|

|

PDF PE613010 Data sheet ( Hoja de datos )

| Número de pieza | PE613010 | |

| Descripción | SPST Tuning Control Switch | |

| Fabricantes | Peregrine Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de PE613010 (archivo pdf) en la parte inferior de esta página. Total 8 Páginas | ||

|

No Preview Available !

Product Description

The PE613010 is an SPST tuning control switch based

on Peregrine’s UltraCMOS® technology. This highly

versatile switch supports a wide variety of tuning circuit

topologies with emphasis on impedance matching and

aperture tuning applications. PE613010 features low on-

resistance and insertion loss from 100 to 3000 MHz.

PE613010 offers high RF power handling and

ruggedness, while meeting challenging harmonic and

linearity requirements enabled by Peregrine’s HaRP™

technology. With single-pin low voltage CMOS control,

all decoding and biasing is integrated on-chip and no

external bypassing or filtering components are required.

UltraCMOS tuning devices feature ease of use while

delivering superior RF performance. With built-in bias

voltage generation and ESD protection, tuning control

switches provide a monolithically integrated tuning

solution for demanding RF applications.

Product Specification

PE613010

UltraCMOS® SPST Tuning Control

Switch, 100–3000 MHz

Features

Open reflective architecture

Very low on-resistance of 1.2Ω

Low insertion loss

0.20 dB @ 900 MHz

0.40 dB @ 1900 MHz

High power handling: 38 dBm (50Ω)

Wide power supply range (2.3V to 4.8V)

High ESD tolerance of 2 kV HBM

on all pins

Applications include:

Open and closed-loop tunable

antennas for 2G/3G/4G

Tunable matching networks

Tunable filter networks

Bypassing applications

RFID readers

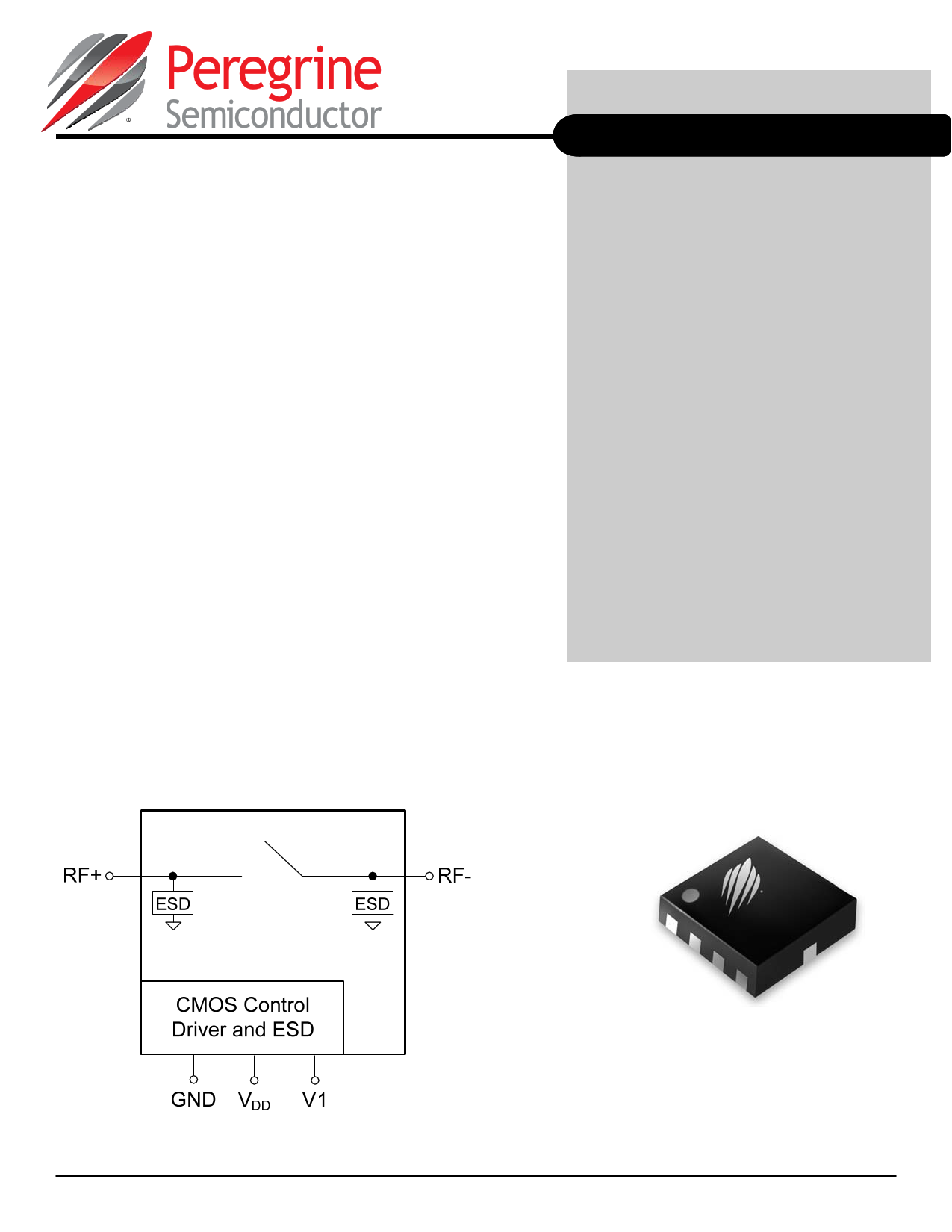

Figure 1. Functional Block Diagram

Figure 2. Package Type

10-lead 2 2 0.55 mm QFN

DOC-11414-5 │ www.psemi.com

DOC-53244

©2013–2014 Peregrine Semiconductor Corp. All rights reserved.

Page 1 of 8

1 page

PE613010

Product Specification

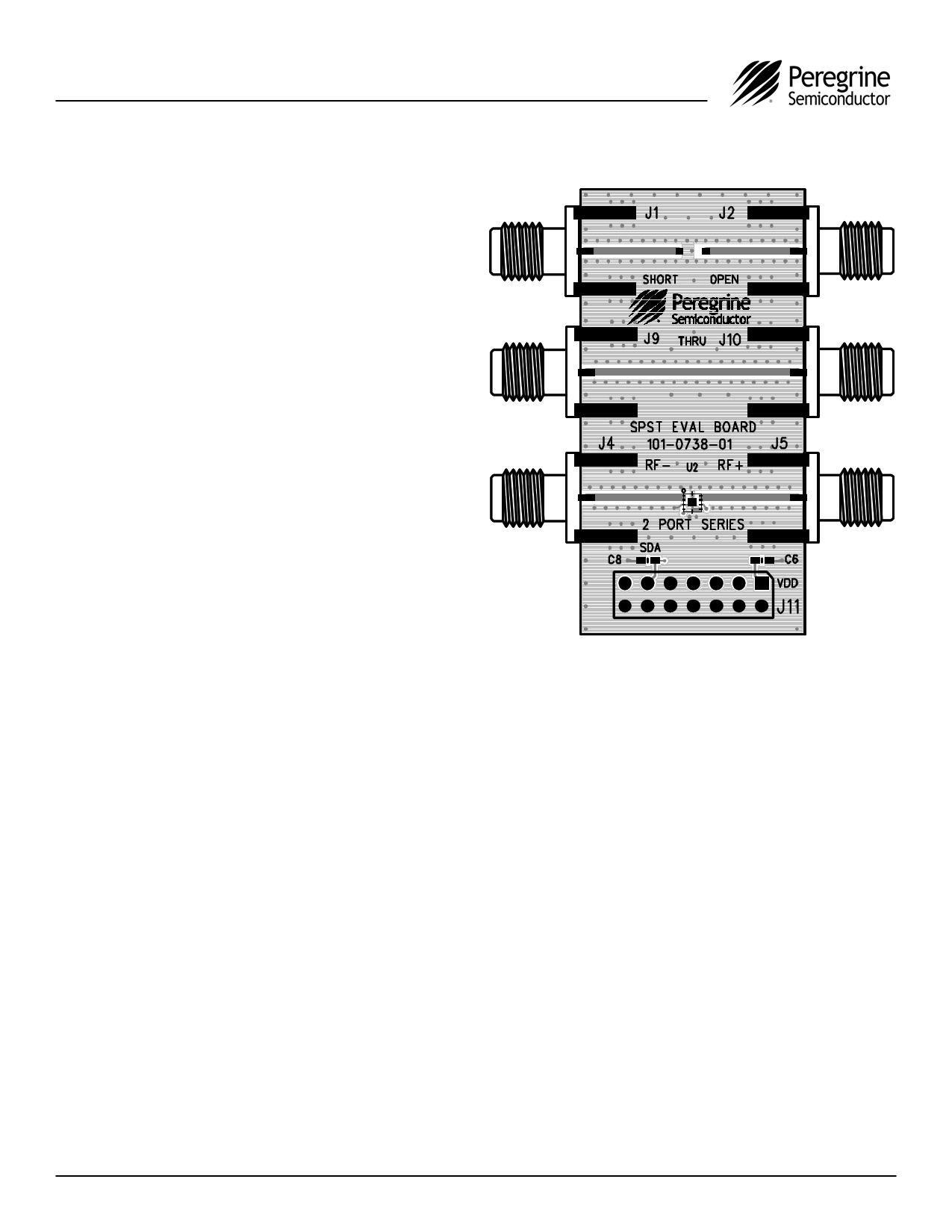

Evaluation Board

The 101-0738 Evaluation Board (EVB) was

designed for accurate measurement of the tuning

switch impedance and loss using 2 Port Series

(J4, J5) configuration. Three calibration standards

are provided. The open (J2) and short (J1)

standards (104 ps delay) are used for performing

port extensions and accounting for electrical length

and transmission line loss. The Thru (J8, J10)

standard can be used to estimate PCB

transmission line loss for scalar de-embedding.

The board consists of a 4 layer stack with

2 outer layers made of Rogers 4350B (εr = 3.48)

and 2 inner layers of FR4 (εr = 4.80). The total

thickness of this board is 62 mils (1.57 mm).

The inner layers provide a ground plane for the

transmission lines. Each transmission line is

designed using a coplanar waveguide with

ground plane (CPWG) model using a trace width

of 32 mils (0.813 mm), gap of 15 mils (0.381 mm),

and a metal thickness of 1.4 mils (0.051 mm).

Figure 5. Evaluation Board

PRT-08405

DOC-11414-5 │ www.psemi.com

©2013–2014 Peregrine Semiconductor Corp. All rights reserved.

Page 5 of 8

5 Page | ||

| Páginas | Total 8 Páginas | |

| PDF Descargar | [ Datasheet PE613010.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| PE613010 | SPST Tuning Control Switch | Peregrine Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |