|

|

PDF P3C1021 Data sheet ( Hoja de datos )

| Número de pieza | P3C1021 | |

| Descripción | STATIC CMOS RAM | |

| Fabricantes | PYRAMID | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de P3C1021 (archivo pdf) en la parte inferior de esta página. Total 10 Páginas | ||

|

No Preview Available !

P3C1021

HIGH SPEED 64K x 16 (1 MEG)

STATIC CMOS RAM

FEATURES

High Speed (Equal Access and Cycle Times)

— 10/12/15/20 ns (Commercial)

— 12/15/20 ns (Industrial)

Low Power

— 325 mW (max.)

Single 3.3V ± 0.3V Power Supply

Easy Memory Expansion Using CE and OE

Inputs

DESCRIPTION

The P3C1021 is a 65,536 words by 16 bits high-speed

CMOS static RAM. The CMOS memory requires no

clocks or refreshing, and has equal access and cycle

times. Inputs are fully TTL-compatible. The RAM oper-

ates from a single 3.3V ± 0.3V tolerance power

supply.

Access times as fast as 10 nanoseconds permit greatly

enhanced system operating speeds. CMOS is utilized

to reduce power consumption to a low level. The P3C1021

is a member of a family of PACE RAM™ products offer-

ing fast access times.

FUNCTIONAL BLOCK DIAGRAM

Fully TTL Compatible Inputs and Outputs

Advanced CMOS Technology

Fast tOE

Automatic Power Down when deselected

Packages

—44-Pin SOJ, TSOP II

The P3C1021 device provides asynchronous operation

with matching access and cycle times. Memory loca-

tions are specified on address pins A0 to A15. Reading is

accomplished by device selection (CE and output en-

abling (OE) while write enable (WE) remains HIGH. By

presenting the address under these conditions, the data

in the addressed memory location is presented on the

data input/output pins. The input/output pins stay in the

HIGH Z state when either CE or OE is HIGH or WE is

LOW.

Package options for the P3C1021 include 44-pin SOJ

and TSOP packages.

PIN CONFIGURATION

1519B

SOJ

TSOPII

Document # SRAM134 REV OR

Revised April 2007

1

1 page

P3C1021

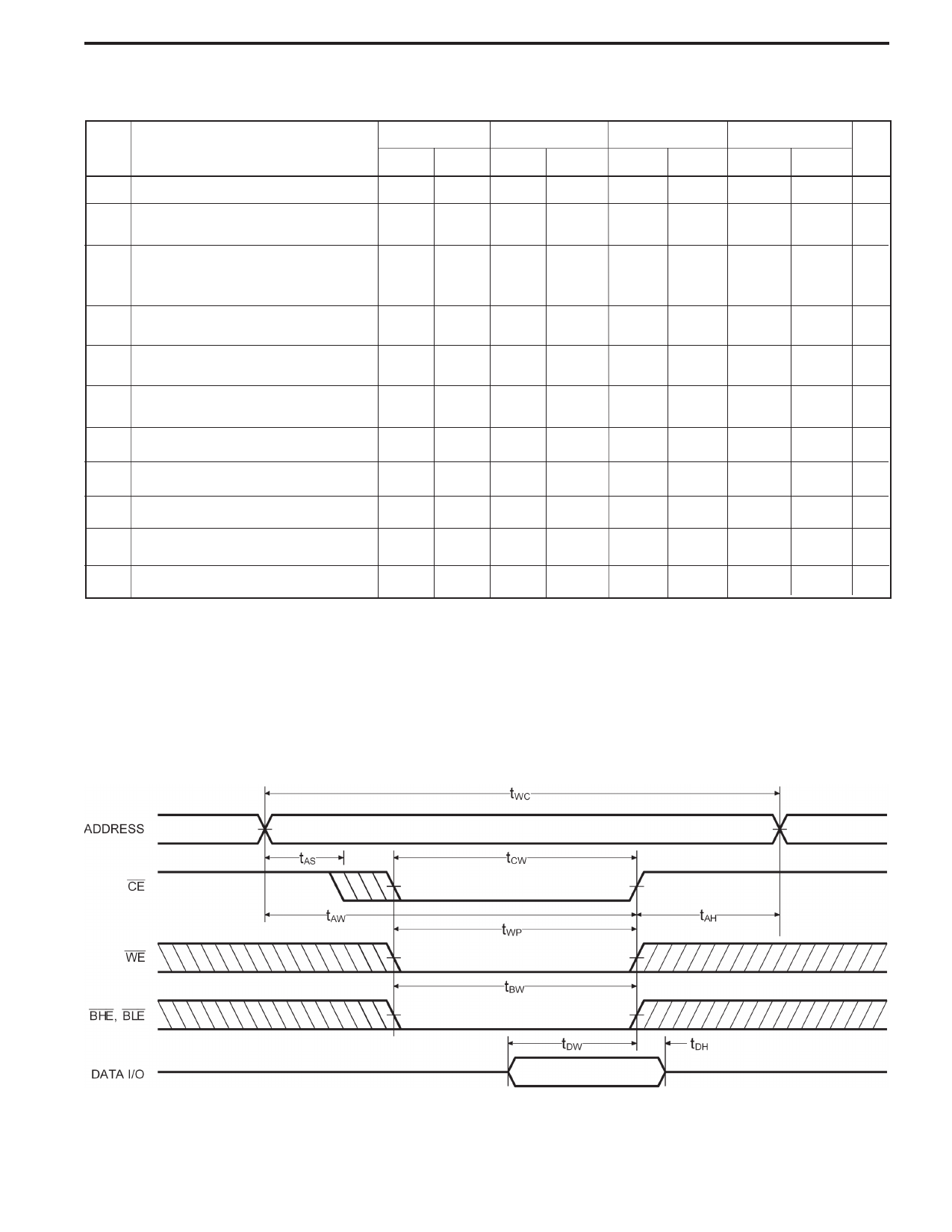

AC CHARACTERISTICS—WRITE CYCLE

(VCC = 3.3V ± 0.3V, All Temperature Ranges)(2)

Sym. Parameter

-10

Min Max

tWC Write Cycle Time

tCW Chip Enable Time to End of

Write

10

8

-12

Min Max

12

9

tAW Address Valid to End of Write

tAS

Address Set-up Time to Write

Start

tWP Write Pulse Width

tAH Address Hold Time

8

0

7

0

9

0

8

0

tDW Data Valid to End of Write

5

tDH Data Hold Time

tWZ Write Enable to Output in High Z

0

5

tLZWE WE High to Low Z

3

tBW Byte Enable to End of Write

7

6

0

6

3

8

-15

Min Max

15

10

10

0

10

0

8

0

7

3

9

-20

Min Max

20

12

Unit

ns

ns

12 ns

0 ns

12 ns

0 ns

10 ns

0 ns

8 ns

3 ns

10 ns

TIMING WAVEFORM OF WRITE CYCLE NO. 1 (CE CONTROLLED)

Document # SRAM134 REV OR

Page 5 of 10

5 Page | ||

| Páginas | Total 10 Páginas | |

| PDF Descargar | [ Datasheet P3C1021.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| P3C1021 | STATIC CMOS RAM | PYRAMID |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |