|

|

PDF WM5102 Data sheet ( Hoja de datos )

| Número de pieza | WM5102 | |

| Descripción | Audio Hub CODEC | |

| Fabricantes | Wolfson Microelectronics | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de WM5102 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

w

WM5102

Audio Hub CODEC with Voice Processor DSP

DESCRIPTION

The WM5102[1] is a highly-integrated low-power audio

system for smartphones, tablets and other portable audio

devices. It combines wideband telephony voice processing

with a flexible, high-performance audio hub CODEC.

The WM5102 digital core provides a powerful combination

of fixed-function signal processing blocks with a

programmable DSP. These are supported by a fully-flexible,

all-digital audio mixing and routing engine with sample rate

converters, for wide use-case flexibility. The programmable

DSP supports a range of audio processing software

packages (supplied separately); user-programmed solutions

can also be supported. Fixed-function signal processing

blocks include filters, EQ, dynamics processors and sample

rate converters.

A SLIMbus interface supports multi-channel audio paths and

host control register access. Multiple sample rates are

supported concurrently via the SLIMbus interface. Three

further digital audio interfaces are provided, each supporting

a wide range of standard audio sample rates and serial

interface formats. Automatic sample rate detection enables

seamless wideband/narrowband voice call handover.

Two stereo headphone drivers each provide stereo ground-

referenced or mono BTL outputs, with noise levels as low as

2.3μVRMS for hi-fi quality line or headphone output. The

CODEC also features stereo 2W Class-D speaker outputs, a

dedicated BTL earpiece output and PDM for external

speaker amplifiers. A signal generator for controlling haptics

devices is included; vibe actuators can connect directly to

the Class-D speaker output, or via an external driver on the

PDM output interface. All inputs, outputs and system

interfaces can function concurrently.

The WM5102 supports up to six microphone inputs, each

either analogue or PDM digital. Microphone activity

detection with interrupt is available. A smart accessory

interface supports most standard 3.5mm accessories.

Impedance sensing and measurement is provided for

external accessory and push-button detection.

The WM5102 power, clocking and output driver

architectures are all designed to maximise battery life in

voice, music and standby modes. Low-power ‘Sleep’ is

supported, with configurable wake-up events. The WM5102

is powered from a 1.8V external supply. A separate supply is

required for the Class D speaker drivers (typically direct

connection to 4.2V battery).

Two integrated FLLs provide support for a wide range of

system clock frequencies. The WM5102 is configured using

the I2C, SPI or SLIMbus interfaces. The fully-differential

internal analogue architecture, minimal analogue signal

paths and on-chip RF noise filters ensure a very high degree

of noise immunity.

FEATURES

Audio hub CODEC with integrated voice processor DSP

Programmable DSP capability for audio processing

Fixed function signal processing functions

- Wind noise, sidetone and other programmable filters

- Dynamic Range Control, Fully parametric EQs

- Tone, Noise, PWM, Haptic control signal generators

Multi-channel asynchronous sample rate conversion

Integrated 6/7 channel 24-bit hi-fi audio hub CODEC

- 6 ADCs, 96dB SNR microphone input (48kHz)

- 7 DACs, 113dB SNR headphone playback (48kHz)

Audio inputs

- Up to 6 analogue or digital microphone inputs

- Single-ended or differential mic/line inputs

Multi-purpose headphone / earpiece / line output drivers

- 2 stereo output paths

- 29mW into 32Ω load at 0.1% THD+N

- 100mW into 32Ω BTL load at 5% THD+N

- 6.5mW typical headphone playback power consumption

- Pop suppression functions

- 2.3µVRMS noise floor (A-weighted)

Mono BTL earpiece output driver

2 x 2W stereo Class D speaker output drivers

- Direct drive of external haptics vibe actuators

Two-channel digital speaker (PDM) interface

SLIMbus® audio and control interface

3 full digital audio interfaces

- Standard sample rates from 4kHz up to 192kHz

- Ultrasonic accessory function support

- TDM support on all AIFs

- 8 channel input and output on AIF1

Flexible clocking, derived from MCLKn, BCLKn or SLIMbus

2 low-power FLLs support reference clocks down to 32kHz

Advanced accessory detection functions

- Low-power standby mode and configurable wake-up

Configurable functions on 5 GPIO pins

Integrated LDO regulators and charge pumps

Support for single 1.8V supply operation

Small W-CSP package, 0.4mm pitch

APPLICATIONS

Smartphones and Multimedia handsets

Tablets and Mobile Internet Devices (MID)

General-purpose low-power audio CODEC hub

WOLFSON MICROELECTRONICS plc

Production Data, June 2014, Rev 4.2

[1] This product is protected by Patents US 7,622,984, US 7,626,445, US 7,765,019 and GB 2,432,765

Copyright 2014 Wolfson Microelectronics plc

1 page

Production Data

WM5102

EXTERNAL ACCESSORY DETECTION ................................................................................ 177

JACK DETECT ............................................................................................................................................................................177

JACK POP SUPPRESSION (MICDET CLAMP)..........................................................................................................................179

MICROPHONE DETECT.............................................................................................................................................................180

HEADPHONE DETECT...............................................................................................................................................................185

LOW POWER SLEEP CONFIGURATION .............................................................................. 189

SLEEP MODE..............................................................................................................................................................................189

SLEEP CONTROL SIGNALS - JD1, GP5, MICDET CLAMP ......................................................................................................192

WAKE-UP TRANSITION .............................................................................................................................................................194

WRITE SEQUENCE CONTROL..................................................................................................................................................195

INTERRUPT CONTROL..............................................................................................................................................................195

GENERAL PURPOSE INPUT / OUTPUT ............................................................................... 196

GPIO CONTROL .........................................................................................................................................................................197

GPIO FUNCTION SELECT .........................................................................................................................................................199

DIGITAL AUDIO INTERFACE FUNCTION (AIFNTXLRCLK) ......................................................................................................202

BUTTON DETECT (GPIO INPUT)...............................................................................................................................................203

LOGIC ‘1’ AND LOGIC ‘0’ OUTPUT (GPIO OUTPUT) ................................................................................................................203

INTERRUPT (IRQ) STATUS OUTPUT........................................................................................................................................203

DSP STATUS FLAG (DSP IRQN) OUTPUT ...............................................................................................................................204

OPCLK AND OPCLK_ASYNC CLOCK OUTPUT .......................................................................................................................204

FREQUENCY LOCKED LOOP (FLL) STATUS OUTPUT ...........................................................................................................205

FREQUENCY LOCKED LOOP (FLL) CLOCK OUTPUT .............................................................................................................206

PULSE WIDTH MODULATION (PWM) SIGNAL OUTPUT .........................................................................................................206

HEADPHONE DETECTION STATUS OUTPUT .........................................................................................................................207

MICROPHONE / ACCESSORY DETECTION STATUS OUTPUT ..............................................................................................207

ASYNCHRONOUS SAMPLE RATE CONVERTER (ASRC) LOCK STATUS OUTPUT .............................................................207

ASYNCHRONOUS SAMPLE RATE CONVERTER (ASRC) CONFIGURATION ERROR STATUS OUTPUT ...........................208

OVER-TEMPERATURE STATUS OUTPUT ...............................................................................................................................208

DYNAMIC RANGE CONTROL (DRC) STATUS OUTPUT ..........................................................................................................208

CONTROL WRITE SEQUENCER STATUS OUTPUT ................................................................................................................209

CONTROL INTERFACE ERROR STATUS OUTPUT .................................................................................................................209

SYSTEM CLOCKS ENABLE STATUS OUTPUT ........................................................................................................................209

CLOCKING ERROR STATUS OUTPUT .....................................................................................................................................210

DIGITAL AUDIO INTERFACE CONFIGURATION ERROR STATUS OUTPUT .........................................................................211

INTERRUPTS .......................................................................................................................... 212

CLOCKING AND SAMPLE RATES ......................................................................................... 224

SYSTEM CLOCKING ..................................................................................................................................................................224

SAMPLE RATE CONTROL .........................................................................................................................................................225

AUTOMATIC SAMPLE RATE DETECTION................................................................................................................................226

SYSCLK AND ASYNCCLK CONTROL .......................................................................................................................................226

MISCELLANEOUS CLOCK CONTROLS ....................................................................................................................................229

BCLK AND LRCLK CONTROL....................................................................................................................................................236

CONTROL INTERFACE CLOCKING ..........................................................................................................................................236

FREQUENCY LOCKED LOOP (FLL) ..........................................................................................................................................237

FREE-RUNNING FLL MODE ......................................................................................................................................................247

SPREAD SPECTRUM FLL CONTROL .......................................................................................................................................248

GPIO OUTPUTS FROM FLL .......................................................................................................................................................249

EXAMPLE FLL CALCULATION...................................................................................................................................................249

EXAMPLE FLL SETTINGS..........................................................................................................................................................250

CONTROL INTERFACE .......................................................................................................... 251

2-WIRE (I2C) CONTROL MODE .................................................................................................................................................252

4-WIRE (SPI) CONTROL MODE.................................................................................................................................................256

CONTROL WRITE SEQUENCER ........................................................................................... 257

INITIATING A SEQUENCE..........................................................................................................................................................257

AUTOMATIC SAMPLE RATE DETECTION SEQUENCES ........................................................................................................258

JACK DETECT, GPIO, MICDET CLAMP, AND WAKE-UP SEQUENCES .................................................................................259

w

PD, June 2014, Rev 4.2

5

5 Page

Production Data

WM5102

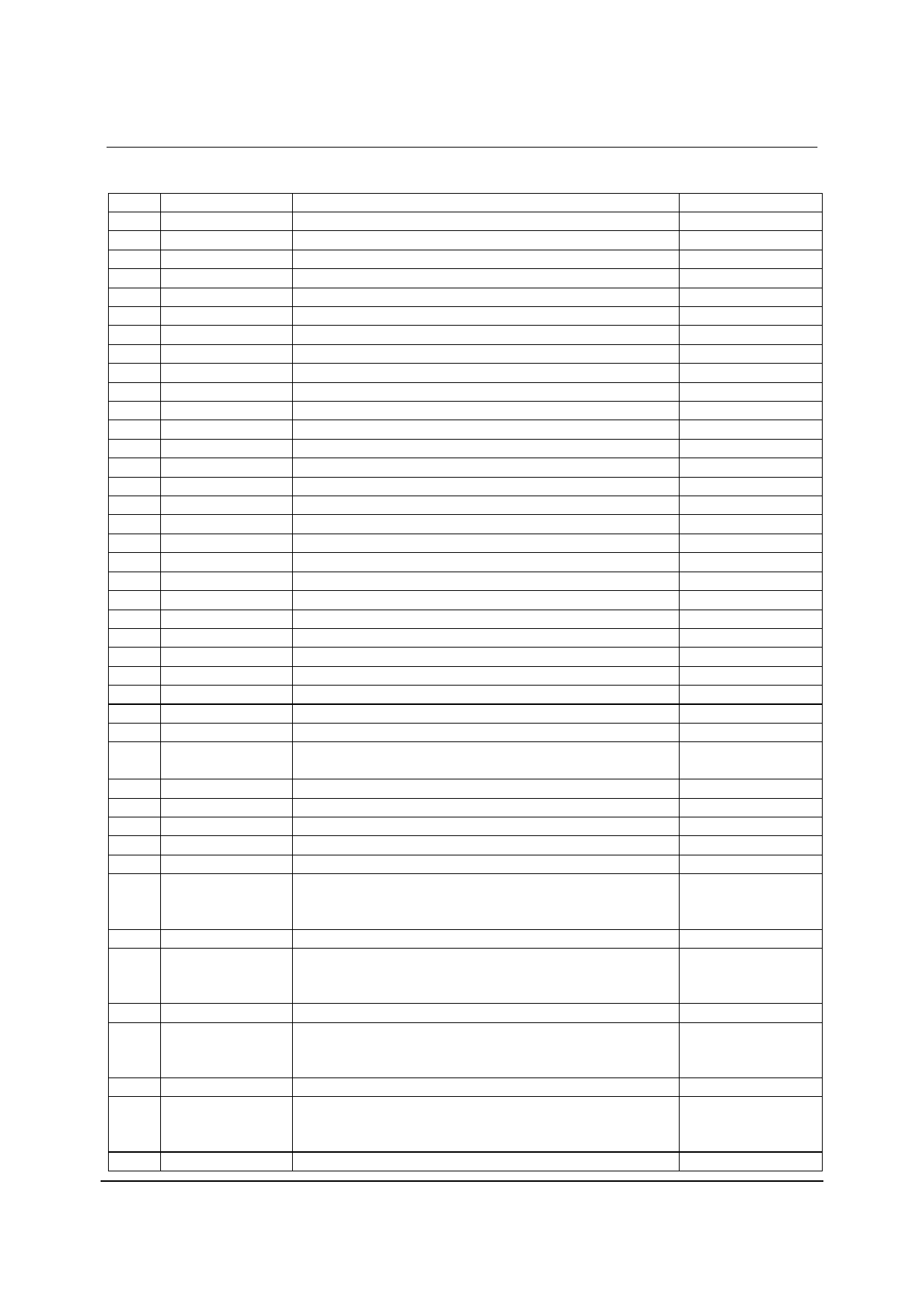

The following table identifies the power domain and ground reference associated with each of the input / output pins.

PIN NO

J13

J11

J12

J8

K5

M9

L8

L6

L5

K4

M5

L4

L13

K12

K11

M13

K9

L12

L11

A4

A5

K13

L7

K3

K10

G10

B12

A12

A13

B8

A8

B6

A6

B5

E3

NAME

AIF1BCLK

AIF1RXDAT

AIF1LRCLK

AIF1TXDAT

AIF2BCLK

AIF2RXDAT

AIF2LRCLK

AIF2TXDAT

AIF3BCLK

AIF3RXDAT

AIF3LRCLK

AIF3TXDAT

CIF1ADDR

CIF1SCLK

CIF1SDA

CIF2MOSI

CIF2MISO

CIF2SCLK

C¯¯IF¯2¯S¯S¯

EPOUTP

EPOUTN

GPIO1

GPIO2

GPIO3

GPIO4

GPIO5

HPDETL

HPDETR

HPOUT1FB1/

MICDET2

HPOUT1L

HPOUT1R

HPOUT2FB

HPOUT2L

HPOUT2R

IN1LN/

DMICCLK1

D3 IN1LP

E1 IN1RN/

DMICDAT1

E2 IN1RP

C1 IN2LN/

DMICCLK2

C2 IN2LP

D1 IN2RN/

DMICDAT2

D2 IN2RP

w

POWER DOMAIN

DBVDD1

DBVDD1

DBVDD1

DBVDD1

DBVDD2

DBVDD2

DBVDD2

DBVDD2

DBVDD3

DBVDD3

DBVDD3

DBVDD3

DBVDD1

DBVDD1

DBVDD1

DBVDD1

DBVDD1

DBVDD1

DBVDD1

CPVDD

CPVDD

DBVDD1

DBVDD2

DBVDD3

DBVDD1

DBVDD1

AVDD

AVDD

CPVDD (Ground noise rejection) /

MICVDD (Microphone / Accessory detection)

CPVDD

CPVDD

CPVDD

CPVDD

CPVDD

MICVDD (analogue) /

MICVDD, MICBIAS1, MICBIAS2, MICBIAS3 (digital)

The DMICCLK1 power domain is selectable using IN1_DMIC_SUP

AVDD

MICVDD (analogue) /

MICVDD, MICBIAS1, MICBIAS2, MICBIAS3 (digital)

The DMICDAT1 power domain is selectable using IN1_DMIC_SUP

AVDD

MICVDD (analogue) /

MICVDD, MICBIAS1, MICBIAS2, MICBIAS3 (digital)

The DMICCLK2 power domain is selectable using IN2_DMIC_SUP

AVDD

MICVDD (analogue) /

MICVDD, MICBIAS1, MICBIAS2, MICBIAS3 (digital)

The DMICDAT2 power domain is selectable using IN2_DMIC_SUP

AVDD

GROUND DOMAIN

DGND

DGND

DGND

DGND

DGND

DGND

DGND

DGND

DGND

DGND

DGND

DGND

DGND

DGND

DGND

DGND

DGND

DGND

DGND

AGND

AGND

DGND

DGND

DGND

DGND

DGND

AGND

AGND

AGND

AGND

AGND

AGND

AGND

AGND

AGND

AGND

AGND

AGND

AGND

AGND

AGND

AGND

PD, June 2014, Rev 4.2

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet WM5102.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| WM5100 | Low Power Audio System | Wolfson Microelectronics |

| WM5102 | Audio Hub CODEC | Wolfson Microelectronics |

| WM5102S | Audio Hub CODEC | Wolfson Microelectronics |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |