|

|

PDF ACPL-302J-000E Data sheet ( Hoja de datos )

| Número de pieza | ACPL-302J-000E | |

| Descripción | 2.5 Amp Gate Drive Optocoupler | |

| Fabricantes | AVAGO | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ACPL-302J-000E (archivo pdf) en la parte inferior de esta página. Total 18 Páginas | ||

|

No Preview Available !

ACPL-302J

2.5 Amp Gate Drive Optocoupler with Integrated Flyback Controller

for Isolated DC-DC Converter, IGBT DESAT Detection,

Active Miller Clamping, FAULT and UVLO Status Feedback

Data Sheet

Lead (Pb) Free

RoHS 6 fully

compliant

RoHS 6 fully compliant options available;

-xxxE denotes a lead-free product

Description

Avago's ACPL-302J 2.5 Amp Gate Drive Optocoupler

features integrated flyback controller for isolated DC-DC

converter, IGBT desaturation sensing with fault feedback

and soft-shutdown, Under-Voltage LockOut (UVLO) with

feedback and active Miller current clamping. The fast

propagation delay with excellent timing skew perfor-

mance enables excellent timing control and efficiency.

This full feature optocoupler comes in a compact, surface-

mountable SO-16 package for space-savings, is suitable

for driving IGBTs and power MOSFETs used in motor

control and inverter applications.

Functional Diagram

SW VEE2 VCC2

VCC1

COMP

/UVLO

/FAULT

VEE1

OSC

Logic

Control

S

R

Input Driver

UVLO

Output Driver

Over

Current

AN

CA

SSD Control

Miller Control

Figure 1. ACPL-302J Functional Diagram

LED2+

VE

DESAT

VO

SSD/

CLAMP

VEE2

Features

• Integrated flyback controller for isolated DC-DC

converter

• Regulated Output Voltage: 20 V

• Peak output current: 2.5 A max.

• Miller Clamp Sinking Current: 1.7 A max.

• Wide Input Voltage Range: 8 V to 18 V

• Common-Mode Rejection (CMR): > 30 kV/ms at VCM =

1500 V

• Propagation delay: 250 ns max.

• Integrated fail-safe IGBT protection

– Desat detection, “Soft” IGBT turn-off and Fault

Feedback

– Under Voltage Lock-Out (UVLO) protection with

Feedback

• High Noise Immunity

– Miller Current Clamping

– Direct LED input with low input impedance and low

noise sensitivity

– Negative Gate Bias

• SO-16 package with 8 mm clearance and creepage

• Regulatory approvals:

– UL 1577, CSA

– IEC/EN/DIN EN 60747-5-5

Applications

• Isolated IGBT/MOSFET Inverter gate drive

• Renewable energy inverters

• AC and brushless DC motor drives

• Industrial inverters

• Uninterruptible Power Supplies (UPS)

CAUTION: It is advised that normal static precautions be taken in handling and assembly

of this component to prevent damage and/or degradation, which may be induced by ESD.

1 page

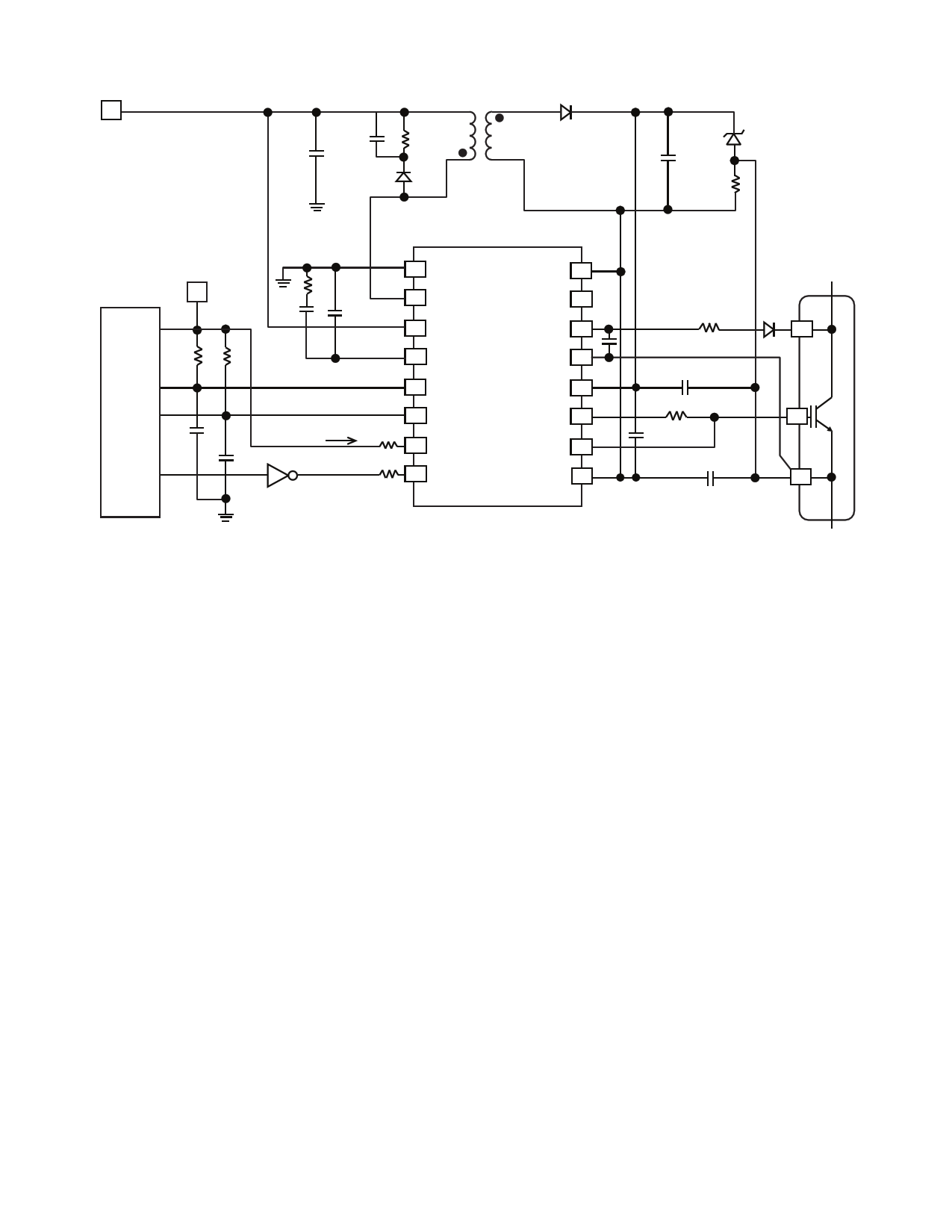

Vin = 8 V - 18 V

220 nF

2 kΩ Lp

Ls

10 µF

1 kΩ

+ 5V

470kΩ

22 nF

10kΩ

10kΩ

µC

330 pF

330 pF

330 pF

IF 130Ω

130Ω

VEE1

SW

VCC1

COMP

/UVLO

/FAULT

AN

CA

VEE2

LED2+

DESAT

VE

VCC2

VO

SSD/CLAMP

VEE2

ACPL-302J

Figure 3. Typical gate drive circuits with Desat current sensing using ACPL-302J

Note. Component value subject to change with varying application requirements

220 pF

1 kΩ

10 µF

10Ω VGATE

0.1 µF

10 µF

C

G

E

Operation of Integrated Flyback Controller

The primary control block implements direct duty cycle

control logics for line and load regulation. Primary winding

currents are sensed and limited to prevent transformer

short circuit failure from damaging the primary switch.

Secondary output voltage VCC2 is also sensed and fed back

to the primary control circuits. VCC2 over voltage can be

detected and the primary switch is turned off to protect

secondary overvoltage failure. The maximum PWM duty

cycle is designed to be around 55% to ensure discontinu-

ous operation mode under a high load condition. For a

complete isolated DC-DC converter, connect a discrete

transformer to ACPL-302J, as in Figure 3. Keep the LED

off when you are powering up VCC1. To ensure proper

operation of the DC-DC converter, a fast VCC1 rise time (≤

5 ms) is preferred for a soft start function to control the

inrush current.

The average PWM switching frequency of the primary

switch (SW) is dithered typically in a range of ±6%. This

frequency dithering feature helps to achieve better

EMI performance by spreading the switching and its

harmonics over a wider band.

Reference DC/DC circuit

Figure 3 shows a reference circuit for DC/DC flyback con-

version including the compensation network at pin 4,

COMP.

This compensation network is referenced to a nominal

transformer of Lp = 60 µH, Ls=260 µH.

For VCC1 = 8 V to 18 V, this circuit will nominally support a

secondary-side load of up to 60 mA (including ICC2) at the

regulated VCC2 voltage. For VCC1 = 6 V to 8V, the supported

load will be up to 40 mA.

Users must further characterize the DC/DC flyback con-

version across their target operating conditions and

chosen components to ensure that the required load can

be supported.

5

5 Page

Electrical Specifications (continued)

Unless otherwise specified, all Minimum/Maximum specifications are at recommended operating conditions, all

voltages at input IC are referenced to VEE1, all voltages at output IC referenced to VEE2. All typical values at TA = 25 °C,

VCC1 = 12 V, VCC2-VEE2 = 20 V, VE-VEE2 = 0 V.

Parameter

Gate Driver

Symbol Min

Typ

Max Units Test Conditions

Fig. Note

High Level Output Current

Low Level Output Current

High Level Output Voltage

Low Level Output Voltage

Vsource to High Level Output

Propagation Delay Time

Vsource to Low Level Output

Propagation Delay Time

Pulse Width Distortion

IOH

IOL

VOH

VOL

tPLH

tPHL

PWD

1.0

VCC2–0.5

50

-1.9

2.3

VCC2–0.15

0.1

120

-0.75

0.5

250

A

A

V

V

ns

50 160 250 ns

-40 40

140 ns

VO = VCC2 - 3 V

VO = VEE2 + 2.5 V

IO = -100 mA

IO = 100 mA

Vsource = 5 V

Rf = 260 Ω, Rg = 10 Ω

Cload = 10 nF

f = 10 kHz

Duty Cycle = 50%

15

16

17,22

17,22

4

4

8,9,10

11

12

13,14

Dead Time Distortion

(tPLH-tPHL)

DTD -160 -40

10% to 90% Rise Time

tR

70

90% to 10% Fall Time

tF

35

Output High Level Common

Mode Transient Immunity

|CMH|

30

>50

Output Low Level Common Mode |CML|

Transient Immunity

30

>50

Active Miller Clamp and Soft Shutdown

60 ns

14,15

ns

ns

kV/μs

kV/μs

TA=25 °C, IF = 10 mA,

VCM =1500 V

TA = 25 °C, IF = 0 mA,

VCM=1500 V

23

24

16

17

Low Level Soft Shutdown

ISSD 22 35

Current During Fault Condition

55

mA VSSD – VEE2 = 14 V

18

Clamp Threshold Voltage

VTH_CLAMP

Clamp Low Level Sinking

Current

ICLAMP

0.5

VCC2 UVLO Protection (UVLO voltage VUVLO reference to VE)

VCC2 UVLO Threshold Low to High VUVLO+

10.9

VCC2 UVLO Threshold High to Low VUVLO-

10.0

VCC2 UVLO Hysteresis

VUVLO_HYS

VCC2 to UVLO High Delay

tPLH_UVLO

VCC2 to UVLO Low Delay

tPHL_UVLO

VCC2 UVLO to VOUT High Delay

tUVLO_ON

VCC2 UVLO to VOUT Low Delay

tUVLO_OFF

Continued on next page...

2.0

2.0

12.5

11.3

1.2

15

10.7

5.3

1.1

3.0 V

A

VCLAMP = VEE2 + 2.5 V

13.8 V

12.8 V

V

µs

µs

µs

µs

VO > 5 V

VO < 5 V

10,18

10,19

10

20

21

22

23

11

11 Page | ||

| Páginas | Total 18 Páginas | |

| PDF Descargar | [ Datasheet ACPL-302J-000E.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ACPL-302J-000E | 2.5 Amp Gate Drive Optocoupler | AVAGO |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |