|

|

PDF ADM5120 Data sheet ( Hoja de datos )

| Número de pieza | ADM5120 | |

| Descripción | Home Gateway Controller | |

| Fabricantes | ADMtek | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ADM5120 (archivo pdf) en la parte inferior de esta página. Total 70 Páginas | ||

|

No Preview Available !

ADM5120

HOME GATEWAY CONTROLLER

Datasheet

Version 1.14

ADMtek.com.tw

Information in this document is provided in connection with ADMtek products. ADMtek may make

changes to specifications and product descriptions at any time, without notice. Designers must not rely on

the absence or characteristics of any features or instructions marked “reserved” or “undefined”. ADMtek

reserves these for future definition and shall have no responsibility whatsoever for conflicts or

incompatibilities arising from future changes to them

The products may contain design defects or errors known as errata, which may cause the product to deviate

from published specifications. Current characterized errata are available on request. To obtain the latest

documentation please contact you local ADMtek sales office or visit ADMtek’s website at

http://www.admtek.com.tw

*Third-party brands and names are the property of their respective owners.

Copyright 2003 by ADMtek Incorporated All Rights Reserved.

http://www.Datasheet4U.com

1 page

ADMtek Inc.

3.2.6 Stream Cipher Scrambler/ De-scrambler ................................................ 3-3

3.2.7 Encoder/Decoder ..................................................................................... 3-3

3.3 SWITCH ENGINE.................................................................................................... 3-4

3.3.1 Hashing Function..................................................................................... 3-4

3.3.2 Learning Process ..................................................................................... 3-4

3.3.3 Routing..................................................................................................... 3-4

3.3.4 Forwarding .............................................................................................. 3-4

3.3.5 Buffer Management.................................................................................. 3-5

3.3.6 Flow Control (Patent Pending) ............................................................... 3-5

3.3.7 Full Duplex .............................................................................................. 3-5

3.3.8 Half Duplex.............................................................................................. 3-5

3.3.9 Packet priority and Class of Service (CoS) ............................................. 3-5

3.3.10 VLAN........................................................................................................ 3-6

3.3.11 Address table access ................................................................................ 3-6

3.3.12 Address security ....................................................................................... 3-6

3.3.13 Bandwidth control function...................................................................... 3-7

3.3.14 Send descriptors content .......................................................................... 3-7

3.3.15 Receive descriptors content ..................................................................... 3-8

3.4 USB 1.1 HOST CONTROLLER.............................................................................. 3-10

3.4.1 Block Diagram ....................................................................................... 3-10

3.4.2 System bus interface............................................................................... 3-10

3.4.3 Operational Register.............................................................................. 3-10

3.4.4 SIE.......................................................................................................... 3-11

3.4.5 DPLL...................................................................................................... 3-11

3.4.6 Memory BIST ......................................................................................... 3-11

3.5 DMA OPERATION............................................................................................... 3-11

3.5.1 Endpoint Descriptor Format.................................................................. 3-11

3.5.2 Transfer Descriptor Format .................................................................. 3-12

3.5.3 DMA operation ...................................................................................... 3-14

CHAPTER 4 REGISTER DESCRIPTION ................................................................ 4-1

4.1 SYSTEM MEMORY MAP ........................................................................................ 4-1

4.2 SYSTEM AND INTERRUPT REGISTERS .................................................................... 4-1

4.2.1 Interrupt Control Register Map ............................................................... 4-1

4.2.2. Interrupt Request Source Description ..................................................... 4-1

4.2.3 IRQ_status, offset: 0x00........................................................................... 4-1

4.2.4 IRQ_raw_status, offset: 0x40................................................................... 4-2

4.2.5 IRQ_enable, offset: 0x80 ......................................................................... 4-2

4.2.6 IRQ_enable_clear, offset: 0xc0 ............................................................... 4-2

4.2.7 Reserved, offset: 0x10 .............................................................................. 4-2

4.2.8 INT_Mode, offset: 0x14 ........................................................................... 4-2

4.2.9 FIQ_status, offset: 0x18........................................................................... 4-3

4.2.10 IRQ_test_source, offset: 0x1c .................................................................. 4-3

4.2.11 IRQ_source_sel, offset: 0x20 ................................................................... 4-3

4.2.12 INT_level, offset: 0x24 ............................................................................. 4-3

4.3 SWITCH CONTROL REGISTER MAP........................................................................ 4-4

4.4 SWITCH CONTROL REGISTER DESCRIPTION .......................................................... 4-5

ADM5120

V1.14

ii

5 Page

ADM5120

Product Overview

Chapter 1 Product Overview

1.1 Overview

ADM5120 is a high performance, highly integrated, and highly flexible SOC (System-

On-Chip) that facilitates the functionalities of SOHO/SME Gateway, NAT Router, Print

Server, WLAN Access Point and VPN Gateway. ADM5120 enables the sharing of IP-

based broadband services throughout the home/office using wired/wireless computers,

entertainment equipment, printers, and other intelligent devices.

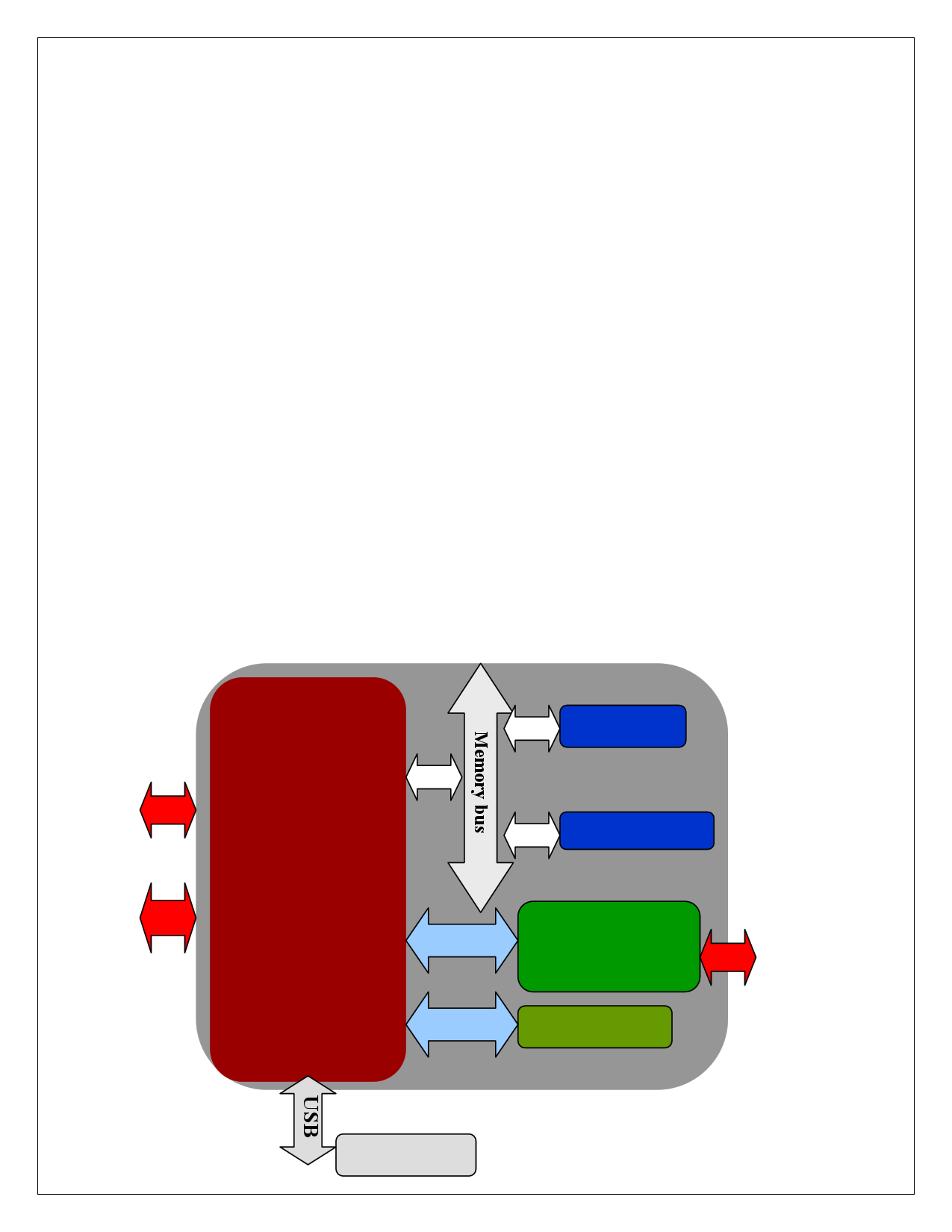

Internally, the ADM5120 ASIC consists of a high performance (227 MIPS) embedded

MIPS CPU, an embedded switch engine, 10/100M PHY, an embedded PCI bridge, an

embedded USB host, and interfaces for UART, SDRAM and Flash. The following

diagram illustrates a system configuration that uses the supported functionalities/facilities

of ADM5120.

1.1.1

Product Order Information

The ADM5120 comes in two packaging formats as follows:

Section 6.1 Ball Grid Array (BGA) 324-pin

Section 6.2 Plastic Quad Flat Pack (PQFP) 208-pin

TTo WAN ADM5120

MIPS +

Switch +

10/100M-PHY

To LAN

X4

PCI

PCI

.

ADMtek Inc.

Printer

SDRAM

NAND Flash

WLAN

802.11a/b/g

NIC

Others

1-1

11 Page | ||

| Páginas | Total 70 Páginas | |

| PDF Descargar | [ Datasheet ADM5120.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ADM5120 | Network Processor | Infineon |

| ADM5120 | Home Gateway Controller | ADMtek |

| ADM5120P | Network Processor | Infineon |

| ADM5120PX | Network Processor | Infineon |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |