|

|

PDF ADRF6755 Data sheet ( Hoja de datos )

| Número de pieza | ADRF6755 | |

| Descripción | 100 MHz to 2400 MHz I/Q Modulator | |

| Fabricantes | Analog Devices | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ADRF6755 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

Data Sheet

100 MHz to 2400 MHz I/Q Modulator

with Integrated Fractional-N PLL and VCO

ADRF6755

FEATURES

I/Q modulator with integrated fractional-N PLL and VCO

Gain control span: 47 dB in 1 dB steps

Output frequency range: 100 MHz to 2400 MHz

Output 1 dB compression: 8 dBm at LO = 1800 MHz

Output IP3: 20.5 dBm at LO = 1800 MHz

Noise floor: −161 dBm/Hz at LO = 1800 MHz

Baseband modulation bandwidth: 600 MHz (3 dB)

Output frequency resolution: 1 Hz

SPI and I2C-compatible serial interfaces

Power supply: 5 V/380 mA

GENERAL DESCRIPTION

The ADRF6755 is a highly integrated quadrature modulator,

frequency synthesizer, and programmable attenuator. The device

covers an operating frequency range from 100 MHz to 2400 MHz

for use in satellite, cellular, and broadband communications.

The ADRF6755 modulator includes a high modulus, fractional-N

frequency synthesizer with integrated VCO, providing less than

1 Hz frequency resolution, and a 47 dB digitally controlled output

attenuator with 1 dB steps.

Control of all the on-chip registers is through a user-selected SPI

interface or I2C interface. The device operates from a single power

supply ranging from 4.75 V to 5.25 V.

REGOUT

VREG1

VREG2

VREG3

VREG4

VREG5

VREG6

RFOUT

VCC1 VCC2 VCC3 VCC4

3.3V

REGULATOR

47dB

GAINCONTROL

RANGE

0°/90° RFDIVIDER

TXDIS

VCO

CORE

LOMON LOMON

REFIN

REFIN

SDI/SDA

CLK/SCL

SDO

CS

×2

DOUBLER

SPI/I2C

INTERFACE

ADRF6755

5-BIT

DIVIDER

÷2 + PHASE

FREQUENCY

– DETECTOR

THIRD-ORDER

FRACTIONAL

INTERPOLATOR

N-COUNTER

FRACTIONAL MODULUS

REGISTER

225

INTEGER

REGISTER

AGND

DGND

Figure 1.

REFERENCE

CHARGE

PUMP

CURRENT SETTING

CR9[7:4]

IBB

IBB

CCOMP1

CCOMP2

CCOMP3

VTUNE

QBB

QBB

RSET

CP

NC

NC

LDET

Rev. B

Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibilityisassumedbyAnalogDevices for itsuse,nor foranyinfringementsofpatentsor other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarksandregisteredtrademarksarethepropertyoftheirrespectiveowners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 ©2012–2013 Analog Devices, Inc. All rights reserved.

Technical Support

www.analog.com

Free Datasheet http://www.datasheet4u.com/

1 page

Data Sheet

Parameter

Noise Floor

Baseband Harmonics

Synthesizer Spurs

Phase Noise

Integrated Phase Noise

RF OUTPUT = 1875 MHz

Nominal Output Power

Gain Flatness

Output P1dB

Output IP3

Output Return Loss

LO Carrier Feedthrough1

2× LO Carrier Feedthrough

Sideband Suppression

Noise Floor

Baseband Harmonics

Synthesizer Spurs

Phase Noise

Integrated Phase Noise

RF OUTPUT = 2100 MHz

Nominal Output Power

Gain Flatness

Output P1dB

Output IP3

Output Return Loss

LO Carrier Feedthrough1

2× LO Carrier Feedthrough

Sideband Suppression

Noise Floor

Baseband Harmonics

Synthesizer Spurs

Test Conditions/Comments

I/Q inputs = 0 V p-p differential, attenuator setting = 0 dB

Attenuator setting = 0 dB to 21 dB, carrier offset = 10 MHz

Attenuator setting = 21 dB to 47 dB, carrier offset = 10 MHz

Min

Integer boundary < loop bandwidth

>10 MHz offset from carrier

100 Hz offset

1 kHz offset

10 kHz offset

100 kHz offset

1 MHz offset

10 MHz offset

1 kHz to 8 MHz integration bandwidth

RFOUT pin

VIQ = 0.9 V p-p differential

Any 40 MHz

f1BB = 3.5 MHz, f2BB = 4.5 MHz, POUT = −6 dBm per tone

Attenuator setting = 0 dB

Attenuator setting = 0 dB to 47 dB

Attenuator setting = 0 dB to 47 dB

I/Q inputs = 0 V p-p differential, attenuator setting = 0 dB

Attenuator setting = 0 dB to 21 dB, carrier offset = 10 MHz

Attenuator setting = 21 dB to 47 dB, carrier offset = 10 MHz

Integer boundary < loop bandwidth

>10 MHz offset from carrier

100 Hz offset

1 kHz offset

10 kHz offset

100 kHz offset

1 MHz offset

10 MHz offset

1 kHz to 8 MHz integration bandwidth

RFOUT pin

VIQ = 0.9 V p-p differential

Any 40 MHz

f1BB = 3.5 MHz, f2BB = 4.5 MHz, POUT = −6 dBm per tone

Attenuator setting = 0 dB

Attenuator setting = 0 dB to 47 dB

Attenuator setting = 0 dB to 47 dB

I/Q inputs = 0 V p-p differential, attenuator setting = 0 dB

Attenuator setting = 0 dB to 21 dB, carrier offset = 10 MHz

Attenuator setting = 21 dB to 47 dB, carrier offset = 10 MHz

Integer boundary < loop bandwidth

>10 MHz offset from carrier

Typ

−161

−150

−170

−58

−60

−75

−89

−99

−103

−108

−133

−152

0.17

−0.6

±0.5

7.8

20.2

−13

−45

−52

−50

−160

−150

−170

−60

−60

−73

−89

−97

−103

−108

−133

−152

0.18

−1.0

±0.5

7.4

19.5

−12

−44

−51

−45

−161

−149

−170

−60

−60

−67

ADRF6755

Max Unit

dBm/Hz

dBc/Hz

dBm/Hz

dBc

dBc

dBc

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

° rms

dBm

dB

dBm

dBm

dB

dBc

dBm

dBc

dBm/Hz

dBc/Hz

dBm/Hz

dBc

dBc

dBc

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

° rms

dBm

dB

dBm

dBm

dB

dBc

dBm

dBc

dBm/Hz

dBc/Hz

dBm/Hz

dBc

dBc

dBc

Rev. B | Page 5 of 48

Free Datasheet http://www.datasheet4u.com/

5 Page

Data Sheet

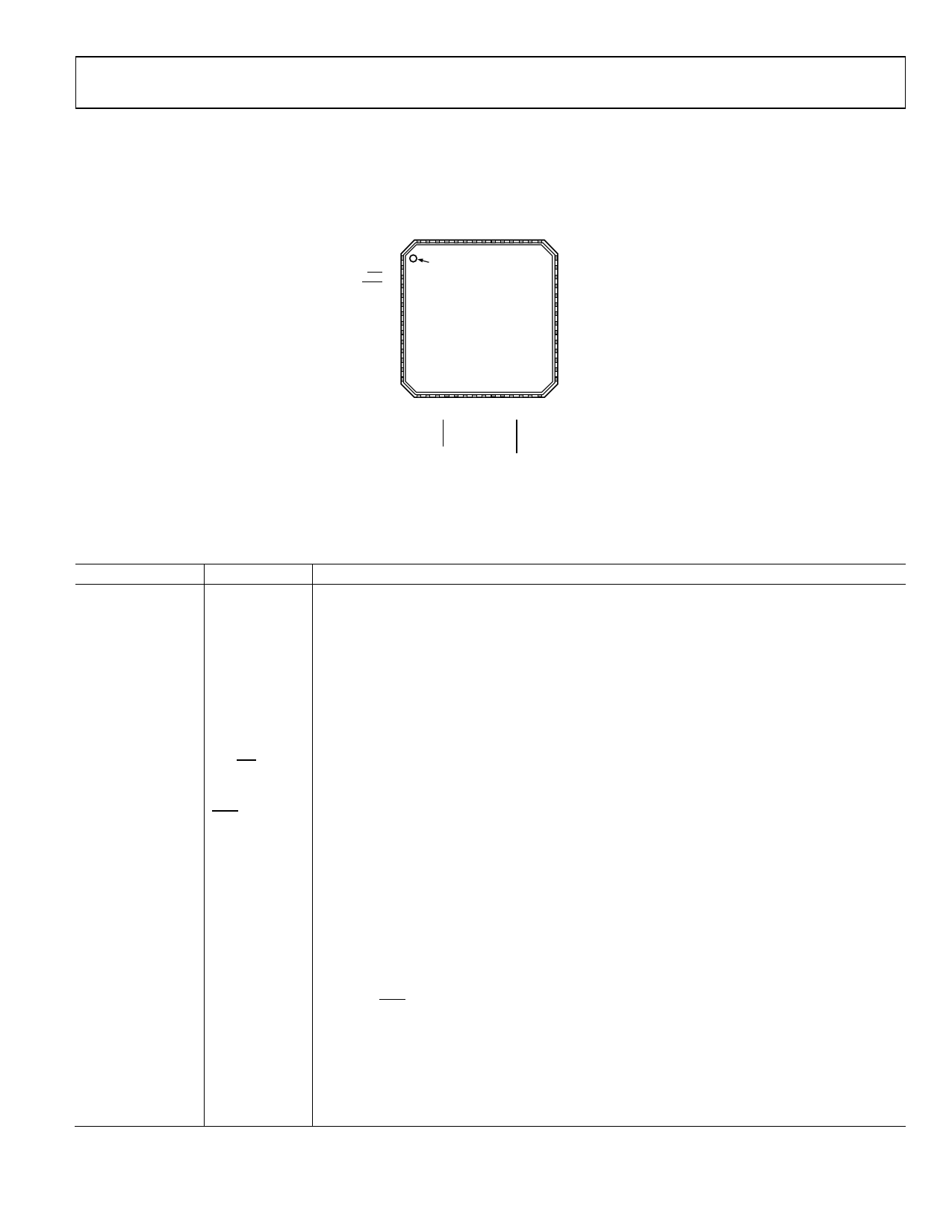

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

ADRF6755

VCC4 1

IBB 2

IBB 3

QBB 4

QBB 5

AGND 6

RSET 7

NC 8

CP 9

NC 10

VCC1 11

REGOUT 12

VREG1 13

VREG2 14

PIN 1

INDICATOR

ADRF6755

TOP VIEW

(Not to Scale)

42 VCC3

41 VCC3

40 AGND

39 AGND

38 VTUNE

37 AGND

36 VREG6

35 CCOMP3

34 CCOMP2

33 CCOMP1

32 DGND

31 VREG5

30 CLK/SCL

29 SDI/SDA

NOTES

1. NC = NO CONNECT. DO NOT CONNECT TO THIS PIN.

2. CONNECT EXPOSED PAD TO GROUND PLANE VIA

A LOW IMPEDANCE PATH.

Figure 4. Pin Configuration

Table 5. Pin Function Descriptions

Pin No.

Mnemonic

11, 55, 56, 41, 42, 1 VCC1 to VCC4

12

13, 14, 15, 16, 31,

36

6, 19, 20, 21, 22, 23,

24, 37, 39, 40, 46, 47,

49, 50, 51, 52, 53, 54

32

2, 3

REGOUT

VREG1 to

VREG6

AGND

DGND

IBB, IBB

4, 5 QBB, QBB

33, 34, 35

38

7

CCOMP1 to

CCOMP3

VTUNE

RSET

9 CP

27 CS

Description

Positive Power Supplies for I/Q Modulator. Apply a 5 V power supply to VCC1, which should be

decoupled with power supply decoupling capacitors. Connect VCC2, VCC3, and VCC4 to the same

5 V power supply.

3.3 V Output Supply. Drives VREG1, VREG2, VREG3, VREG4, VREG5, and VREG6.

Positive Power Supplies for PLL Synthesizer, VCO, and Serial Port. Connect these pins to REGOUT

(3.3 V) and decouple them separately.

Analog Ground. Connect to a low impedance ground plane.

Digital Ground. Connect to the same low impedance ground plane as the AGND pins.

Differential In-Phase Baseband Inputs. These high impedance inputs must be dc biased to approx-

imately 500 mV dc and should be driven from a low impedance source. Nominal characterized ac signal

swing is 450 mV p-p on each pin. These inputs are not self-biased and must be externally biased.

Differential Quadrature Baseband Inputs. These high impedance inputs must be dc-biased to

approximately 500 mV dc and should be driven from a low impedance source. Nominal charac-

terized ac signal swing is 450 mV p-p on each pin. These inputs are not self-biased and must be

externally biased.

Internal Compensation Nodes. These pins must be decoupled to ground with a 100 nF capacitor.

Control Input to the VCO. This voltage determines the output frequency and is derived from

filtering the CP output voltage.

Charge Pump Current Set. Connecting a resistor between this pin and ground sets the maximum

charge pump output current. The relationship between ICP and RSET is as follows:

ICPmax

=

23.5

RSET

where RSET = 4.7 kΩ and ICP max = 5 mA.

Charge Pump Output. When enabled, this output provides ±ICP to the external loop filter, which, in

turn, drives the internal VCO.

Chip Select, CMOS Input. When CS is high, the data stored in the shift registers is loaded into one of

31 latches. In I2C mode, when CS is high, the slave address of the device is 0x60, and, when CS is

low, the slave address is 0x40.

Rev. B | Page 11 of 48

Free Datasheet http://www.datasheet4u.com/

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet ADRF6755.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ADRF6750 | 950 MHz to 1575 MHz Quadrature Modulator | Analog Devices |

| ADRF6755 | 100 MHz to 2400 MHz I/Q Modulator | Analog Devices |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |