|

|

PDF PCKEL14 Data sheet ( Hoja de datos )

| Número de pieza | PCKEL14 | |

| Descripción | 2.5 V/3.3 V PECL/ECL 1:5 clock distribution chip | |

| Fabricantes | NXP Semiconductors | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de PCKEL14 (archivo pdf) en la parte inferior de esta página. Total 15 Páginas | ||

|

No Preview Available !

www.DataSheet.co.kr

PCKEL14

2.5 V/3.3 V PECL/ECL 1:5 clock distribution chip

Rev. 01 — 14 October 2002

Product data

1. Description

The PCKEL14 is a low skew 1:5 clock distribution chip designed explicitly for low

skew clock distribution applications. The device can be driven by either a differential

or single-ended ECL, or if positive power supplies are used, PECL input signal. The

PCKEL14 is designed to operate in ECL or PECL mode for a voltage supply range of

−2.375 V to −3.8 V (or 2.375 V to 3.8 V).

The PCKEL14 features a multiplexed clock input to allow for the distribution of a lower

speed scan or test clock along with the high speed system clock. When LOW (or left

open and pulled LOW by the input pull-down resistor), the SEL pin will select the

differential clock input.

The common enable (EN) is synchronous, so that the outputs will only be

enabled/disabled when they are already in the LOW state. This avoids any chance of

generating a runt clock pulse when the device is enabled/disabled, as can happen

with an asynchronous control. The internal flip-flop is clocked on the falling edge of

the input clock, therefore all associated specification limits are referenced to the

negative edge of the clock input.

The VBB pin (an internally generated voltage supply) is available to this device only.

For single-ended conditions, the unused differential input is connected to VBB as a

switching reference voltage. VBB may also rebias AC-coupled inputs. When used,

decouple VBB and VCC via a 0.01 µF capacitor and limit current sourcing or sinking to

0.1 mA. When not used, VBB should be left open.

2. Features

s 50 ps output-to-output skew at 3.3 V

s Synchronous enable/disable

s Multiplexed clock input

s ESD protection: > 2.5 kV HBM

s The PCK series contains temperature compensation

s PECL mode operating range: VCC = 2.375 V to 3.8 V, with VEE = 0 V

s NECL mode operating range: VCC = 0 V, with VEE = −2.375 V to −3.8 V

s Internal 75 kΩ pull-down resistors on all inputs, plus a 37.5 kΩ pull-up on CLK

s Q output will default LOW with inputs open or at VEE

s Meets or exceeds JEDEC spec EIA/JESD78 IC latch-up test

s Moisture sensitivity level 1

s Flammability rating: UL-94 code V-0 @ 1/8”

Datasheet pdf - http://www.DataSheet4U.net/

1 page

www.DataSheet.co.kr

Philips Semiconductors

PCKEL14

2.5 V/3.3 V PECL/ECL 1:5 clock distribution chip

8. Static characteristics

Table 5: PECL DC characteristics[1]

VCC = 2.5 V; VEE = 0 V [2]

Symbol Parameter

Conditions

IEE

VOH

VOL

VIH

VIL

VBB

VIHCMR

IIH

IIL

power supply current

HIGH-level output

voltage

LOW-level output

voltage

HIGH-level input

voltage

single-ended

LOW-level input voltage single-ended

output voltage

reference

HIGH-level input

voltage, common mode

range (differential)

HIGH-level input current

LOW-level input current CLK

CLK

Tamb = −40 °C

Tamb = +25 °C

Tamb = +85 °C Unit

Min Typ Max Min Typ Max Min Typ Max

- 28 40 - 30 40 - 31 42 mA

[3] 1325 1460 1620 1435 1545 1620 1475 1545 1620 mV

[3] 670 805 945 690 795 880 690 795 880 mV

[4] 1310 -

1620 1335 -

1620 1335 -

1620 mV

[4] 690 -

1.07 -

1025 690 -

1.25 1.15 -

1025 690 -

1.25 1.15 -

1025 mV

1.31 V

[5] 1.2 -

2.1 1.2 -

2.1 1.2 -

2.1 V

--

0.5 -

−300 -

150 -

-

- 0.5 -

- −300 -

150 -

-

- 0.5 -

- −300 -

150 µA

- µA

- µA

[1] Devices are designed to meet the DC specifications shown in this table, after thermal equilibrium has been established. The circuit is in

a test socket or mounted on a printed circuit board and transverse air flow greater than 500 LFPM is maintained.

[2] Input and output parameters vary 1:1 with VCC. VEE can vary +0.125 V to −1.3 V.

[3] All loading with 50 Ω to VCC − 2 V.

[4] Do not use VBB at VCC < 3.0 V.

[5] VIHCMR(min) varies 1:1 with VEE, VIHCMR(max) varies 1:1 with VCC. The VIHCMR range is referenced to the most positive side of the

differential input signal.

9397 750 09564

Product data

Rev. 01 — 14 October 2002

© Koninklijke Philips Electronics N.V. 2002. All rights reserved.

5 of 15

Datasheet pdf - http://www.DataSheet4U.net/

5 Page

www.DataSheet.co.kr

Philips Semiconductors

PCKEL14

2.5 V/3.3 V PECL/ECL 1:5 clock distribution chip

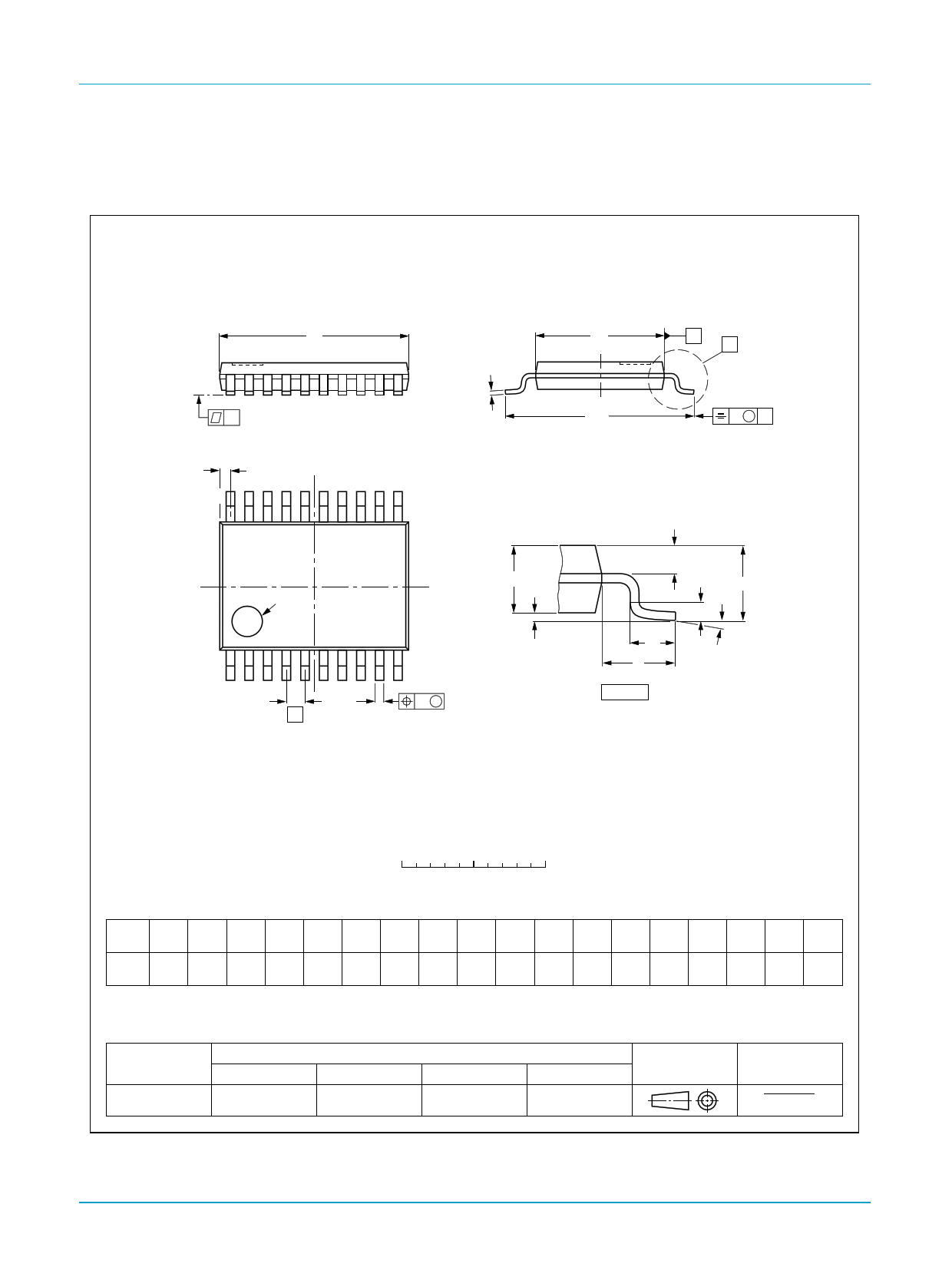

TSSOP20: plastic thin shrink small outline package; 20 leads; body width 4.4 mm

SOT360-1

y

Z

20

D

c

11

EA

X

HE v M A

pin 1 index

1

e

10

wM

bp

A2

A1

Q

(A3)

A

Lp

L

detail X

θ

0 2.5 5 mm

scale

DIMENSIONS (mm are the original dimensions)

UNIT

A

max.

A1

A2

A3

bp

c

mm

1.10

0.15

0.05

0.95

0.80

0.25

0.30

0.19

0.2

0.1

D (1) E (2)

e

6.6

6.4

4.5

4.3

0.65

HE

6.6

6.2

Notes

1. Plastic or metal protrusions of 0.15 mm maximum per side are not included.

2. Plastic interlead protrusions of 0.25 mm maximum per side are not included.

OUTLINE

VERSION

IEC

REFERENCES

JEDEC

EIAJ

SOT360-1

MO-153

L Lp Q

1.0

0.75

0.50

0.4

0.3

vwy

0.2 0.13 0.1

Z (1)

0.5

0.2

θ

8o

0o

EUROPEAN

PROJECTION

ISSUE DATE

95-02-04

99-12-27

Fig 7. TSSOP20 package outline (SOT360-1).

9397 750 09564

Product data

Rev. 01 — 14 October 2002

© Koninklijke Philips Electronics N.V. 2002. All rights reserved.

11 of 15

Datasheet pdf - http://www.DataSheet4U.net/

11 Page | ||

| Páginas | Total 15 Páginas | |

| PDF Descargar | [ Datasheet PCKEL14.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| PCKEL14 | 2.5 V/3.3 V PECL/ECL 1:5 clock distribution chip | NXP Semiconductors |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |