|

|

PDF ADC1213S Data sheet ( Hoja de datos )

| Número de pieza | ADC1213S | |

| Descripción | Single 12-bit ADC | |

| Fabricantes | NXP Semiconductors | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de ADC1213S (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

ADC1213S series

Single 12-bit ADC; 65 Msps, 80 Msps, 105 Msps or 125 Msps;

serial JESD204A interface

Rev. 1 — 14 March 2011

Product data sheet

1. General description

The ADC1213S is a single channel 12-bit Analog-to-Digital Converter (ADC) optimized for

high dynamic performance and low power at sample rates up to 125 Msps. Pipelined

architecture and output error correction ensure the ADC1213S is accurate enough to

guarantee zero missing codes over the entire operating range. Supplied from a 3 V source

for analog and a 1.8 V source for the output driver, it outputs data in serial mode via a

single differential lane, which complies with the JESD204A standard. The integration of

Serial Peripheral Interface (SPI) allows the user to easily configure the ADCs and the

serial output modes. The device also includes a programmable full-scale SPI to allow a

flexible input voltage range from 1 V (p-p) to 2 V (p-p).

Excellent dynamic performance is maintained from the baseband to input frequencies of

170 MHz or more, making the ADC1213S ideal for use in communications, imaging, and

medical applications.

2. Features and benefits

www.DataSheet4U.net

SNR, 70 dBFS; SFDR, 86 dBc

Sample rates up to 125 Msps

Single channel, 12-bit pipelined ADC

core

3 V, 1.8 V power supplies

Flexible input voltage range: 1 V (p-p)

to 2 V (p-p)

Serial output

Compliant with JESD204A serial

transmission standard

Pin compatible with ADC1613S series,

ADC1413S series, and ADC1113S125

Input bandwidth, 600 MHz

Power dissipation, 550 mW at 80 Msps

SPI register programming

Duty cycle stabilizer

High Intermediate Frequency (IF)

capability

Offset binary, two’s complement, gray

code

Power-down mode and Sleep mode

HVQFN32 package

3. Applications

Wireless and wired broadband

communications

Spectral analysis

Ultrasound equipment

Portable instrumentation

Imaging systems

1 page

NXP Semiconductors

ADC1213S series

Single 12-bit ADC; serial JESD204A interface

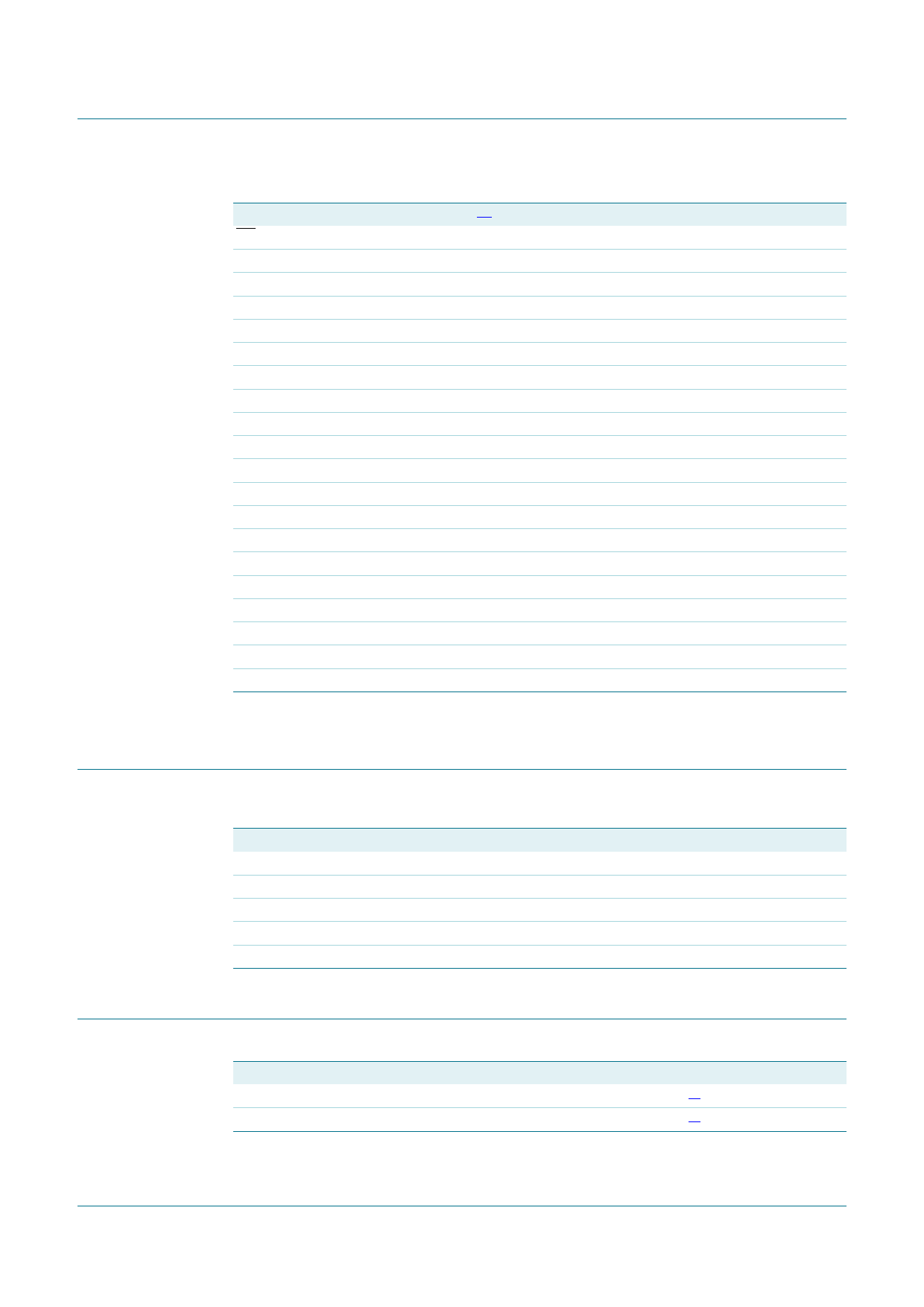

Table 2.

Symbol

CS

OTR

VDDD

DGND

DGND

VDDD

CMLP

CMLN

VDDD

DGND

DGND

n.c.

SYNCP

SYNCN

VDDD

DGND

VDDA

AGND

SENSE

VREF

Pin description …continued

Pin Type [1]

13 I

14 O

15 P

16 G

17 G

18 P

19 O

20 O

21 P

22 G

23 G

24 -

25 I

26 I

27 P

28 G

29 P

30 G

31 I

32 I/O

Description

chip select

out-of-range information

digital power supply 1.8 V

digital ground

digital ground

digital power supply 1.8 V

serial output

serial complementary output

digital power supply 1.8 V

digital ground

digital ground

not connected

positive synchronization signal from the receiver

negative synchronization signal from the receiver

digital power supply 1.8 V

digital ground

analog power supply 3 V

analog ground

reference programming pin

voltage reference input/output

[1] P: power supply; G: ground; I: input; O: output; I/O: input/output.

7. Limiting values

www.DataSheet4U.net

Table 3. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

Symbol Parameter

Conditions

Min

VDDA

VDDD(1V8)

Tstg

Tamb

Tj

analog supply voltage

digital supply voltage (1.8 V)

storage temperature

ambient temperature

junction temperature

−0.4

−0.4

−55

−40

-

Max

+4.6

+2.5

+125

+85

125

Unit

V

V

°C

°C

°C

8. Thermal characteristics

Table 4.

Symbol

Rth(j-a)

Rth(j-c)

Thermal characteristics

Parameter

thermal resistance from junction to ambient

thermal resistance from junction to case

Conditions

Typ

[1] 25.6

[1] 8.6

[1] Value for six layers board in still air with a minimum of 25 thermal vias.

Unit

K/W

K/W

ADC1213S_SER

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 1 — 14 March 2011

© NXP B.V. 2011. All rights reserved.

5 of 39

5 Page

NXP Semiconductors

ADC1213S series

Single 12-bit ADC; serial JESD204A interface

10.3 Serial output timing

The eye diagram of the serial output is shown in Figure 3 and Figure 4. Test conditions

are:

• 3.125 Gbps data rate

• Tamb = 25 °C

• DC-coupling with two different receiver common-mode voltages

Fig 3. Eye diagram at 1 V receiver common-mode

005aaa088

www.DataSheet4U.net

Fig 4. Eye diagram at 2 V receiver common-mode

005aaa089

ADC1213S_SER

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 1 — 14 March 2011

© NXP B.V. 2011. All rights reserved.

11 of 39

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet ADC1213S.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ADC12130 | Self-Calibrating 12-Bit Plus Sign Serial I/O A/D Converters with MUX and Sample/Hold | National Semiconductor |

| ADC12130 | ADC12130/32/38 Self-Cal 12-Bit + Serial I/O ADC w/MUX and Sample/Hold (Rev. G) | Texas Instruments |

| ADC12130CIN | Self-Calibrating 12-Bit Plus Sign Serial I/O A/D Converters with MUX and Sample/Hold | National Semiconductor |

| ADC12130CIWM | Self-Calibrating 12-Bit Plus Sign Serial I/O A/D Converters with MUX and Sample/Hold | National Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |