|

|

PDF GSC3E Data sheet ( Hoja de datos )

| Número de pieza | GSC3E | |

| Descripción | GPS Single Chip | |

| Fabricantes | SiRF | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de GSC3E (archivo pdf) en la parte inferior de esta página. Total 25 Páginas | ||

|

No Preview Available !

GSC3e/LPx and GSC3f/LPx

High Performance, Lowest Power, GPS Single Chip

Datasheet

SiRFstarIII Architecture

PRODUCT DESCRIPTION

The GSC3e/LPx and GSC3f/LPx are the pin-for-pin

compatible, lowest power versions of the advanced

GSC3e(f)/LP receiver in a single package. The baseband

has been ported to 65 nm technology, enabling an

additional power reduction of up to 30 percent. In the

GSC3e/LPx, the baseband and RF are integrated into the

7 mm x 10 mm x 1.4 mm package. In the GSC3f/LPx,

flash memory is included in the package making for an

extremely compact design. The GSC3e(f)/LPx includes a

powerful GPS DSP integrated with an ARM7TDMI micro-

processor and 1 Mb of SRAM. The GSC3e(f)/LPx archi-

tecture uses an FFT and Matched Filter that delivers

performance equivalent to more than 200,000 corre-

lators. This represents a quantum leap forward in GPS

performance.

ARCHITECTURE HIGHLIGHTS

Next Generation, Lowest Power, GPS Performance

X 200,000+ effective correlators for fast TTFF

and high sensitivity acquisitions

X Supports 20-Channel GPS

X High sensitivity for indoor fixes

X Extremely fast TTFFs at low signal levels

X Real-time navigation for location-based services

X Low 100 ms interrupt load on microprocessor for easy

IP implementation

X SBAS (WAAS, MSAS, and EGNOS) support

SiRFLocTM Client AGPS Support

X SiRF patented end-to-end solution

X Multimodes: mobile centric to network centric

X Mutli-standard support: 3GPP, 3GPP2, PDC, iDEN,

and TIA-916

X Supports AI3 and F interfaces

GSW3—Modular Software Support

X API compatible with GSW2

X RTOS friendly

PRODUCT HIGHLIGHTS

GSC3f/LPx—Digital, RF, and Flash Single Chip

X Digital, RF, and 4 Mb Flash in a single package

X Small 7 mm x 10 mm x 1.4 mm, BGA package

X ARM7TDMI CPU and SRAM to enable user tasks

X Accepts six reference frequencies between 13 MHz

and 26 MHz

X Extensive GPS peripherals: 2 UARTs, battery-backed

SRAM, and 14 GPIOs

Lowest Power

X Under 60 mW at full power

X 46 mW tracking power

X Push-to-Fix™ reduces power as much as 98%

Built On Proven Experience

X IP integration experience

X Highly developed design tools

X FCC E911 compliance experience

GPS Antenna

LNA

RF Filter

RTCXTAL Reference

Clock

GSC3e/LPx

and

GSC3f/LPx

Serial Data

1 PPS

Reset

ECLK

(Optional)

Serial Data

Power

Battery

Figure 1. Sample Architecture Diagram

Preliminary Datasheet S SiRF Proprietary and Confidential S 1055-1061 May 2009 S www.sirf.com

www.DataSheet.in

1 page

GSC3e/LPx and GSC3f/LPx: High Performance, Lowest Power, GPS Single Chip

CLOCK MODULE

This module generates all internal clocks such as the

Signal Processing (SP) Clock and Bus (B) Clock from

the Acquisition Clock. The Acquisition Clock is

generated by the RF section. The clocks generated by

Clock Module run the SiRFstarIII DSP and ARM and

control the various power management modes allowing

for maximum power savings and system flexibility.

DUART

The GSC3e(f)/LPx contains two full duplex serial ports.

One port is normally used for GPS data and receiver

control and the second serial port can be used as an

alternate communication channel. The transmit and

receive side of each port contains a 16-byte deep FIFO

with selectable bit rates ranging from 1.2 to 115.2

Kbaud. With special flashing software, maximum baud

rate of 921.6 kbps is available.

GPIO UNIT

The GSC3e(f)/LPx supports a variety of peripherals

through 14 GPIO lines. The GPIO unit centralizes

management of all GPIO lines and provides a simple

software interface for their control.

FLASH

The GSC3f/LPx integrates 4 Mbits of Flash memory.

This eliminates the need for external Flash and signifi-

cantly simplifies the routing associated with integrating

a GPS receiver into a board design. This chip is not

available in a pre-flashed version.

INTERRUPT CONTROLLER

The Interrupt Controller manages all internal or external

sources of interrupts. These include the SiRFstarIII

core, SBAS, DSP, DUART and external user interrupts.

SIRF BRIDGE UNIT

The SiRF Bridge Units (SBU1 and SBU2) provide low

power access to peripherals. SBU1 provides access to

general purpose ARM peripherals such as the serial

port UARTS, RTC, and interrupt controller. SBU2

provides access to the DSP core and its associated

memory. The DSP core also uses this bus for internal

communications. The ARM is able to perform byte,

half-word, and word transactions via the 32-bit

peripheral busses.

SRAM

The on-chip SRAM size is 1 Mbit (32k x 32) memory

that can be used for instructions or data. In many

applications it eliminates the need for external data

memory. The SRAM is designed for a combination of

low power and high speed, and can support single

cycle reads for all bus speeds.

SERIAL PERIPHERAL INTERFACE

The Serial Peripheral Interface (SPI) port handles

communication, such as reference frequency selection,

AGC, and power control, between the digital and RF

sections. The RF section acts in slave mode and can

only be controlled by the digital section using SiRF

software. The SPI port consists of SPI_CLK, SPI_DI,

SPI_DO, and SPI_CEB for the RF section, and corre-

sponds to SK, SI, SO, and CEB in the digital section.

The SPI port does not support additional SPI devices. It

is only used for internal communication between RF

and BB.

DSP RAM AND RAM SHARING

The GSC3e(f)/LP includes shared RAM which is

allocated between ARM and DSP core. This keeps the

overall size of the chip down while maximizing the

availability of memory.

FACTORY TESTING

The GSC3e(f)/LPx uses a memory built-in self-test

called MEMBIST to provide complete coverage of all

the memory during chip testing and qualification. This

is combined with the SCAN test logic using Automatic

Test Pattern Generation (ATPG) at the wafer level to

provide functional test coverage. (These functions are

not available to customers.)

Preliminary Datasheet S SiRF Proprietary and Confidential S 1055-1061 May 2009 S www.sirf.com

www.DataSheet.in

page 5

5 Page

GSC3e/LPx and GSC3f/LPx: High Performance, Lowest Power, GPS Single Chip

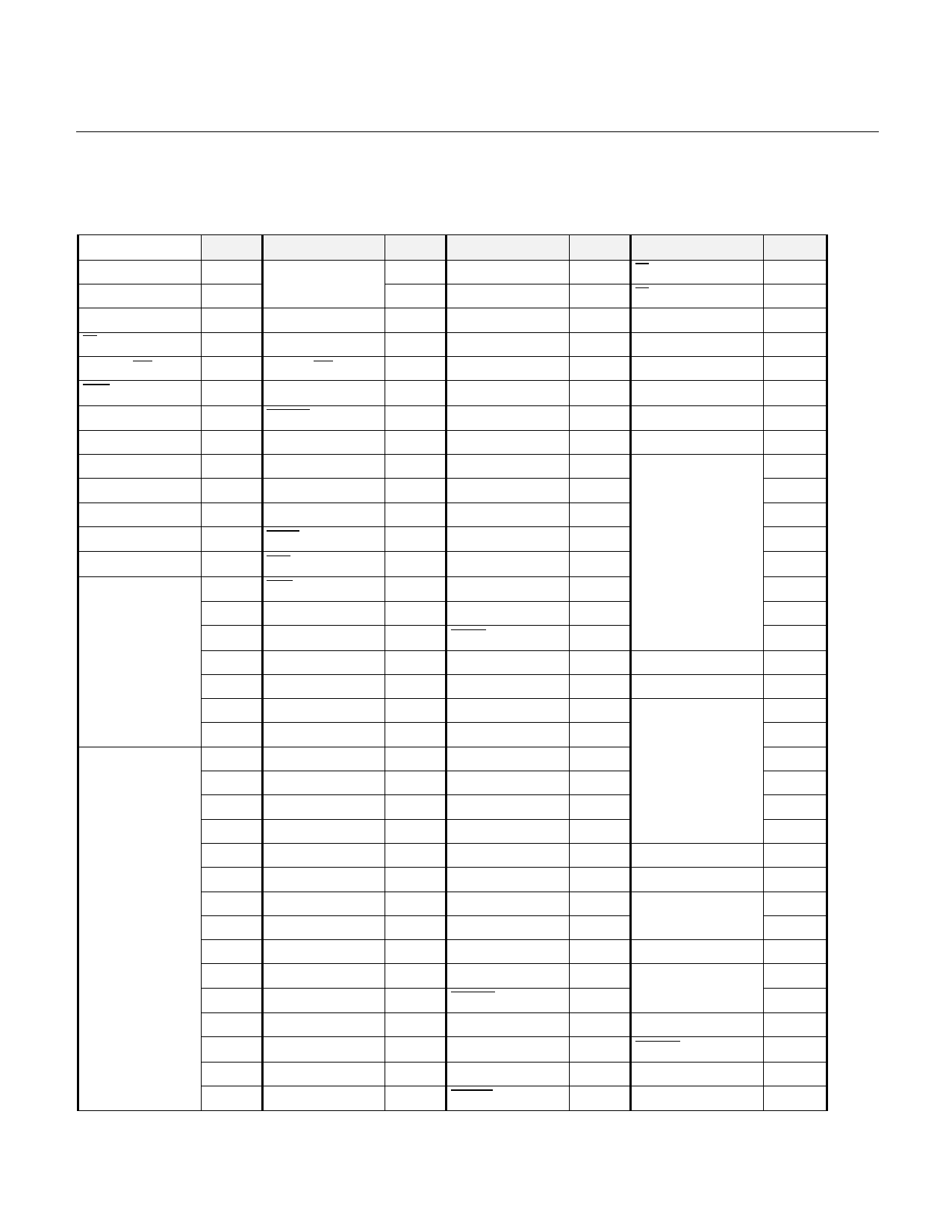

Table 1. GSC3e(f)/LPx Series Pin Identification

Name

Ball Name

AGCPWM/GPIO[2]

K3

GND_RF

CLKACQ_I (In)

J4

CLKACQ_O (Out)

K4

GPIO[0]/LNA EN

CS[0]

D3 GPIO[1] / ODO

GPIO[13] / CTS

F1 GPIO[14]/ RTS

CS_F

A3 GPIO[15]/YCLK

ECLK

A7 GRFRST

ED[0]

G1 JTCK

ED[1]

C2 JTDI

ED[2]

F3 JTDO

ED[3]

F2 JTMS

ED[7]

J2 JTRST

EIT[0] / GPIO[10]

B5

MOE

GND_BB

A1 MWE

D5 ON_OFF

D6 PLL_FILTER

E5 EA[0]

E6 EA[4]

F5 Reserved

F6 EA[1]

GND_RF

L4 ED[10]

L5 Reserved

L6 EA[3]

L7 ED[4]

L8 EA[2]

L9 EA[5]

N2 EA[6]

N3 ED[9]

N4 ED[8]

N5 EA[7]

N6 EA[8]

N7 Reserved

N8 EA[18]

N9 EA[19]

N10 ED[12]

Ball

P5

P7

A4

A2

C1

E1

P1

N1

J1

M1

L1

K1

D1

B2

G10

H6

A9

B6

B8

B9

C3

C8

C9

D2

D7

D8

D9

E2

E3

E8

E9

E10

F8

F9

G2

Name

ED[11]

ED[14]

EA[16]

EA[15]

EA[13]

EA[11]

EA[9]

ED[5]

ED[13]

ED[6]

EA[17]

EA[14]

EA[12]

EA[10]

ED[15]

RESET

RFIN

RFPWRUP

RIN

RTC_OUT

RTC_XI

RTC_XO

RXA

RXB

SCLK

SI

SIGN_MAG_I (In)

SIGN_MAG_O (Out)

SK

SO

SPI_CEB

SPI_CLK

SPI_DI

SPI_DO

SRESET

Ball

G3

G4

G5

G6

G7

G8

G9

H2

H3

H4

H5

H7

H8

H9

J3

H10

P6

B1

F10

K10

P10

L10

A5

C7

A8

J6

J5

K5

J7

J8

K9

K7

K8

K6

J10

Name

SS[0] / GPIO[3]

SS[1]/ GPIO[4]

TIMEMARK / GPIO[9]

TMODE

TP_IF

TXA

TXB

NC

VCC_RF

VCC_RF

VCC_RTC

VDD_BB

VDD_FLASH

VDD_PLL

VDD_REG

VDD_RTC

VDDK

VDDPLL_O

WAKEUP

XTAL_IN

XTAL_OUT

Ball

J9

H1

C6

D10

P4

A6

B7

P8

M3

M4

M5

M6

M7

M8

M9

M10

M2

P9

D4

E4

F4

K2

L2

L3

B3

C5

C4

F7

B4

B10

C10

A10

E7

P2

P3

Preliminary Datasheet S SiRF Proprietary and Confidential S 1055-1061 May 2009 S www.sirf.com

www.DataSheet.in

page 11

11 Page | ||

| Páginas | Total 25 Páginas | |

| PDF Descargar | [ Datasheet GSC3E.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| GSC301-10M0900 | 900MHz Band 10dB Chip Coupler | Soshin |

| GSC302-20M0900 | 900MHz Band 20dB Chip Coupler | Soshin |

| GSC303-30M0900 | 900MHz Band 30dB Chip Coupler | Soshin |

| GSC310-10M1900 | 1900MHz Band 10dB Chip Coupler | Soshin |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |