|

|

PDF CAT25256 Data sheet ( Hoja de datos )

| Número de pieza | CAT25256 | |

| Descripción | 256-Kb SPI Serial CMOS EEPROM | |

| Fabricantes | ON Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de CAT25256 (archivo pdf) en la parte inferior de esta página. Total 19 Páginas | ||

|

No Preview Available !

CAT25256

256-Kb SPI Serial CMOS

EEPROM

Description

The CAT25256 is a 256−Kb Serial CMOS EEPROM device

internally organized as 32Kx8 bits. This features a 64−byte page write

buffer and supports the Serial Peripheral Interface (SPI) protocol. The

device is enabled through a Chip Select (CS) input. In addition, the

required bus signals are clock input (SCK), data input (SI) and data

output (SO) lines. The HOLD input may be used to pause any serial

communication with the CAT25256 device. The device features

software and hardware write protection, including partial as well as

full array protection.

On−Chip ECC (Error Correction Code) makes the device suitable

for high reliability applications.*

Features

• 20 MHz (5 V) SPI Compatible

• 1.8 V to 5.5 V Supply Voltage Range

• SPI Modes (0,0) & (1,1)

• 64−byte Page Write Buffer

• Additional Identification Page with Permanent Write Protection

(New Product)

• Self−timed Write Cycle

• Hardware and Software Protection

• Block Write Protection

− Protect 1/4, 1/2 or Entire EEPROM Array

• Low Power CMOS Technology

• 1,000,000 Program/Erase Cycles

• 100 Year Data Retention

• Industrial and Extended Temperature Range

• 8−lead PDIP, SOIC, TSSOP and 8−pad UDFN Packages

• This Device is Pb−Free, Halogen Free/BFR Free, and RoHS

Compliant

VCC

SI

CS

WP

HOLD

SCK

CAT25256

SO

VSS

Figure 1. Functional Symbol

* Available for New Product (Rev. E)

www.onsemi.com

SOIC−8

V SUFFIX

CASE 751BD

UDFN−8

HU4 SUFFIX

CASE 517AZ

SOIC−8

X SUFFIX

CASE 751BE

PDIP−8

L SUFFIX

CASE 646AA

TSSOP−8

Y SUFFIX

CASE 948AL

PIN CONFIGURATIONS

CS 1

SO

WP

VSS

VCC

HOLD

SCK

SI

PDIP (L), SOIC (V, X), TSSOP (Y),

UDFN (HU4)

(Top View)

** Not recommended for new designs.

PIN FUNCTION

Pin Name†

Function

CS Chip Select

SO Serial Data Output

WP Write Protect

VSS Ground

SI Serial Data Input

SCK

Serial Clock

HOLD

Hold Transmission Input

VCC Power Supply

†The exposed pad for the UDFN package can be left

floating or connected to Ground.

ORDERING INFORMATION

See detailed ordering and shipping information in the package

dimensions section on page 19 of this data sheet.

© Semiconductor Components Industries, LLC, 2015

June, 2015 − Rev. 8

1

Publication Order Number:

CAT25256/D

1 page

CAT25256

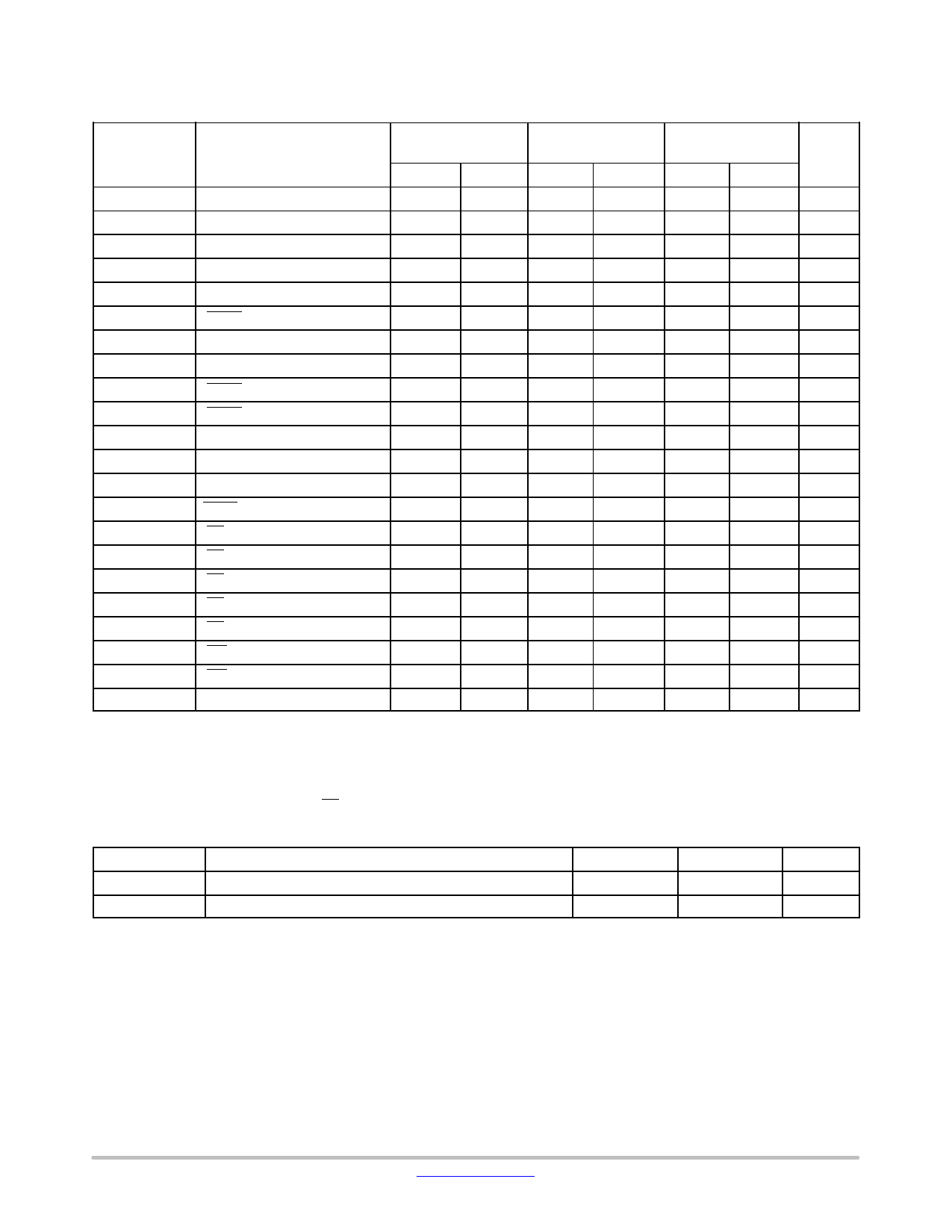

Table 8. A.C. CHARACTERISTICS – NEW PRODUCT (Rev E) (VCC = 1.8 V to 5.5 V, TA = −40°C to +85°C (Industrial) and

VCC = 2.5 V to 5.5 V, TA = −40°C to +125°C (Extended), unless otherwise specified.) (Note 11)

VCC < 2.5 V

−405C to +855C

VCC . 2.5 V

−405C to +1255C

VCC . 4.5 V

−405C to +855C

Symbol

Parameter

Min Max Min Max Min

fSCK

Clock Frequency

DC 5 DC 10 DC

tSU Data Setup Time

20

10

5

tH Data Hold Time

20 10

5

tWH SCK High Time

75 40 20

tWL SCK Low Time

75 40 20

tLZ HOLD to Output Low Z

50 25

tRI (Note 12) Input Rise Time

22

tFI (Note 12) Input Fall Time

22

tHD HOLD Setup Time

0

0

0

tCD HOLD Hold Time

10

10

5

tV Output Valid from Clock Low

75 40

tHO Output Hold Time

0

0

0

tDIS Output Disable Time

50 20

tHZ HOLD to Output High Z

100 25

tCS CS High Time

80 40 20

tCSS

CS Setup Time

30 30 15

tCSH

CS Hold Time

30 30 20

tCNS

CS Inactive Setup Time

20

20

15

tCNH

CS Inactive Hold Time

20

20

15

tWPS

WP Setup Time

10 10

10

tWPH

WP Hold Time

10 10 10

tWC (Note 13) Write Cycle Time

55

11. AC Test Conditions:

Input Pulse Voltages: 0.3 VCC to 0.7 VCC

Input rise and fall times: ≤ 10 ns

Input and output reference voltages: 0.5 VCC

Output load: current source IOL max/IOH max; CL = 30 pF

12. This parameter is tested initially and after a design or process change that affects the parameter.

13. tWC is the time from the rising edge of CS after a valid write sequence to the end of the internal write cycle.

Max Units

20 MHz

ns

ns

ns

ns

25 ns

2 ms

2 ms

ns

ns

20 ns

ns

20 ns

25 ns

ns

ns

ns

ns

ns

ns

ns

5 ms

Table 9. POWER−UP TIMING (Notes 12, 14)

Symbol

Parameter

Min Max

tPUR

Power−up to Read Operation

0.1 1

tPUW

Power−up to Write Operation

0.1 1

14. tPUR and tPUW are the delays required from the time VCC is stable until the specified operation can be initiated.

Units

ms

ms

www.onsemi.com

5

5 Page

CAT25256

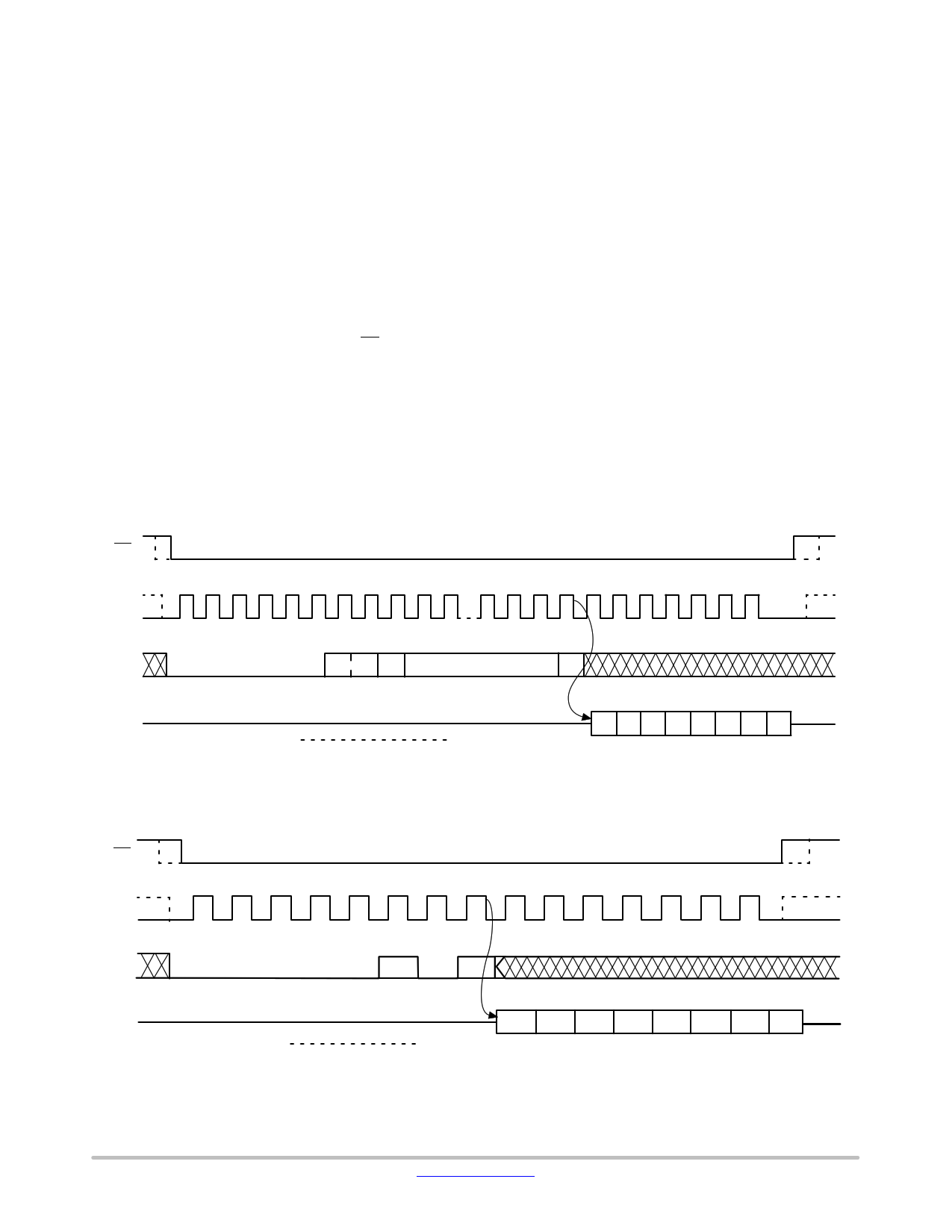

READ OPERATIONS

Read from Memory Array

To read from memory, the host sends a READ instruction

followed by a 16−bit address (see Table 14 for the number

of significant address bits).

After receiving the last address bit, the CAT25256 will

respond by shifting out data on the SO pin (as shown in

Figure 9). Sequentially stored data can be read out by simply

continuing to run the clock. The internal address pointer is

automatically incremented to the next higher address as data

is shifted out. After reaching the highest memory address,

the address counter “rolls over” to the lowest memory

address, and the read cycle can be continued indefinitely.

The read operation is terminated by taking CS high.

Read Identification Page

Reading the additional 64−byte Identification Page (IP) is

achieved using the same Read command sequence as used

for Read from main memory array (Figure 9). The IPL bit

from the Status Register must be set (IPL = 1) before

attempting to read from the IP. The [A5:A0] are the address

significant bits that point to the data byte shifted out on the

SO pin. If the CS continues to be held low, the internal

address register defined by [A5:A0] bits is automatically

incremented and the next data byte from the IP is shifted out.

The byte address must not exceed the 64−byte page

boundary.

Read Status Register

To read the status register, the host simply sends a RDSR

command. After receiving the last bit of the command, the

CAT25256 will shift out the contents of the status register on

the SO pin (Figure 10). The status register may be read at

any time, including during an internal write cycle. While the

internal write cycle is in progress, the RDSR command will

output the full content of the status register (New product,

Rev. E) or the RDY (Ready) bit only (i.e., data out = FFh) for

previous product revisions C, D (Mature product). For easy

detection of the internal write cycle completion, both during

writing to the memory array and to the status register, we

recommend sampling the RDY bit only through the polling

routine. After detecting the RDY bit “0”, the next RDSR

instruction will always output the expected content of the

status register.

CS

SCK

0 1 2 3 4 5 6 7 8 9 10 20 21 22 23 24 25 26 27 28 29 30

OPCODE

BYTE ADDRESS*

SI 0 0 0 0 0 0 1 1 AN

A0

SO

Dashed Line = mode (1, 1)

HIGH IMPEDANCE

* Please check the Byte Address Table (Table 14)

DATA OUT

765432 10

MSB

Figure 9. READ Timing

CS

SCK

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14

OPCODE

SI

0 0000

1 01

HIGH IMPEDANCE

SO

DATA OUT

7 6 5 4 3 2 10

Dashed Line = mode (1, 1)

MSB

Figure 10. RDSR Timing

www.onsemi.com

11

11 Page | ||

| Páginas | Total 19 Páginas | |

| PDF Descargar | [ Datasheet CAT25256.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| CAT25256 | 256-Kb SPI Serial CMOS EEPROM | ON Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |