|

|

PDF ADC12DL040 Data sheet ( Hoja de datos )

| Número de pieza | ADC12DL040 | |

| Descripción | Dual 12-Bit/ 40 MSPS/ 3V/ 210mW A/D Converter | |

| Fabricantes | National Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de ADC12DL040 (archivo pdf) en la parte inferior de esta página. Total 26 Páginas | ||

|

No Preview Available !

November 2005

www.DataSheet4U.com

ADC12DL040

Dual 12-Bit, 40 MSPS, 3V, 210mW A/D Converter

General Description

The ADC12DL040 is a dual, low power monolithic CMOS

analog-to-digital converter capable of converting analog in-

put signals into 12-bit digital words at 40 Megasamples per

second (MSPS). This converter uses a differential, pipeline

architecture with digital error correction and an on-chip

sample-and-hold circuit to minimize power consumption

while providing excellent dynamic performance and a 250

MHz Full Power Bandwidth. Operating on a single +3.0V

power supply, the ADC12DL040 achieves 11.1 effective bits

at nyquist and consumes just 210 mW at 40 MSPS, including

the reference current. The Power Down feature reduces

power consumption to 36 mW.

The differential inputs provide a full scale differential input

swing equal to 2 times VREF with the possibility of a single-

ended input. Full use of the differential input is recom-

mended for optimum performance. The digital outputs from

the two ADC’s are available on a single multiplexed 12-bit

bus or on separate buses. Duty cycle stabilization and output

data format are selectable using a quad state function pin.

The output data can be set for offset binary or two’s comple-

ment.

To ease interfacing to lower voltage systems, the digital

output driver power pins of the ADC12DL040 can be con-

nected to a separate supply voltage in the range of 2.4V to

the analog supply voltage.

This device is available in the 64-lead TQFP package and

will operate over the industrial temperature range of −40˚C to

+85˚C. An evaluation board is available to ease the evalua-

tion process.

Features

n Single +3.0V supply operation

n Internal sample-and-hold

n Internal reference

n Outputs 2.4V to 3.6V compatible

n Power down mode

n Duty Cycle Stabilizer

n Multiplexed Output Mode

Key Specifications

n Resolution

n DNL

n SNR (fIN = 10 MHz)

n SFDR (fIN = 10 MHz)

n Data Latency

n Power Consumption

n -- Operating

n -- Power Down Mode

Applications

n Ultrasound and Imaging

n Instrumentation

n Communications Receivers

n Sonar/Radar

n xDSL

n Cable Modems

n DSP Front Ends

12 Bits

±0.3 LSB (typ)

69 dB (typ)

85 dB (typ)

7 Clock Cycles

210 mW (typ)

36 mW (typ)

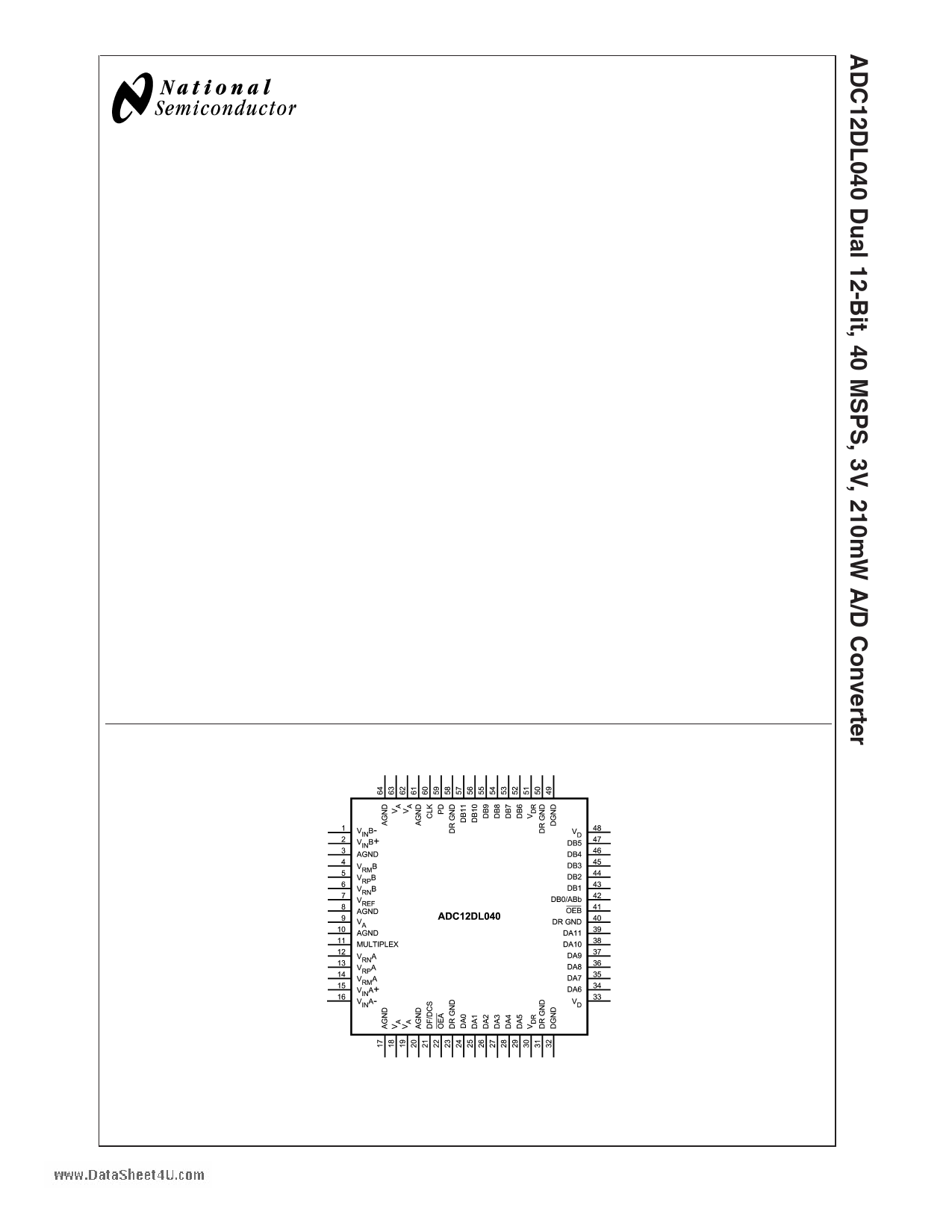

Connection Diagram

TRI-STATE® is a registered trademark of National Semiconductor Corporation.

© 2005 National Semiconductor Corporation DS201002

20100201

www.national.com

1 page

Absolute Maximum Ratings (Notes 1,

2)

If Military/Aerospace specified devices are required,

please contact the National Semiconductor Sales Office/

Distributors for availability and specifications.

VA, VD, VDR

|VA–VD|

Voltage on Any Input or Output Pin

4.2V

≤ 100 mV

−0.3V to (VA or VD

+0.3V)

Input Current at Any Pin (Note 3)

±25 mA

Package Input Current (Note 3)

±50 mA

Package Dissipation at TA = 25˚C

ESD Susceptibility

See (Note 4)

Human Body Model (Note 5)

2500V

Machine Model (Note 5)

250V

Storage Temperature

−65˚C to +150˚C

Soldering process must comply with National

Semiconductor’s Reflow Temperature Profile

specifications. Refer to www.national.com/packaging.

(Note 6)

Operating Ratings (Notes 1, 2)

www.DataSheet4U.com

Operating Temperature

−40˚C ≤ TA ≤ +85˚C

Supply Voltage (VA, VD)

+2.7V to +3.6V

Output Driver Supply (VDR)

+2.4V to VD

CLK, PD, OEA, OEB

−0.05V to (VD + 0.05V)

Analog Input Pins

0V to 2.6V

VCM

|AGND–DGND|

0.5V to 2.0V

≤100mV

Clock Duty Cycle (DCS On)

20% to 80%

Clock Duty Cycle (DCS Off)

40% to 60%

Converter Electrical Characteristics

Unless otherwise specified, the following specifications apply for AGND = DGND = DR GND = 0V, VA = VD = +3.0V, VDR =

+2.5V, PD = 0V, External VREF = +1.0V, fCLK = 40 MHz, fIN = 10 MHz, tr = tf = 2 ns, CL = 15 pF/pin, Duty Cycle Stabilizer On,

parallel output mode. Boldface limits apply for TJ = TMIN to TMAX: all other limits TJ = 25˚C (Notes 7, 8, 9)

Symbol

Parameter

Conditions

Typical Limits

(Note 10) (Note 10)

Units

(Limits)

STATIC CONVERTER CHARACTERISTICS

Resolution with No Missing Codes

12 Bits (min)

INL Integral Non Linearity (Note 11)

±0.8

± 2.6

LSB (max)

DNL

Differential Non Linearity

±0.3

+0.96,

-0.9

LSB (max)

PGE

Positive Gain Error

±0.2

+2.5,

-3.3

%FS (max)

NGE

Negative Gain Error

±0.2

±3.6

%FS (max)

TC GE

VOFF

TC

VOFF

Gain Error Tempco

Offset Error (VIN+ = VIN−)

Offset Error Tempco

Under Range Output Code

−40˚C ≤ TA ≤ +85˚C

−40˚C ≤ TA ≤ +85˚C

5 ppm/˚C

0.1

±0.8

%FS (max)

3 ppm/˚C

00

Over Range Output Code

4095

4095

REFERENCE AND ANALOG INPUT CHARACTERISTICS

VCM Common Mode Input Voltage

0.5

1.5

2.0

V (min)

V (max)

VRMA,

VRMB

CIN

VREF

Reference Output Voltage

VIN Input Capacitance (each pin to

GND)

External Reference Voltage (Note

13)

Output load = 1 mA

VIN = 2.5 Vdc

+ 0.7 Vrms

(CLK LOW)

(CLK HIGH)

1.5

8

7

1.00

0.8

1.2

V

pF

pF

V (min)

V (max)

Reference Input Resistance

1 MΩ (min)

5 www.national.com

5 Page

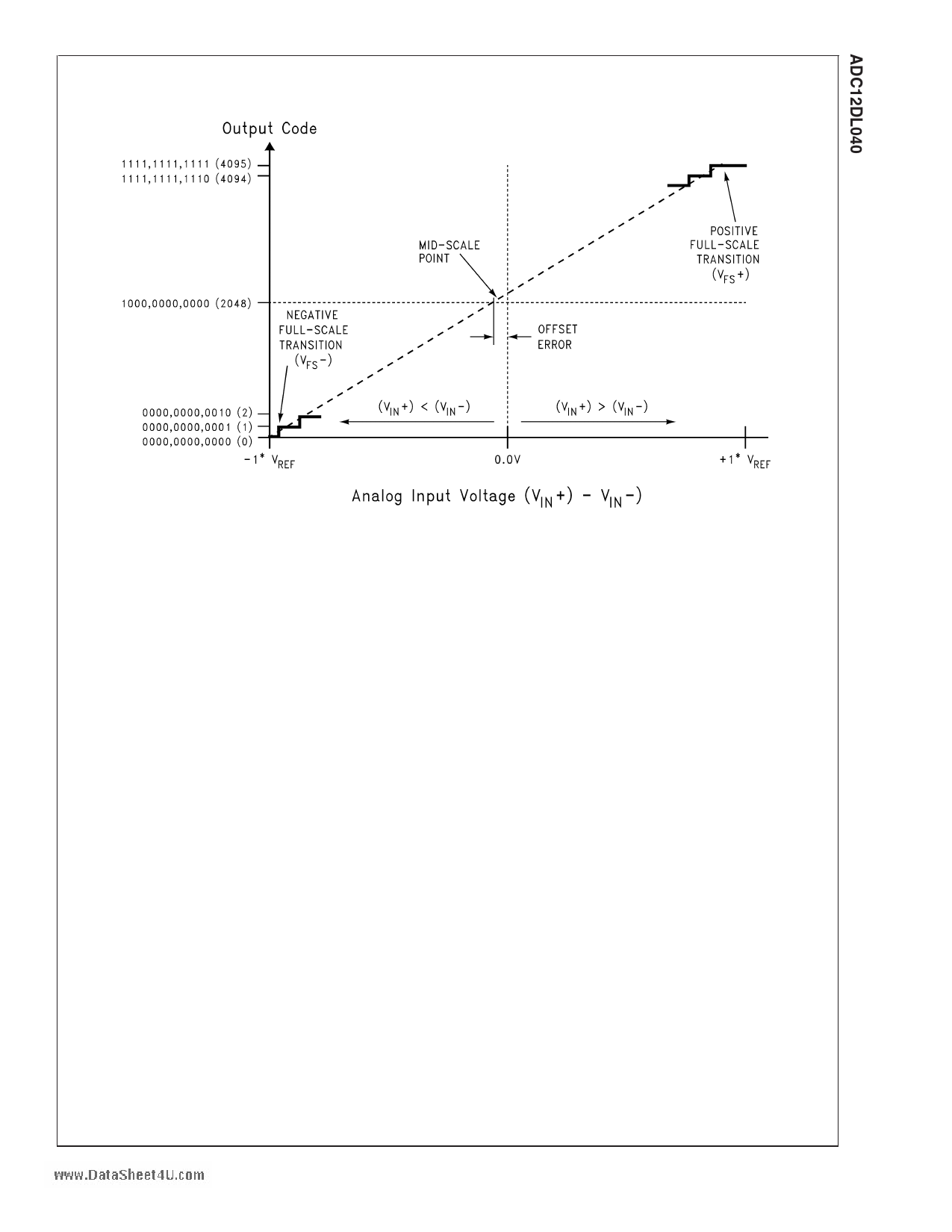

Transfer Characteristic

www.DataSheet4U.com

FIGURE 1. Transfer Characteristic

20100210

11 www.national.com

11 Page | ||

| Páginas | Total 26 Páginas | |

| PDF Descargar | [ Datasheet ADC12DL040.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ADC12DL040 | Dual 12-Bit/ 40 MSPS/ 3V/ 210mW A/D Converter | National Semiconductor |

| ADC12DL040 | Dual 12-Bit / 40 MSPS / 3V - 210mW A/D Converter | National Semiconductor |

| ADC12DL040 | ADC12DL040 Dual 12-Bit 40 MSPS 3V 210mW A/D Converter (Rev. D) | Texas Instruments |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |