|

|

PDF 80C453 Data sheet ( Hoja de datos )

| Número de pieza | 80C453 | |

| Descripción | CMOS single-chip 8-bit microcontrollers | |

| Fabricantes | NXP Semiconductors | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de 80C453 (archivo pdf) en la parte inferior de esta página. Total 23 Páginas | ||

|

No Preview Available !

Philips Semiconductors

CMOS single-chip 8-bit microcontrollers

Preliminary specification

80C453/83wCw4w5.D3at/a8S7heCet44U5.c3om

DESCRIPTION

The Philips 8XC453 is an I/O expanded single-chip microcontroller

fabricated with Philips high-density CMOS technology. Philips

epitaxial substrate minimizes latch-up sensitivity.

The 8XC453 is a functional extension of the 87C51 microcontroller

with three additional I/O ports and four I/O control lines. The 8XC453

is available in 68-pin LCC packages. Four control lines associated

with port 6 facilitate high-speed asynchronous I/O functions.

The 87C453 includes an 8k × 8 EPROM, a 256 × 8 RAM, 56 I/O

lines, two 16-bit timer/counters, a seven source, two priority level,

nested interrupt structure, a serial I/O port for either a full duplex

UART, I/O expansion, or multi-processor communications, and

on-chip oscillator and clock circuits.

The 87C453 has two software selectable modes of reduced activity

for further power reduction; idle mode and power-down mode. Idle

mode freezes the CPU while allowing the RAM, timers, serial port,

and interrupt system to continue functioning. Power-down mode

freezes the oscillator, causing all other chip functions to be

inoperative while maintaining the RAM contents.

FEATURES

• 80C51 based architecture

• Seven 8-bit I/O ports

• Port 6 features:

– Eight data pins

– Four control pins

– Direct MPU bus interface

– ISA Bus Interface

– Parallel printer interface

– IBF and OBF interrupts

– A flag latch on host write

• On the microcontroller:

– 8k × 8 EPROM

Quick pulse programming algorithm

Two-level program security system

– 256 × 8 RAM

– Two 16-bit counter/timers

– Two external interrupts

• External memory addressing capability

– 64k ROM and 64k RAM

• Low power consumption:

– Normal operation: less than 24mA at 5V, 16MHz

– Idle mode

– Power-down mode

• Reduced EMI

• Full-duplex enhanced UART

– Framing error detection

– Automatic address recognition

LCC PIN FUNCTIONS

9

1

10

61

60

LCC

26 44

Pin Function

1 EA/VPP

2 P2.0/A8

3 P2.1/A9

4 P2.2/A10

5 P2.3/A11

6 P2.4/A12

7 P2.5/A13

8 P2.6/A14

9 P2.7/A15

10 P0.7/AD7

11 P0.6/AD6

12 P0.5/AD5

13 P0.4/AD4

14 P0.3/AD3

15 P0.2/AD2

16 P0.1/AD1

17 P0.0/AD0

18 VCC

19 P4.7

20 P4.6

21 P4.5

22 P4.4

23 P4.3

27 43

Pin Function

24 P4.2

25 P4.1

26 P4.0

27 P1.0

28 P1.1

29 P1.2

30 P1.3

31 P1.4

32 P1.5

33 P1.6

34 P1.7

35 RST

36 P3.0/RxD

37 P3.1/TxD

38 P3.2/INTO

39 P3.3/INT1

40 P3.4/T0

41 P3.5/T1

42 P3.6/WR

43 P3.7/RD

44 P5.0

45 P5.1

46 P5.2

Pin Function

47 P5.3

48 P5.4

49 P5.5

50 P5.6

51 P5.7

52 XTAL2

53 XTAL1

54 VSS

55 ODS

56 IDS

57 BFLAG

58 AFLAG

59 P6.0

60 P6.1

61 P6.2

62 P6.3

63 P6.4

64 P6.5

65 P6.6

66 P6.7

67 PSEN

68 ALE/PROG

SU00157

1996 Aug 15

3-311

1 page

Philips Semiconductors

CMOS single-chip 8-bit microcontrollers

Preliminary specification

80C453/83wCw4w5.D3at/a8S7heCet44U5.c3om

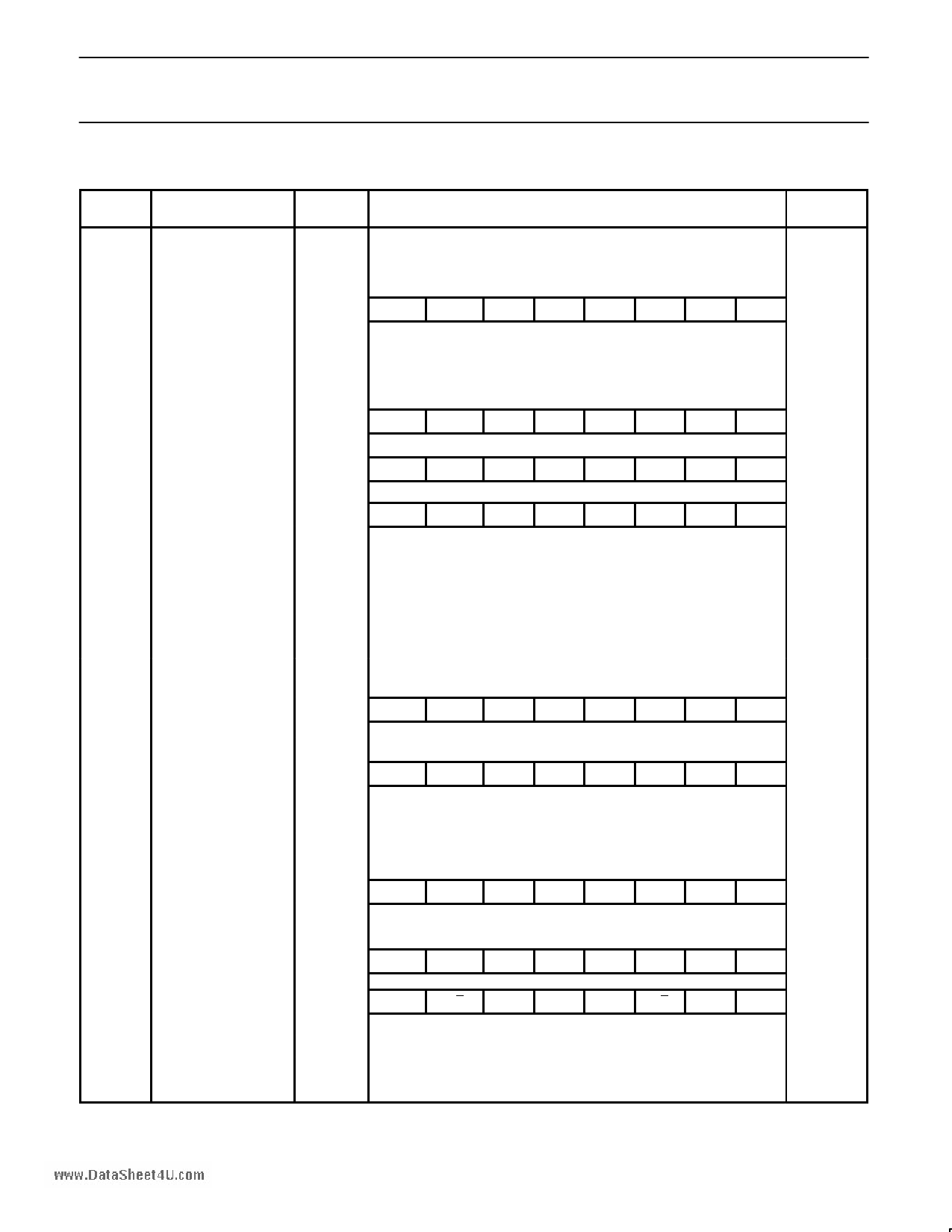

Table 1.

SYMBOL

ACC*

B*

CSR*#

DPTR

DPH

DPL

IP*

87C453 Special Function Registers

DESCRIPTION

DIRECT

ADDRESS MSB

Accumulator

E0H E7

B register

F0H F7

EF

Port 6 command/status

E8H

MB1

Data pointer (2 bytes)

Data pointer high

83H

Data pointer low

82H

BF

Interrupt priority

B8H –

BIT NAMES AND ADDRESSES

E6

F6

EE

MB0

E5

F5

ED

MA1

E4

F4

EC

MA0

E3

F3

EB

OBFC

E2

F2

EA

IDSM

BE BD BC BB BA

POB PIB PS PT1 PX1

LSB

E1 E0

F1 F0

E9 E8

OBF IBF

B9 B8

PT0 PX0

RESET

VALUE

00H

00H

FCH

00H

00H

x0000000B

AUXR# Auxiliary register

IE*

P0*

P1*

P2*

P3*

P4*#

P5*#

P6*#

PCON

Interrupt enable

Port 0

Port 1

Port 2

Port 3

Port 4

Port 5

Port 6

Power control

8EH

A8H

80H

90H

A0H

B0H

C0H

C8H

D8H

87H

– – – – – – AF AO x0000000B

AF AE AD AC AB AA A9 A8

EA IOB IIB ES ET1 EX1 ET0 EX0 00000000B

87 B6 85 84 83 82 81 80 FFH

97 96 95 94 93 92 91 90 FFH

A7 A6 A5 A4 A3 A2 A1 A0 FFH

B7 B6 B5 B4 B3 B2 B1 B0 FFH

C7 C6 C5 C4 C3 C2 C1 C0 FFH

CF CE CD CC CB CA C9 C8 FFH

DF DE DD DC DB DA D9 D8 FFH

SMOD1 SMOD0 –

POF1 GF1 GF0 PD

IDL 00xx0000B

PSW*

SADDR#

SADEN#

SBUF

Program status word

Slave Address

Slave Address Mask

Serial data buffer

SCON*

SP

Serial port control

Stack pointer

TCON* Timer/counter control

D0H

A9H

B9H

99H

98H

81H

88H

D7

CY

9F

SM0

8F

TF1

D6 D5 D4 D3 D2 D1

AC F0 RS1 RS0 OV –

9E 9D 9C 9B 9A

SM1 SM2 REN TB8 RB8

99

TI

8E 8D 8C 8B 8A 89

TR1 TF0 TR0 IE1 IT1 IE0

D0

P 00H

00H

00H

xxxxxxxxB

98

RI 00H

07H

88

IT0 00H

TMOD Timer/counter mode

89H GATE C/T M1 M0 GATE C/T M1 M0 00H

TH0 Timer 0 high byte

8CH

00H

TH1 Timer 1 high byte

8DH

00H

TL0 Timer 0 low byte

8AH

00H

TL1 Timer 1 low byte

8BH

NOTES:

* SFRs are bit addressable.

# SFRs are modified from or added to the 80C51 SFRs.

1. REset value depends on reset source.

00H

1996 Aug 15

3-315

5 Page

Philips Semiconductors

CMOS single-chip 8-bit microcontrollers

Preliminary specification

80C453/83wCw4w5.D3at/a8S7heCet44U5.c3om

ODS is active low for output driver control. The OBF flag can be

programmed to be cleared on the negative or positive edge of ODS.

Can produce an IOB interrupt (see Figure 2).

IDS – Input data strobe for port 6. IDS is used to control the port 6

input latch and input buffer full flag (IBF) bit in the CSR. The input

data latch can be programmed to be transparent when IDS is low

and latched on the positive transition of IDS, or to latch only on the

positive transition of IDS. Correspondingly, the IBF flag is set on the

negative or positive transition of IDS. Can produce an IIB interrupt

(see Figure 2).

AFLAG – AFLAG is a bidirectional I/O pin which can be

programmed to be an output set high or low under program control,

or to output the state of the output buffer full flag. AFLAG can also

be programmed to be an input which selects whether the contents of

the output buffer, or the contents of the port 6 control status register

will output on port 6. This feature grants complete port 6 status to

external devices.

BFLAG – BFLAG is a bidirectional I/O pin which can be

programmed to be an output, set high or low under program control,

or to output the state of the input buffer full flag. BFLAG can also be

programmed to input an enable signal for port 6. When BFLAG is

used as an enable input, port 6 output drivers are in the

high-impedance state, and the input latch does not respond to the

IDS strobe when BFLAG is high. Both features are enabled when

BFLAG is low. This feature facilitates the use of the 87C453 in

bused multiprocessor systems.

CONTROL STATUS REGISTER

The control status register (CSR) establishes the mode of operation

for port 6 and indicates the current status of port 6 I/O registers. All

control status register bits can be read and written by the CPU,

except bits 0 and 1, which are read only. Reset writes ones to bits 2

through 7, and writes zeros to bits 0 and 1 (see Table 3).

CSR.0 Input Buffer Full Flag (IBF) (Read Only) – The IBF bit is

set to a logic 1 when port 6 data is loaded into the input buffer under

control of IDS. This can occur on the negative or positive edge of

IDS, as determined by CSR.2. When IBF is set, the Interrupt Enable

Register bit IIB (IE.5) is set. The Interrupt Service Routine vector

address for this interrupt is 002BH. IBF is cleared when the CPU

reads the input buffer register.

CSR.1 Output Buffer Full Flag (OBF) (Read Only) – The OBF flag

is set to a logic 1 when the CPU writes to the port 6 output data

buffer. OBF is cleared by the positive or negative edge of ODS, as

determined by CSR.3. When OBF is cleared, the Interrupt Enable

Register bit IOB (IE.6) is set. The Interrupt Service Routine vector

address for this interrupt is 0033H.

CSR.2 IDS Mode Select (IDSM) – When CSR.2 = 0, a low-to-high

transition on the IDS pin sets the IBF flag. The Port 6 input buffer is

loaded on the IDS positive edge. When CSR.2 = 1, a high-to-low

transition on the IDS pin sets the IBF flag. Port 6 input buffer is

transparent when IDS is low, and latched when IDS is high.

CSR.3 Output Buffer Full Flag Clear Mode (OBFC) – When

CSR.3 = 1, the positive edge of the ODS input clears the OBF flag.

When CSR.3 = 0, the negative edge of the ODS input clears the

OBF flag.

CSR.4, CSR.5 AFLAG Mode Select (MA0, MA1) – Bits 4 and 5

select the mode of operation for the AFLAG pin as follows:

MA1

0

0

1

1

MA0

0

1

0

1

AFLAG Function

Logic 0 output

Logic 1 output

OBF flag output (CSR.1)

Select (SEL) input mode

The select (SEL) input mode is used to determine whether the port 6

data register or the control status register is output on port 6. When

the select feature is enabled, the AFLAG input controls the source of

port 6 output data. A logic 0 on AFLAG input selects the port 6 data

register, and a logic 1 on AFLAG input selects the control status

register.

The value of the AFLAG input is latched into the Auxiliary Register

(AUXR) bit 1 (AUXR.1). Checking this bit (AF) will allow the

87C453’s program to determine if Port 6 was loaded with data or a

UPI command.

CSR.6, CSR.7 BFLAG Mode Select (MB0, MB1) – Bits 6 and 7

select the mode operation as follows:

MB1 MB0

00

01

10

11

BFLAG Function

Logic 0 output

Logic 1 output

IBF flag output (CSR.0)

Port enable (PE)

In the port enable mode, IDS and ODS inputs are disabled when

BFLAG input is high. When the BFLAG input is low, the port is

enabled for I/O.

Reduced EMI Mode – The on–chip clock distribution drivers have

been identified as the cause of most of the EMI emissions from the

80C51 family. By tailoring the clock drivers properly, a compromise

between maximum operating speed and minimal EMI emissions can

be achieved. Typically, an order in magnitude of reduction is

possible over previous designs. This feature has been implemented

on this chip along with the additional capability of turning off the ALE

output. Setting the AO bit (AUXR.0) in the AUXR special function

register will disable the ALE output. Reset forces a 0 into AUXR.0 to

enable normal 80C51 type operation.

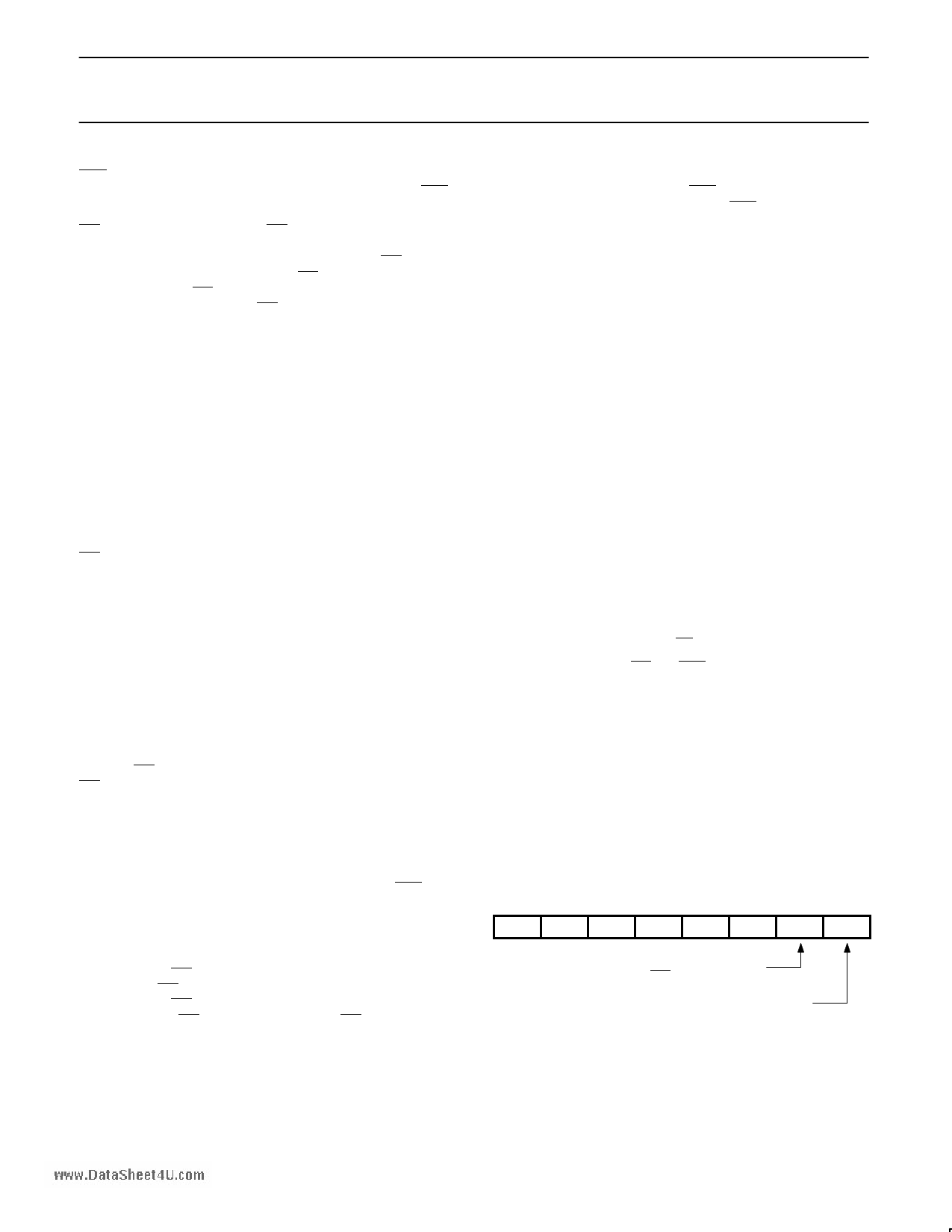

Auxiliary Register (AUXR)

76543210

– – – – – – AF AO

Latched value of AFLAG when Port 6

inputs data from IDS strobe

0 = ALE enabled

1 = ALE disabled

1996 Aug 15

3-321

11 Page | ||

| Páginas | Total 23 Páginas | |

| PDF Descargar | [ Datasheet 80C453.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| 80C451 | 80C51 8-bit microcontroller family 4K/128 OTP/ROM/ROMless/ expanded I/O | NXP Semiconductors |

| 80C453 | CMOS single-chip 8-bit microcontrollers | NXP Semiconductors |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |