|

|

PDF LC72133M Data sheet ( Hoja de datos )

| Número de pieza | LC72133M | |

| Descripción | PLL Frequency Synthesizer for Electronic Tuning | |

| Fabricantes | Sanyo Semicon Device | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de LC72133M (archivo pdf) en la parte inferior de esta página. Total 22 Páginas | ||

|

No Preview Available !

Ordering number : EN5427A

CMOS LSI

LC72133M, 72133V

PLL Frequency Synthesizer for

Electronic Tuning

Overview

The LC72133M and LC72133V are a phase-locked loop

frequency synthesizer LSI circuits for use in radio tuners.

It supports low-voltage (2.7 to 3.6 V) operation and can

implement high-performance AM/FM tuners easily.

Functions

• High speed programmable dividers

— FMIN: 10 to 120 MHz ..........pulse swallower

(built-in divide-by-two prescaler), VDD ≥ 2.7 V

10 to 130 MHz ..........pulse swallower

(built-in divide-by-two prescaler), VDD ≥ 3.0 V

— AMIN: 2 to 40 MHz ..............pulse swallower

0.5 to 10 MHz ...........direct division

• IF counter

— IFIN: 0.4 to 12 MHz ...........AM/FM IF counter

• Reference frequencies

— Twelve selectable frequencies

(4.5 or 7.2 MHz crystal)

1, 3, 5, 9, 10, 3.125, 6.25, 12.5, 15, 25, 50 and 100 kHz

• Phase comparator

— Dead zone control

— Unlock detection circuit

— Deadlock clear circuit

• Built-in MOS transistor for forming an active low-pass

filter

• I/O ports

— Dedicated output ports: 4

— Input or output ports: 2

— Support clock time base output

• Serial data I/O

— Support CCB format communication with the

system controller.

• Operating ranges

— Supply voltage........................2.7 to 3.6 V

— Operating temperature............–20 to +70°C

• Package

MFP20

SSOP20

Package Dimensions

unit: mm

3036B-MFP20

[LC72133M]

unit: mm

3179A-SSOP20

[LC72133V]

SANYO: MFP20

SANYO: SSOP20

• CCB is a trademark of SANYO ELECTRIC CO., LTD.

• CCB is SANYO’s original bus format and all the bus

addresses are controlled by SANYO.

SANYO Electric Co.,Ltd. Semiconductor Bussiness Headquarters

TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110 JAPAN

22897HA (OT)/63196HA (OT) No. 5427-1/22

1 page

Pin Functions

Symbol

Pin No.

LC72133M, 72133V

Type

Functions

XIN

XOUT

1

20

Xtal OSC

• Crystal resonator connection

(4.5/7.2 MHz)

Circuit configuration

FMIN

AMIN

CE

CL

DI

• FMIN is selected when the serial data input DVS bit is

set to 1.

• The input frequency range is from 10 to 130 MHz.

• The input signal passes through the internal divide-by-

two prescaler and is input to the swallow counter.

• The divisor can be in the range 272 to 65535. However,

14

Local oscillator

signal input

since the signal has passed through the divide-by-two

prescaler, the actual divisor is twice the set value.

Operating

conditions

Operating power-

supply voltage

Operating input

levels

FMIN input frequency

10 to 90 MHz 10 to 120 MHz 10 to 130 MHz

2.7 to 3.6 V 2.7 to 3.6 V 3.0 to 3.6 V

70 to 900

mVrms

100 to 900

mVrms

70 to 900

mVrms

• AMIN is selected when the serial data input DVS bit is

set to 0.

• When the serial data input SNS bit is set to 1:

— The input frequency range is 2 to 40 MHz.

— The signal is directly input to the swallow counter.

13

Local oscillator

signal input

— The divisor can be in the range 272 to 65535, and

the divisor used will be the value set.

• When the serial data input SNS bit is set to 0:

— The input frequency range is 0.5 to 10 MHz.

— The signal is directly input to a 12-bit programmable

divider.

— The divisor can be in the range 4 to 4095, and the

divisor used will be the value set.

2 Chip enable

Set this pin high when inputting (DI) or outputting (DO)

serial data.

4 Clock

• Used as the synchronization clock when inputting (DI) or

outputting (DO) serial data.

3

Data input

• Inputs serial data transferred from the controller to the

LC72133.

• Outputs serial data transferred from the LC72133 to the

DO

5 Data output

controller.

The content of the output data is determined by the

serial data DOC0 to DOC2.

• The LC72133 power supply pin (VDD = 2.7 to 3.6 V)

VDD

15

Power supply

• The power on reset circuit operates when power is first

applied.

Continued on next page.

No. 5427-5/22

5 Page

LC72133M, 72133V

Continued from preceding page.

No. Control block/data

IF counter control data

(11) IFS

LSI test data

TEST 0 to TEST 2

(12)

(13) DNC

Functions

• Note that if this value is set to zero the system enters input sensitivity degradation mode,

and the sensitivity is reduced to 10 to 30 mV rms.

* See the “IF Counter Operation” item for details.

• LSI test data

TEST0

TEST1 These values must all be set to 0.

TEST2

These test data are set to 0 automatically after the power-on reset.

Don’t care. This data must be set to 0.

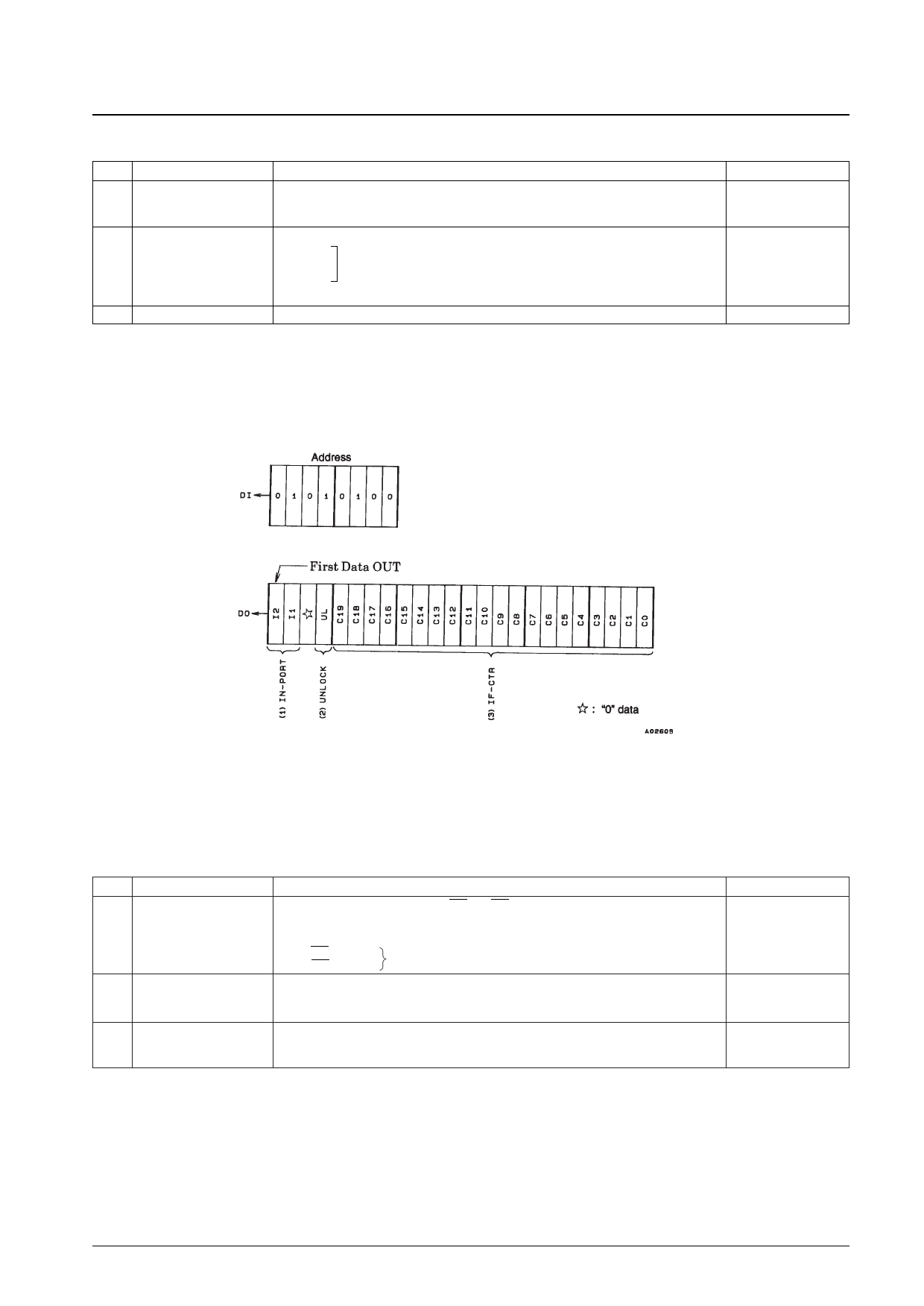

3. DO Output Data (Serial Data Output)

• OUT Mode

Related data

4. DO Output Data

No. Control block/data

I/O port data

I2, I1

(1)

PLL unlock data

(2) UL

IF counter binary data

(3) C19 to C0

Functions

• Latched from the pin states of the IO1 and IO2 I/O ports.

• These values follow the pin states regardless of the input or output setting.

• Data is latched at the point where the circuit enters data output mode (OUT mode).

I1 ← IO1 pin state High: 1

I2 ← IO2 pin state Low: 0

• Latched from the state of the unlock detection circuit.

UL ← 0: Unlocked

UL ← 1: Locked or detection stopped mode

• Latched from the value of the IF counter (20-bit binary counter).

C19 ← MSB of the binary counter

C0 ← LSB of the binary counter

Related data

IOC1,

IOC2

UL0,

UL1

CTE,

GT0,

GT1

No. 5427-11/22

11 Page | ||

| Páginas | Total 22 Páginas | |

| PDF Descargar | [ Datasheet LC72133M.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| LC72133M | PLL Frequency Synthesizer for Electronic Tuning | Sanyo Semicon Device |

| LC72133V | PLL Frequency Synthesizer for Electronic Tuning | Sanyo Semicon Device |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |