|

|

PDF AD9551 Data sheet ( Hoja de datos )

| Número de pieza | AD9551 | |

| Descripción | Multiservice Clock Generator | |

| Fabricantes | Analog Devices | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AD9551 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

Multiservice Clock Generator

AD9551

FEATURES

Translation between any two standard network rates

Dual reference inputs and dual clock outputs

Pin programmable for standard network rate translation

SPI programmable for arbitrary rational rate translation

Output frequencies from 10 MHz to 900 MHz

Input frequencies from 19.44 MHz to 806 MHz

On-chip VCO

Meets OC-192 high band jitter generation requirement

Supports standard forward error correction (FEC) rates

Supports holdover operation

Supports hitless switchover and phase build-out (even with

unequal reference frequencies)

SPI-compatible 3-wire programming interface

Single supply (3.3 V)

APPLICATIONS

Multiservice switches

Multiservice routers

Exact network clock frequency translation

General-purpose frequency translation

GENERAL DESCRIPTION

The AD9551 accepts one or two reference input signals to synthe-

size one or two output signals. The AD9551 uses a fractional-N

PLL that precisely translates the reference frequency to the desired

output frequency. The input receivers and output drivers provide

both single-ended and differential operation.

Reference conditioning and switchover circuitry internally

synchronizes the two references so that if one reference fails,

there is virtually no phase perturbation at the output.

The AD9551 uses an external crystal and an internal DCXO to

provide for holdover operation. If both references fail, the device

maintains a steady output signal.

The AD9551 provides pin-selectable, preset divider values for

standard (and FEC adjusted) network frequencies. The pin-

selectable frequencies include any combination of 15 possible

input frequencies and 16 possible output frequencies. A SPI

interface provides further flexibility by making it possible to

program almost any rational input/output frequency ratio.

The AD9551 is a clock generator that employs fractional-N-based

phase-locked loops (PLL) using sigma-delta (Σ-Δ) modulators

(SDMs). The fractional frequency synthesis capability enables

the device to meet the frequency and feature requirements for

multiservice switch applications. The AD9551 precisely generates

a wide range of standard frequencies when using any one of those

same standard frequencies as a timing base (reference). The

primary challenge of this function is the precise generation of the

desired output frequency because even a slight output frequency

error can cause problems for downstream clocking circuits in

the form of bit or cycle slips. The requirement for exact frequency

translation in such applications necessitates the use of a frac-

tional-N-based PLL architecture with variable modulus.

BASIC BLOCK DIAGRAM

CRYSTAL

(26MHz)

REFA

REFB

REFERENCE

CONDITIONING

AND SWITCH-

OVER

HOLDOVER

LOOP

PLL

OUTPUT

CIRCUITRY

OUT1

OUT2

PIN-DEFINED AND SERIAL

PROGRAMMING

Figure 1.

AD9551

Rev. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarksandregisteredtrademarksarethepropertyoftheirrespectiveowners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

Fax: 781.461.3113

©2009 Analog Devices, Inc. All rights reserved.

1 page

www.DataSheet4U.com

Parameter

Duty Cycle

Rise/Fall Time1 (20% to 80%)

Min Typ Max

45 55

500 745

1 The listed values are for the slower edge (rise or fall).

JITTER CHARACTERISTICS (180 HZ LOOP BANDWIDTH)

Table 3.

Parameter

JITTER GENERATION

12 kHz to 20 MHz

50 kHz to 80 MHz

4 MHz to 80 MHz

JITTER TRANSFER BANDWIDTH

Min Typ Max

1.3

0.8

0.5

0.6

0.1

180

JITTER TRANSFER PEAKING

0.1

CRYSTAL OSCILLATOR CHARACTERISTICS

Table 4.

Parameter

CRYSTAL FREQUENCY

Range

Tolerance

CRYSTAL MOTIONAL RESISTANCE

DCXO LOAD CAPACITANCE CONTROL

RANGE

Min

19

Typ

26

3 to 21

POWER CONSUMPTION

Table 5.

Parameter

TOTAL CURRENT

VDD CURRENT BY PIN

Pin 9

Pin 23

Pin 27

Pin 34

LVPECL OUTPUT DRIVER

Min Typ

169

24

78

36

36

38

Max

52

20

100

Max

195

27

84

42

42

AD9551

Unit Test Conditions/Comments

% At maximum output frequency

ps 3.3 V CMOS; standard drive strength

setting; 10 pF load

Unit Test Conditions/Comments

ps rms

ps rms

ps rms

ps rms

ps rms

Hz

dB

fIN = 19.44 MHz, fOUT = 622.08 MHz

fIN = 622.08 MHz, fOUT = 622.08 MHz

fIN = 19.44 MHz, fOUT = 622.08 MHz

fIN = 622.08 MHz, fOUT = 622.08 MHz

fIN = 622.08 MHz, fOUT = 622.08 MHz

See the Typical Performance Characteristics

section

See the Typical Performance Characteristics

section

Unit Test Conditions/Comments

MHz

ppm

Ω

pF Requires a crystal with a 10 pF load

specification

Unit Test Conditions/Comments

mA At maximum output frequency with both

output channels active

mA

mA

mA

mA

mA 900 MHz with 100 Ω termination between

both pins of the output driver

Rev. A | Page 5 of 40

5 Page

www.DataSheet4U.com

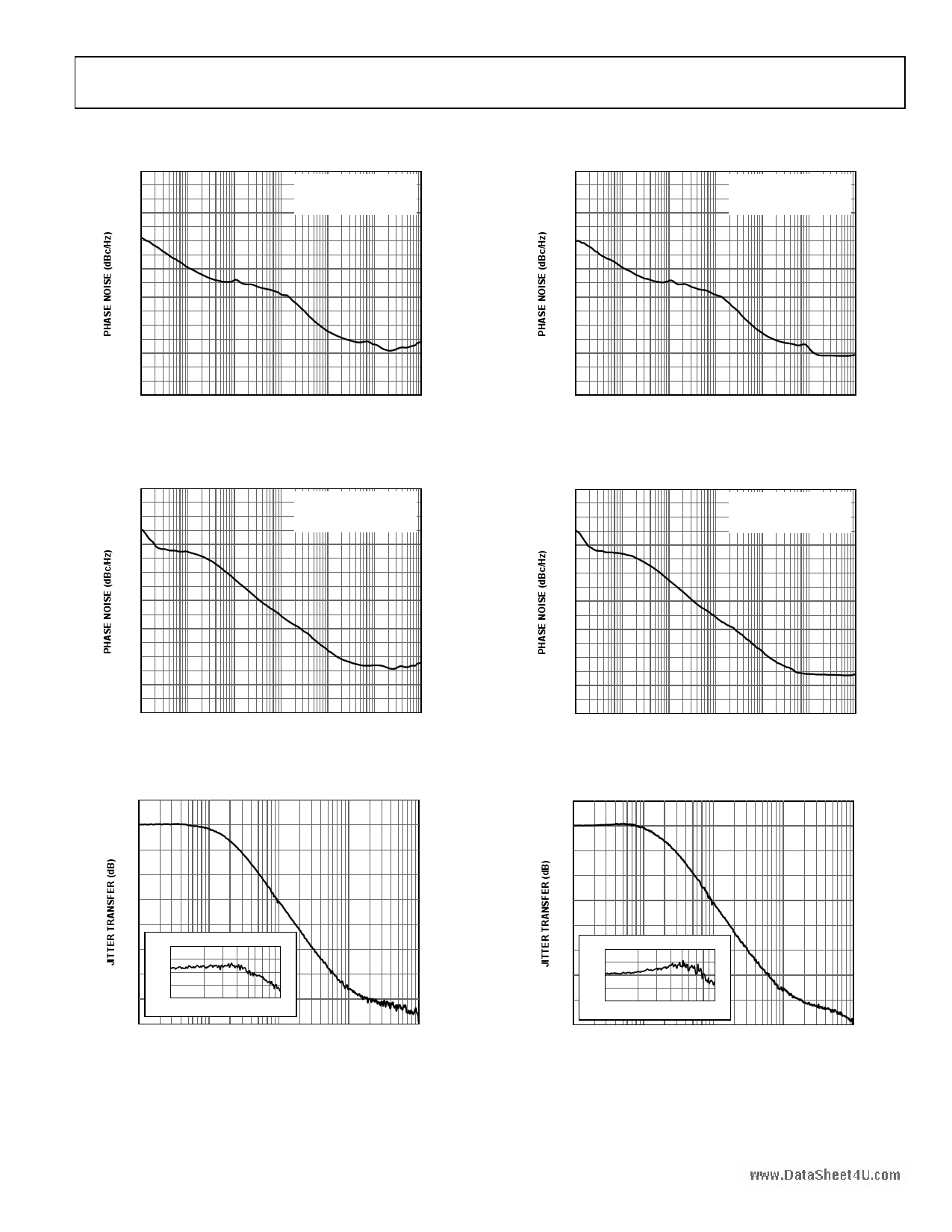

TYPICAL PERFORMANCE CHARACTERISTICS

–20

–30

–40

–50

–60

–70

–80

–90

–100

–110

–120

–130

–140

–150

–160

–170

–180

100

CARRIER 622.080005MHz 0.8813dBm

RMS JITTER:

0.827ps (12kHz TO 20MHz)

0.618ps (50kHz TO 80MHz)

1k

10k 100k 1M

10M

FREQUENCY OFFSET FROM CARRIER (Hz)

100M

Figure 4. Phase Noise, Fractional-N

(fIN = 622.08 MHz, fOUT1 = 622.08 MHz, fXTAL = 26 MHz)

–20

–30

–40

–50

–60

–70

–80

–90

–100

–110

–120

–130

–140

–150

–160

–170

–180

100

CARRIER 622.080027MHz 0.5414dBm

RMS JITTER:

1.336ps (12kHz TO 20MHz)

0.463ps (50kHz TO 80MHz)

1k

10k 100k 1M

10M

FREQUENCY OFFSET FROM CARRIER (Hz)

100M

Figure 5. Phase Noise, 19.44 MHz Mode, Fractional-N

(fIN = 19.44 MHz, fOUT1 = 622.08 MHz, fXTAL = 52 MHz)

5

0

–5

–10

–15

–20

–25 1.0

0.5

–30 0

–0.5

–35

–1.0

10

100

–40

10

100 1k 10k

FREQUENCY OFFSET (Hz)

Figure 6. Jitter Transfer (Minimal Peaking)

(Register 0x33[7] = 0)

100k

AD9551

–20

–30

–40

–50

–60

–70

–80

–90

–100

–110

–120

–130

–140

–150

–160

–170

–180

100

CARRIER 619.666689MHz 0.8705dBm

RMS JITTER:

0.773ps (12kHz TO 20MHz)

0.559ps (50kHz TO 80MHz)

1k

10k 100k 1M

10M

FREQUENCY OFFSET FROM CARRIER (Hz)

100M

Figure 7. Phase Noise, Integer-N

(fIN = 622.08 MHz, fOUT1 = 619.67 MHz, fXTAL = 26 MHz)

–20

–30

–40

–50

–60

–70

–80

–90

–100

–110

–120

–130

–140

–150

–160

–170

–180

100

CARRIER 619.666712MHz 0.6233dBm

RMS JITTER:

1.327ps (12kHz TO 20MHz)

0.438ps (50kHz TO 80MHz)

1k

10k 100k 1M

10M

FREQUENCY OFFSET FROM CARRIER (Hz)

100M

Figure 8. Phase Noise, 19.44 MHz Mode, Integer-N

(fIN = 19.44 MHz, fOUT1 = 619.67 MHz, fXTAL = 52 MHz)

5

0

–5

–10

–15

–20

–25 1.0

0.5

–30 0

–0.5

–35 –1.0

10

100

–40

10

100 1k 10k

FREQUENCY OFFSET (Hz)

Figure 9. Jitter Transfer (Nominal Peaking)

(Register 0x33[7] = 1)

100k

Rev. A | Page 11 of 40

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet AD9551.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AD9550 | Integer-N Clock Translator | Analog Devices |

| AD9551 | Multiservice Clock Generator | Analog Devices |

| AD9552 | Oscillator Frequency Up Converter | Analog Devices |

| AD9553 | Flexible Clock Translator | Analog Devices |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |