|

|

PDF NJU26040 Data sheet ( Hoja de datos )

| Número de pieza | NJU26040 | |

| Descripción | Sound functions are possible to customization | |

| Fabricantes | JRC | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de NJU26040 (archivo pdf) en la parte inferior de esta página. Total 17 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

NJU26040 Series

NJU26040 Series Data Sheet

■ General Description

The NJU26040 Series a Digital Signal Processor with built-in

OTP (One Time Programmable).

By the DSP with built-in OTP, customization is possible from

various sound technology.

The NJU26040 Series is suitable for TV, mini-component,

speakers system and other audio products. This DSP can

constitute a small system by combining a CODEC.

■ Package

NJU26040V

■ FEATURES

• 24bit Fixed-point Digital Signal Processing

• System Clock Frequency

: Maximum 38MHz

• Digital Audio Interface

• Digital Audio Format

: 3 Input ports / 3Output ports

: I2S 24bit, Left- justified, Right-justified, BCK : 32/64fs

• Master / Slave Mode

• Serial Host Interface

: In Master mode, MCK : 768/384/256fs

: I2C bus (Standard-mode/100kbps, First-mode/400kbps)

: 4-Wire Serial bus (Clock, Enable, Input data, Output data)

• Power Supply

: 3.3 V

• Input terminal

: 5.0V Input tolerant

• Package

: SSOP32 ( Pb-Free )

■ Block Diagram

S C L/SC K

SD A /S D O U T

RESETb

MCK

CLKOUT

CLK

A D 1/SD IN A D 2/SSb

S E R IA L

HOST

IN TERFACE

24bit Fix ed-point D SP C ore

PROGRAM

CONTROL

ALU

24 -B IT x 24-B IT

M U LTIPLIER

TIM IN G

GENERATOR

ADDRESS G EN ERATIO N U N IT

SERIAL AUDIO

IN TERFACE

BCKO

LRO

SDO0

SDI

[2 :0 ]

SDO1

SDO2

BCKI

LRI

DATA

RAM

FIRM W ARE

O TP/R A M

G eneral I/O

IN TERFACE

G PIO 3

G PIO 2

G PIO 1

G PIO 0

Fig.1 NJU26040 Hardware Block Diagram

Ver.2006-09-13

-1-

1 page

www.DataSheet4U.com

■ Electric Characteristics

NJU26040 Series

Table 3 Electric Characteristics

Parameter

Symbol

Test Condition

Operating Voltage

Operating Current

High Level Input Voltage

Low Level Input Voltage

High Level Output Voltage

Low Level Output Voltage

Leakage Current *4

Input Transition Time *5

Clock Frequency

Clock Duty Cycle

VDD

IDD

VIH

VIL

VOH

VOL

IIN

IIN(PU)

II(PD)N

tr / tf

fOSC

rEC

VDD pin

VDD=3.3V *1

IOH= -1mA *3

IOL= 1mA

VIN = VSS to VDD

No.11pin (CLK) *6

No.11pin (CLK)

( VDD=3.3V, fOSC=36.864MHz, Ta=25°C )

Min.

Typ.

Max.

Units

3.0 3.3 3.6 V

-

VDD x 0.7

0

VDD x 0.8

0

-10

-100

-10

42

-

-

-

-

-

-

-

-

VDD *2

VDD x 0.3

VDD

VDD x 0.2

10

10

100

mA

V

µA

- - 100 ns

20 36.864 38 MHz

45 50 55 %

*1 Current of operation is at the starting time.

It is an actual measurement (reference value) in the room temperature in standard firmware in the default state.

*2 Open-Drain input/output pins are +5.0V tolerant except GPIO0,GPIO1/GPIO2,GPIO3 and CLK input pin at supply voltage

VDD = 3.3V.

*3 Except No.2pin: SDA/SDOUT (Open-Drain).

*4 I IN(PU) : 26pin, I IN(PD) : 27,28,29,30,31 pin

*5 The tr / tf of No.2,3,4,5 pins are specified separately. Refer to the software specification.

*6 Use it by the clock frequency united with the specification of firmware. Refer to the software specification.

Usually, the sampling frequency of 768 Fs is supplied to CLK pin.

Ver.2006-09-13

-5-

5 Page

www.DataSheet4U.com

NJU26040 Series

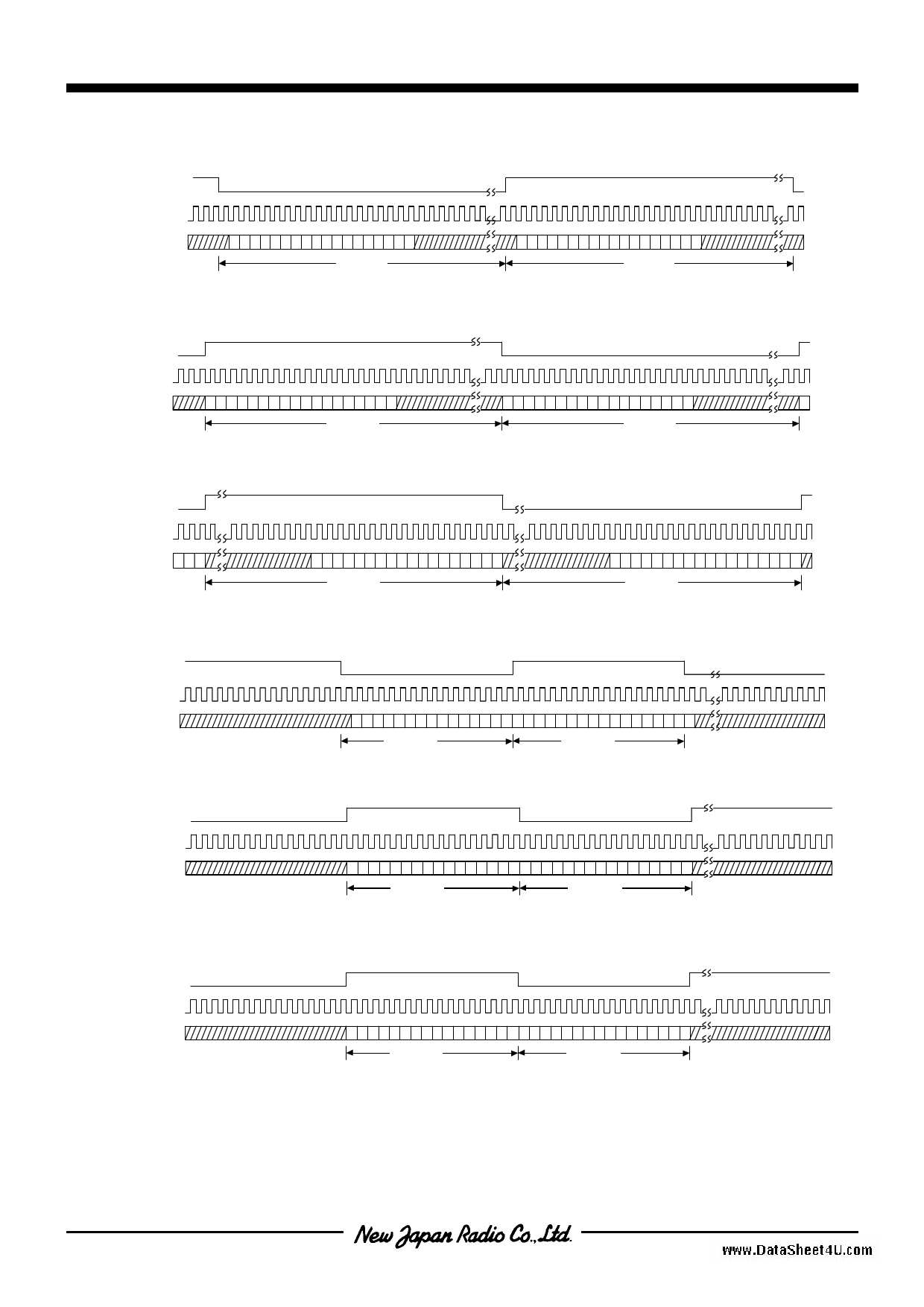

LRI, LRO

BCKI, BCKO

SDI, SDO

Left Channel

Right Channel

MSB LSB

1716151413121110 9 8 7 6 5 4 3 2 1 0

32Clocks

MSB LSB

1716151413121110 9 8 7 6 5 4 3 2 1 0

32Clocks

Fig.5-7 I2S Data Format 64fs, 18bit Data

LRI, LRO

BCKI, BCKO

SDI, SDO

Left Channel

Right Channel

MSB LSB

1716 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

32 Clocks

MSB LSB

17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

32 Clocks

Fig.5-8 Left-Justified Data Format 64fs, 18bit Data

17

LRI, LRO

BCKI, BCKO

SDI, SDO 2 1 0

Left Channel

Right Channel

MSB LSB

17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

32Clocks

MSB LSB

17 16 15 1413 12 11 10 9 8 7 6 5 4 3 2 1 0

32Clocks

Fig.5-9 Right-Justified Data Format 64fs, 18bit Data

LRI, LRO

BCKI, BCKO

SDI, SDO

LRI, LRO

BCKI, BCKO

SDI, SDO

Left Channel

Right Channel

MSB

LSB MSB

LSB

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

16 Clocks

16 Clocks

Fig.5-10 I2S Data Format 32fs, 16bit Data

Left Channel

Right Channel

MSB

LSB MSB

LSB

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

16 Clocks

16 Clocks

Fig.5-11 Left-Justified Data Format 32fs, 16bit Data

LRI, LRO

BCKI, BCKO

SDI, SDO

Left Channel

Right Channel

MSB

LSB MSB

LSB

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

16 Clocks

16 Clocks

Fig.5-12 Right-Justified Data Format 32fs, 16bit Data

Ver.2006-09-13

- 11 -

11 Page | ||

| Páginas | Total 17 Páginas | |

| PDF Descargar | [ Datasheet NJU26040.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| NJU26040 | Sound functions are possible to customization | JRC |

| NJU26040-07A | Digital Signal Processor | New Japan Radio |

| NJU26040-08B | Digital Signal Processor | New Japan Radio |

| NJU26040-09B | SRS WOW HD Processor | New Japan Radio |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |