|

|

PDF ADN4668 Data sheet ( Hoja de datos )

| Número de pieza | ADN4668 | |

| Descripción | 3V LVDS Quad CMOS Differential Line Receiver | |

| Fabricantes | Analog Devices | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ADN4668 (archivo pdf) en la parte inferior de esta página. Total 12 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

FEATURES

±15 kV ESD protection on receiver input pins

400 Mbps (200 MHz) switching rates

Flow-through pin configuration simplifies PCB layout

150 ps channel-to-channel skew (typical)

100 ps differential skew (typical)

2.7 ns maximum propagation delay

3.3 V power supply

High impedance outputs on power-down

Low power design (3 mW quiescent typical)

Interoperable with existing 5 V LVDS drivers

Accepts small swing (310 mV typical) differential

input signal levels

Supports open, short, and terminated input fail-safe

0 V to −100 mV threshold region

Conforms to TIA/EIA-644 LVDS standard

Industrial operating temperature range of −40°C to +85°C

Available in low profile TSSOP package

APPLICATIONS

Point-to-point data transmission

Multidrop buses

Clock distribution networks

Backplane receivers

GENERAL DESCRIPTION

The ADN4668 is a quad-channel CMOS, low voltage differential

signaling (LVDS) line receiver offering data rates of over 400 Mbps

(200 MHz) and ultralow power consumption. It features a flow-

through pin configuration for easy PCB layout and separation

of input and output signals.

The device accepts low voltage (310 mV typical) differential

input signals and converts them to a single-ended, 3 V TTL/CMOS

logic level.

3 V LVDS Quad CMOS

Differential Line Receiver

ADN4668

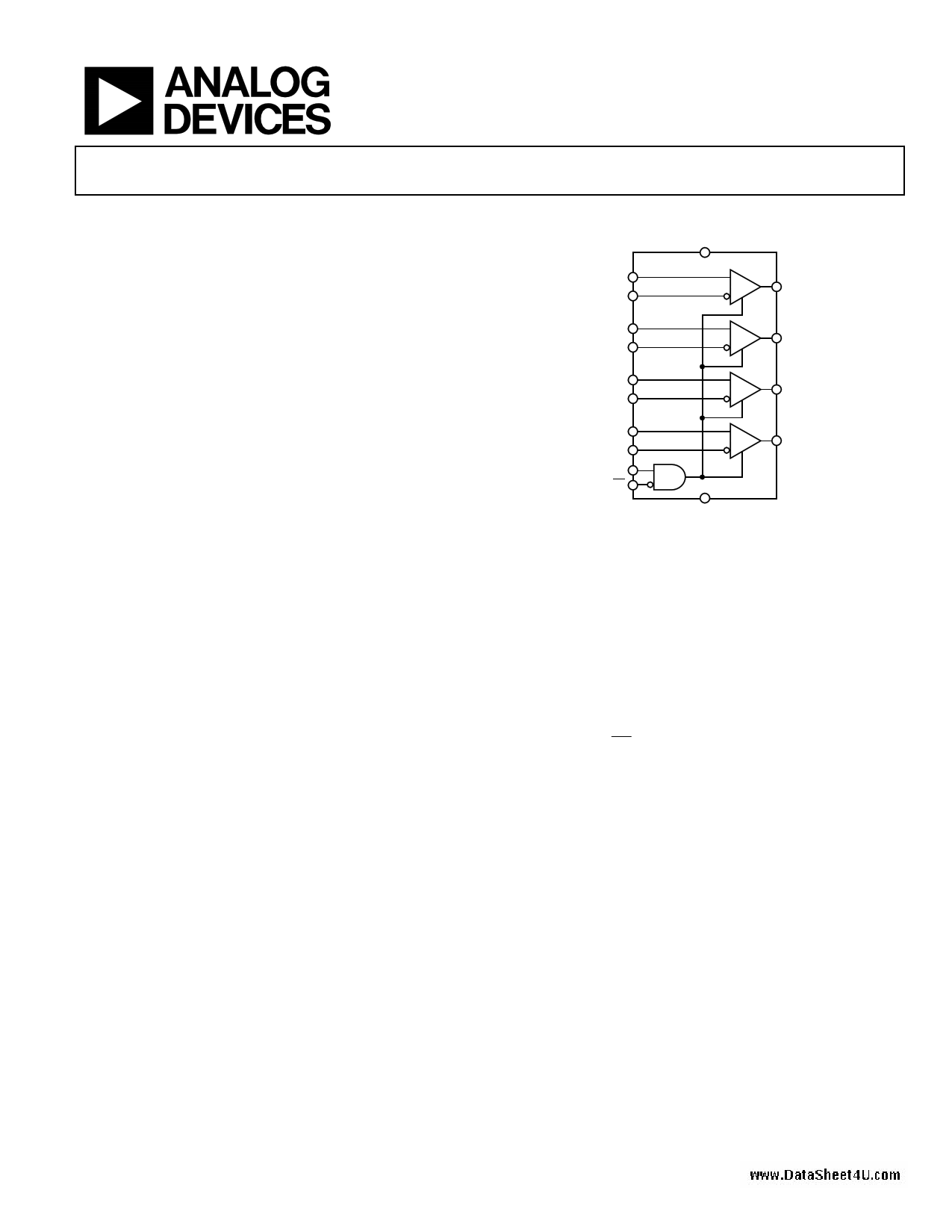

FUNCTIONAL BLOCK DIAGRAM

VCC

RIN1+

RIN1–

ADN4668

R1 ROUT1

RIN2+

RIN2–

R2 ROUT2

RIN3+

RIN3–

R3 ROUT3

RIN4+

RIN4–

EN

EN

R4 ROUT4

GND

Figure 1.

The ADN4668 also offers active-high and active-low enable/disable

inputs (EN and EN) that control all four receivers. They disable

the receivers and switch the outputs to a high impedance state.

This high impedance state allows the outputs of one or more

ADN4668s to be multiplexed together and reduces the quies-

cent power consumption to 3 mW typical.

The ADN4668 and its companion driver, the ADN4667, offer

a new solution to high speed, point-to-point data transmission

and a low power alternative to emitter-coupled logic (ECL) or

positive emitter-coupled logic (PECL).

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarksandregisteredtrademarksarethepropertyoftheirrespectiveowners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

Fax: 781.461.3113

©2008 Analog Devices, Inc. All rights reserved.

1 page

www.DataSheet4U.com

RINx–

RINx+

0V (DIFFERENTIAL) VID = 200mV

tPLHD

1.2V

tPHLD

80%

80%

1.3V

1.1V

VOH

ROUTx

1.5V

1.5V

20% 20%

tTLH

tTHL

VOL

Figure 3. Receiver Propagation Delay and Transition Time Waveforms

ADN4668

VCC

S1

SIGNAL

GENERATOR

RINx+

RINx–

EN

50Ω

EN

GND

RL

ROUTx

CL

NOTES

1. CL INCLUDES LOAD AND TEST JIG CAPACITANCE.

2. S1 CONNECTED TO VCC FOR tPZL AND tPLZ MEASUREMENTS.

3. S1 CONNECTED TO GND FOR tPZH AND tPHZ MEASUREMENTS.

Figure 4. Test Circuit for Receiver Enable/Disable Delay

EN WITH EN = GND

OR OPEN CIRCUIT

1.5V

1.5V

EN WITH EN = VCC

1.5V

ROUTx WITH VID = +100mV

tPHZ

0.5V

1.5V

tPZH

50%

ROUTx WITH VID = –100mV

tPLZ

0.5V

tPZL

Figure 5. Receiver Enable/Disable Delay Waveforms

50%

3V

0V

3V

0V

VOH

GND

VCC

VOL

Rev. 0 | Page 5 of 12

5 Page

www.DataSheet4U.com

THEORY OF OPERATION

The ADN4668 is a quad-channel line receiver for low voltage

differential signaling. It takes a differential input signal of 310 mV

typical and converts it into a single-ended 3 V TTL/CMOS logic

signal.

A differential current input signal, received via a transmission

medium such as a twisted pair cable, develops a voltage across

a terminating resistor, RT. This resistor is chosen to match the

characteristic impedance of the medium, typically around 100 Ω.

The differential voltage is detected by the receiver and converted

back into a single-ended logic signal.

When the noninverting receiver input, RINx+, is positive with

respect to the inverting input, RINx− (current flows through RT

from RINx+ to RINx−), ROUTx is high. When the noninverting receiver

input, RIN+, is negative with respect to the inverting input, RINx−

(current flows through RT from RINx− to RINx+), ROUTx is low.

Using the ADN4667 as a driver, the received differential current

is between ±2.5 mA and ±4.5 mA (±3.1 mA typical), developing

between ±250 mV and ±450 mV across a 100 Ω termination

resistor. The received voltage is centered around the receiver offset

of 1.2 V. In other words, the noninverting receiver input is typically

(1.2 V + [310 mV/2]) = 1.355 V, and the inverting receiver input

is (1.2 V − [310 mV/2]) = 1.045 V for Logic 1. For Logic 0, the

inverting and noninverting input voltages are reversed. Note that

because the differential voltage reverses polarity, the peak-to-peak

voltage swing across RT is twice the differential voltage.

Current-mode signaling offers considerable advantages over

voltage-mode signaling, such as the RS-422. The operating

ADN4668

current remains fairly constant with increased switching

frequency, whereas the operating current of voltage-mode

drivers increases exponentially in most cases. This increase is

caused by the overlap as internal gates switch between high and

low, causing currents to flow from VCC to ground. A current-mode

device reverses a constant current between its two outputs, with

no significant overlap currents.

This is similar to emitter-coupled logic (ECL) and positive emitter-

coupled logic (PECL), but without the high quiescent current of

ECL and PECL.

ENABLE INPUTS

The ADN4668 has active-high and active-low enable inputs that

put all the logic outputs into a high impedance state when disabled,

reducing device current consumption from 9 mA typical to 1 mA

typical. See Table 5 for a truth table of the enable inputs.

Table 5. Enable Inputs Truth Table

EN EN

RINx+

High Low or Open 1.045 V

High Low or Open 1.355 V

Any other combination X

of EN and EN

RINx−

1.355 V

1.045 V

X

ROUTx

0

1

High-Z

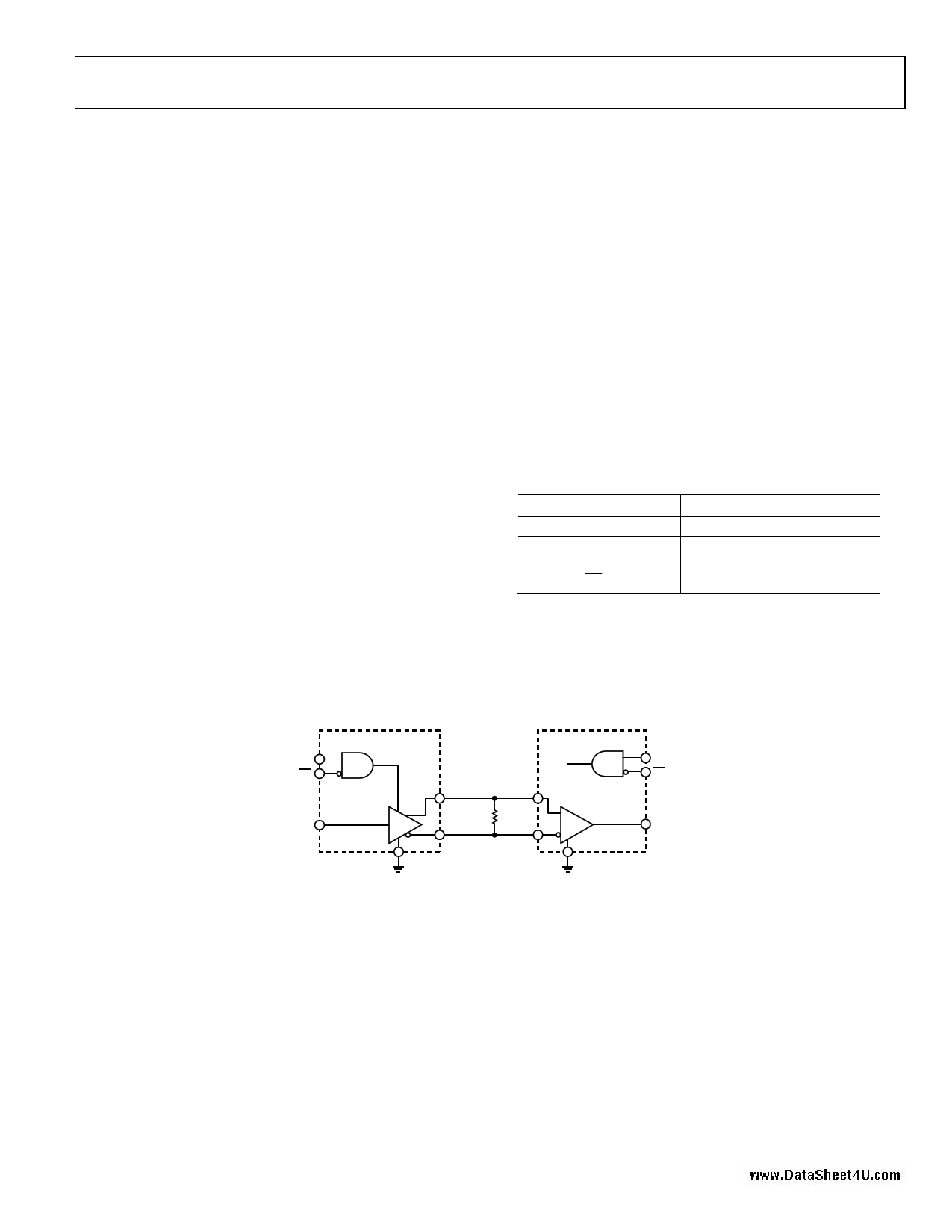

APPLICATIONS INFORMATION

Figure 22 shows a typical application for point-to-point data

transmission using the ADN4667 as the driver and the ADN4668

as the receiver.

1/4 ADN4667

EN

EN

DIN

GND

1/4 ADN4668

DOUTy+

DOUTy–

RINx+

RT

100Ω

RINx–

GND

Figure 22. Typical Application Circuit

EN

EN

DOUT

Rev. 0 | Page 11 of 12

11 Page | ||

| Páginas | Total 12 Páginas | |

| PDF Descargar | [ Datasheet ADN4668.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ADN4661 | High Speed Differential Driver | Analog Devices |

| ADN4662 | LVDS Differential Line Receiver | Analog Devices |

| ADN4663 | Dual 3V CMOS LVDS High Speed Differential Driver | ANALOG DEVICES |

| ADN4663 | LVDS High Speed Differential Driver | Analog Devices |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |