|

|

PDF ADT7460 Data sheet ( Hoja de datos )

| Número de pieza | ADT7460 | |

| Descripción | dB COOL Remote Thermal Controller and Fan Controller | |

| Fabricantes | Analog Devices | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ADT7460 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

a

dBCOOL™ Remote Thermal

ControllerandFanController

ADT7460*

www.datasFhEeAetT4uU.cRoEmS

Controls and Monitors up to 4 Fan Speeds

1 On-Chip and 2 Remote Temperature Sensors

Dynamic TMIN Control Mode Optimizes System Acoustics

Intelligently

Automatic Fan Speed Control Mode Controls System

Cooling Based on Measured Temperature

Enhanced Acoustic Mode Dramatically Reduces User

Perception of Changing Fan Speeds

Thermal Protection Feature via THERM Output

Monitors Performance Impact of Intel® Pentium® 4

Processor Thermal Control Circuit via THERM Input

2-Wire and 3-Wire Fan Speed Measurement

Limit Comparison of All Monitored Values

Meets SMBus 2.0 Electrical Specifications

(Fully SMBus 1.1 Compliant)

APPLICATIONS

Low Acoustic Noise PCs

Networking and Telecommunications Equipment

GENERAL DESCRIPTION

The ADT7460 dBCOOL controller is a thermal monitor and

multiple PWM fan controller for noise-sensitive applications

requiring active system cooling. It can monitor the temperature

of up to two remote sensor diodes, plus its own internal tem-

perature. It can measure and control the speed of up to four

fans so that they operate at the lowest possible speed for mini-

mum acoustic noise. The Automatic Fan Speed Control Loop

optimizes fan speed for a given temperature. A unique Dynamic

TMIN Control Mode enables the system thermals/acoustics

to be intelligently managed. The effectiveness of the system’s

thermal solution can be monitored using the THERM input.

The ADT7460 also provides critical Thermal Protection to the

system using the bidirectional THERM pin as an output to

prevent system or component overheating.

FUNCTIONAL BLOCK DIAGRAM

ADDR

SELECT ADDR EN SCL SDA SMBALERT

PWM1

PWM2

PWM3

TACH1

TACH2

TACH3

TACH4

THERM

VCC

D1+

D1–

D2+

D2–

+2.5VIN

PWM

REGISTERS

AND

CONTROLLERS

VCC TO ADT7460

BAND GAP

TEMP. SENSOR

ACOUSTIC

ENHANCEMENT

CONTROL

FAN SPEED

COUNTER

PERFORMANCE

MONITORING

SMBUS

ADDRESS

SELECTION

SERIAL BUS

INTERFACE

AUTOMATIC

FAN SPEED

CONTROL

ADDRESS

POINTER

REGISTER

DYNAMIC

TMIN

CONTROL

PWM

CONFIGURATION

REGISTERS

INTERRUPT

MASKING

THERMAL

PROTECTION

ADT7460

INPUT

SIGNAL

CONDITIONING

AND

ANALOG

MULTIPLEXER

10-BIT

ADC

BAND GAP

REFERENCE

GND

INTERRUPT

STATUS

REGISTERS

LIMIT

COMPARATORS

VALUE AND

LIMIT

REGISTERS

*Protected by U.S. Patent Nos. 6,188,189; 6,169,442; 6,097,239; 5,982,221; and 5,867,012. Other patents pending.

dBCOOL is a trademark of Analog Devices, Inc.

Intel and Pentium are registered trademarks of Intel Corp.

REV. 0

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its use,

nor for any infringements of patents or other rights of third parties that may

result from its use. No license is granted by implication or otherwise under any

patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700

www.analog.com

Fax: 781/326-8703

© Analog Devices, Inc., 2002

1 page

www.datasheet4u.com

PIN CONFIGURATION

SCL 1

16 SDA

GND 2

15 PWM1/XTO

VCC 3

14 2.5V/SMBALERT

TACH3 4 ADT7460 13 D1+

PWM2/SMBALERT

5

TOP VIEW

(Not to Scale)

12

D1–

TACH1 6

11 D2+

TACH2 7

10 D2–

PWM3/ADDRESS ENABLE 8

9 TACH4/ADDRESS SELECT/THERM

ADT7460

PIN FUNCTION DESCRIPTIONS

Pin No. Mnemonic Description

1 SCL

Digital Input (Open Drain). SMBus serial clock input. Requires SMBus pull-up.

2 GND Ground Pin for the ADT7460.

3 VCC

Power Supply. Can be powered by 3.3 V standby if monitoring in low power states is required. VCC is also

monitored through this pin. The ADT7460 can also be powered from a 5 V supply. Setting Bit 7 of

Configuration Register 1 (Reg. 0x40) rescales the VCC input attenuators to correctly measure a 5 V supply.

4

TACH3

Digital Input (Open Drain). Fan tachometer input to measure speed of FAN 3. Can be reconfigured as an

analog input (AIN3) to measure the speed of 2-wire fans.

5

PWM2

Digital Output (Open Drain). Requires 10 kΩ typical pull-up. Pulsewidth modulated output to control FAN 2 speed.

SMBALERT Digital Output (Open Drain). This pin may be reconfigured as an SMBALERT interrupt output to signal

out-of-limit conditions.

6

TACH1

Digital Input (Open Drain). Fan tachometer input to measure speed of FAN 1. Can be reconfigured as an analog

input (AIN1) to measure the speed of 2-wire fans.

7

TACH2

Digital Input (Open Drain). Fan tachometer input to measure speed of FAN 2. Can be reconfigured as an analog

input (AIN2) to measure the speed of 2-wire fans.

8

PWM3

Digital I/O (Open Drain). Pulsewidth modulated output to control FAN 3/4 speed. Requires 10 kΩ typical pull-up.

ADDRESS If pulled low on power-up, this places the ADT7460 into Address Select mode, and the state of Pin 9 will

ENABLE determine the ADT7460’s slave address.

9

TACH4

Digital Input (Open Drain). Fan tachometer input to measure speed of FAN 4. Can be reconfigured as an analog

input (AIN4) to measure the speed of 2-wire fans.

ADDRESS

SELECT

THERM

If in Address Select mode, this pin determines the SMBus device address.

Alternatively, the pin may be reconfigured as a bidirectional THERM pin. Can be used to time and monitor

assertions on the THERM input. For example, can be connected to the PROCHOT output of Intel’s Pentium 4

processor or to the output of a trip point temperature sensor. Can be used as an output to signal overtemperature

conditions.

10 D2–

Cathode Connection to Second Thermal Diode

11 D2+

Anode Connection to Second Thermal Diode

12 D1–

Cathode Connection to First Thermal Diode

13 D1+

Anode Connection to First Thermal Diode

14

+2.5VIN

Analog Input. Monitors +2.5 V supply, typically a chipset voltage.

SMBALERT Digital Output (Open Drain). This pin may be reconfigured as an SMBALERT interrupt output to signal

out-of-limit conditions.

15 PWM1/XTO Digital Output (Open Drain). Pulsewidth modulated output to control FAN 1 speed. Requires 10 kΩ typical pull-up.

16 SDA

Digital I/O (Open Drain). SMBus bidirectional serial data. Requires SMBus pull up.

REV. 0

–5–

5 Page

ADT7460

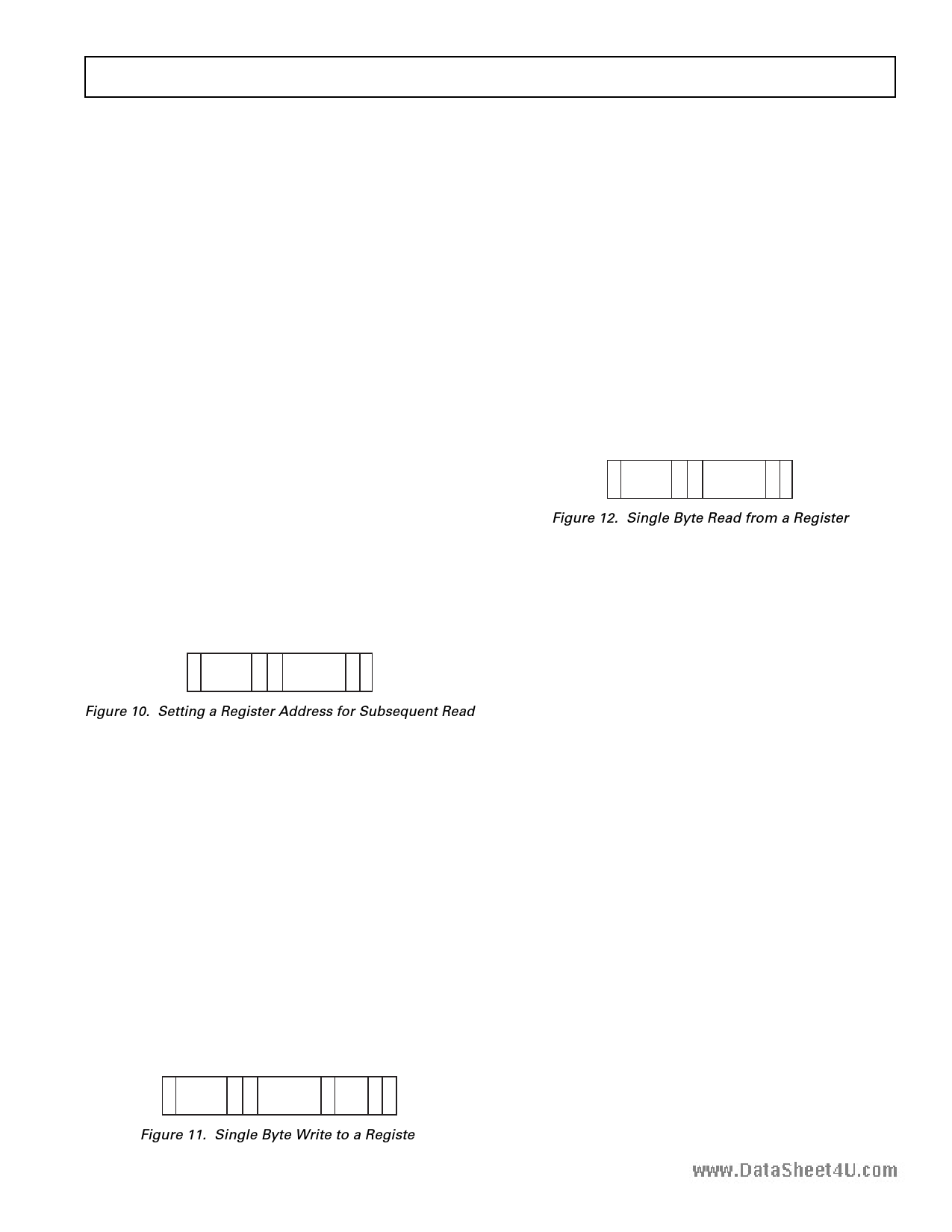

4. If it is required to perform several read or write operations in

succession, the master can send a repeat start condition

instead of a stop condition to begin a new operation.

ADT7460 WRITE OPERATIONS

The SMBus specification defines several protocols for different

types of read and write operations. The ones used in the

www.daAtaDsThe7e4t46u0.caorme discussed below. The following abbreviations are

used in the diagrams:

S – START

P – STOP

R – READ

W – WRITE

A – ACKNOWLEDGE

A – NO ACKNOWLEDGE

The ADT7460 uses the following SMBus write protocols:

Send Byte

In this operation, the master device sends a single command

byte to a slave device as follows:

1. The master device asserts a START condition on SDA.

2. The master sends the 7-bit slave address followed by the

write bit (low).

3. The addressed slave device asserts ACK on SDA.

4. The master sends a command code.

5. The slave asserts ACK on SDA.

6. The master asserts a STOP condition on SDA and the

transaction ends.

For the ADT7460, the send byte protocol is used to write a

register address to RAM for a subsequent single byte read from

the same address. This is illustrated in Figure 10.

12

3 4 56

S

SLAVE

ADDRESS

W

A

REGISTER

ADDRESS

AP

Figure 10. Setting a Register Address for Subsequent Read

If it is required to read data from the register immediately after

setting up the address, the master can assert a repeat start con-

dition immediately after the final ACK and carry out a single

byte read without asserting an intermediate stop condition.

Write Byte

In this operation, the master device sends a command byte and

one data byte to the slave device as follows:

1. The master device asserts a START condition on SDA.

2. The master sends the 7-bit slave address followed by the

write bit (low).

3. The addressed slave device asserts ACK on SDA.

4. The master sends a command code.

5. The slave asserts ACK on SDA.

6. The master sends a data byte.

7. The slave asserts ACK on SDA.

8. The master asserts a STOP condition on SDA to end the

transaction.

This is illustrated in Figure 11.

12

3 4 5 6 78

S

SLAVE

ADDRESS

W

A

REGISTER

ADDRESS

A DATA A P

Figure 11. Single Byte Write to a Register

ADT7460 READ OPERATIONS

The ADT7460 uses the following SMBus read protocols:

Receive Byte

This is useful when repeatedly reading a single register. The

register address needs to have been set up previously. In this

operation, the master device receives a single byte from a slave

device as follows:

1. The master device asserts a START condition on SDA.

2. The master sends the 7-bit slave address followed by the

read bit (high).

3. The addressed slave device asserts ACK on SDA.

4. The master receives a data byte.

5. The master asserts NO ACK on SDA.

6. The master asserts a STOP condition on SDA and the trans-

action ends.

In the ADT7460, the receive byte protocol is used to read a

single byte of data from a register whose address has previously

been set by a send byte or write byte operation.

12

3 4 56

S

SLAVE

ADDRESS

W

A

REGISTER

ADDRESS

AP

Figure 12. Single Byte Read from a Register

ALERT RESPONSE ADDRESS

Alert Response Address (ARA) is a feature of SMBus devices

that allows an interrupting device to identify itself to the host

when multiple devices exist on the same bus.

The SMBALERT output can be used as an interrupt output or

can be used as an SMBALERT. One or more outputs can be

connected to a common SMBALERT line connected to the

master. If a device’s SMBALERT line goes low, the following

procedure occurs:

1. SMBALERT is pulled low.

2. Master initiates a read operation and sends the Alert Response

Address (ARA = 0001 100). This is a general call address

that must not be used as a specific device address.

3. The device whose SMBALERT output is low responds to

the Alert Response Address, and the master reads its device

address. The address of the device is now known, and it can

be interrogated in the usual way.

4. If more than one device’s SMBALERT output is low, the

one with the lowest device address will have priority in

accordance with normal SMBus arbitration.

5. Once the ADT7460 has responded to the Alert Response

Address, the master must read the Status Registers and the

SMBALERT will only be cleared if the error condition has

gone away.

SMBUS TIMEOUT

The ADT7460 includes an SMBus Timeout feature. If there is

no SMBus activity for 35 ms, the ADT7460 assumes that the bus

is locked and releases the bus. This prevents the device from

locking or holding the SMBus expecting data. Some SMBus

controllers cannot handle the SMBus Timeout feature, so it

can be disabled.

CONFIGURATION REGISTER 1 – Register 0x40

<6> TODIS = 0; SMBus Timeout ENABLED (default)

<6> TODIS = 1; SMBus Timeout DISABLED

REV. 0

–11–

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet ADT7460.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ADT7460 | dB COOL Remote Thermal Controller and Fan Controller | Analog Devices |

| ADT7461 | Temperature Monitor | Analog Devices |

| ADT7461 | Temperature Monitor | ON Semiconductor |

| ADT7461A | Temperature Monitor | ON Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |