|

|

PDF LH540202 Data sheet ( Hoja de datos )

| Número de pieza | LH540202 | |

| Descripción | CMOS 1024 x 9 Asynchronous FIFO | |

| Fabricantes | Sharp Electrionic Components | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de LH540202 (archivo pdf) en la parte inferior de esta página. Total 18 Páginas | ||

|

No Preview Available !

LH540202

CMOS 1024 × 9 Asynchronous FIFO

FEATURES

• Fast Access Times: 15/20/25/35/50 ns

• Fast-Fall-Through Time Architecture Based on

CMOS Dual-Port SRAM Technology

• Input Port and Output Port Have Entirely

Independent Timing

• Expandable in Width and Depth

• Full, Half-Full, and Empty Status Flags

• Data Retransmission Capability

• TTL-Compatible I/O

• Pin and Functionally Compatible with Sharp LH5497

and with Am/IDT/MS7202

• Industrial Temperature Grade Option Currently

Available With Sharp LH5497H only

(Contact a Sharp Representative for More Information)

• Control Signals Assertive-LOW for Noise Immunity

• Packages:

28-Pin, 300-mil PDIP

28-Pin, 300-mil SOJ *

32-Pin PLCC

PIN CONNECTIONS

FUNCTIONAL DESCRIPTION

The LH540202 is a FIFO (First-In, First-Out) memory

device, based on fully-static CMOS dual-port SRAMtech-

nology, capable of storing up to 1024 nine-bit words. It

follows the industry-standard architecture and package

pinouts for nine-bit asynchronous FIFOs. Each nine-bit

LH540202 word may consist of a standard eight-bit byte,

together with a parity bit or a block-marking/framing bit.

The input and output ports operate entirely inde-

pendently of each other, unless the LH540202 becomes

either totally full or else totally empty. Data flow at a port

is initiated by asserting either of two asynchronous, as-

sertive-LOW control inputs: Write (W) for data entry at the

input port, or Read (R) for data retrieval at the output port.

Full, Half-Full, and Empty status flags monitor the

extent to which the internal memory has been filled. The

system may make use of these status outputs to avoid

the risk of data loss, which otherwise might occur either

by attempting to write additional words into an already-full

LH540202, or by attempting to read additional words from

an already-empty LH540202. When an LH540202 is

operating in a depth-cascaded configuration, the Half-Full

Flag is not available.

28-PIN PDIP

28-PIN SOJ * W 1

D8 2

D3 3

D2 4

D1 5

D0 6

XI 7

FF 8

Q0 9

Q1 10

Q2 11

Q3 12

Q8 13

VSS 14

TOP VIEW

28 VCC

27 D4

26 D5

25 D6

24 D7

23 FL/RT

22 RS

21 EF

20 XO/HF

19 Q7

18 Q6

17 Q5

16 Q4

15 R

540202-2D

32-PIN PLCC

TOP VIEW

4 3 2 1 32 31 30

D2 5

D1 6

D0 7

XI 8

29 D6

28 D7

27 NC

26 FL/RT

FF 9

25 RS

Q0 10

24 EF

Q1 11

23 XO/HF

NC 12

22 Q7

Q2 13

21 Q6

14 15 16 17 18 19 20

NOTE: * = No external electrical connections are allowed.

540202-3D

Figure 1. Pin Connections for PDIP and

SOJ * Packages

Figure 2. Pin Connections for PLCC Package

* This is a final data sheet; except that all references to the SOJ package have Advance Information status.

1

1 page

CMOS 1024 × 9 Asynchronous FIFO

LH540202

OPERATIONAL MODES

Standalone Configuration

When depth cascading is not required for a given

application, the LH540202 is placed in standalone mode

by tying the Expansion In input (XI) to ground. This

input is internally sampled during a reset operation. (See

Table 1.)

Width Expansion

Word-width expansion is implemented by placing

multiple LH540202 devices in parallel. Each LH540202

should be configured for standalone mode. In this ar-

rangement, the behavior of the status flags is identical for

all devices; so, in principle, a representative value for

each of these flags could be derived from any one device.

In practice, it is better to derive ‘composite’ flag values

using external logic, since there may be minor speed

variations between different actual devices. (See Figures

4, 5, and 6.)

WRITE

DATA IN

D0 - D8

FULL FLAG

RESET

HF

WR

9

FF

LH540202

RS

9

EF

RT

XI

READ

DATA OUT

Q0 - Q8

EMPTY FLAG

RETRANSMIT

Figure 4. Standalone FIFO

(1024 × 9)

540202-17

DATA IN

D0 - D17

18

WRITE

FULL FLAG

RESET

HF

9

W

FF

LH540202

RS

R

RT

9

XI

HF

9

W

LH540202

RS

XI

EF

R

RT

9

Figure 5. FIFO Word-Width Expansion

(1024 × 18)

EMPTY FLAG

READ

RETRANSMIT

18 DATA OUT

Q0 - Q17

540202-18

5

5 Page

CMOS 1024 × 9 Asynchronous FIFO

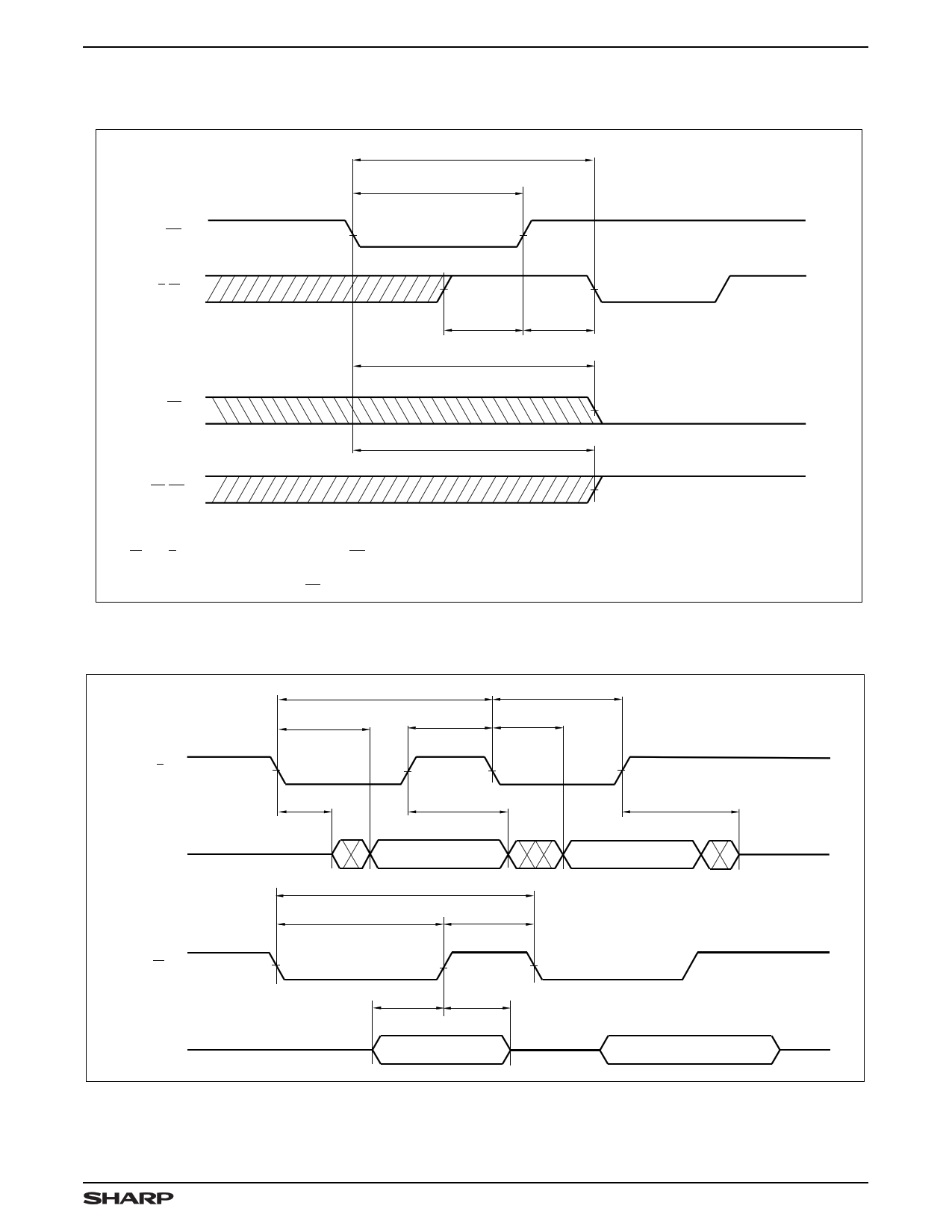

TIMING DIAGRAMS

tRSC

tRS

RS

R,W

t RRSS

t WRSS

tEFL

tRSR

EF

tFFH , tHFH

FF,HF

NOTES:

1. tRSC = tRS + tRSR.

2. W and R ≥ VIH around the rising edge of RS.

3. The Data Out pins (D0 - D8) are forced into a

high-impedance state whenever EF = LOW.

Figure 10. Reset Timing

R

Q0 - Q8

W

D0 - D8

tRC

t A tRR

t RPW

tA

t RLZ

t DV

VALID DATA OUT

t WPW

t WC

t WR

t RHZ

VALID DATA OUT

t DS t DH

VALID DATA IN

VALID DATA IN

Figure 11. Asynchronous Write and Read Operation

LH540202

540202-14

540202-5

11

11 Page | ||

| Páginas | Total 18 Páginas | |

| PDF Descargar | [ Datasheet LH540202.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| LH540202 | CMOS 1024 x 9 Asynchronous FIFO | Sharp Electrionic Components |

| LH540203 | CMOS 2048 x 9 Asynchronous FIFO | Sharp Electrionic Components |

| LH540204 | CMOS 4096 x 9 Asynchronous FIFO | Sharp Electrionic Components |

| LH540205 | CMOS 8192 x 9 Asynchronous FIFO | Sharp Electrionic Components |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |