|

|

PDF ADN2805 Data sheet ( Hoja de datos )

| Número de pieza | ADN2805 | |

| Descripción | 1.25 Gbps Clock and Data Recovery IC | |

| Fabricantes | Analog Devices | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ADN2805 (archivo pdf) en la parte inferior de esta página. Total 17 Páginas | ||

|

No Preview Available !

Data Sheet

FEATURES

Locks to 1.25 Gbps NRZ serial data input

Patented clock recovery architecture

No reference clock required

Loss-of-lock indicator

I2C interface to access optional features

Single-supply operation: 3.3 V

Low power: 390 mW typical

5 mm × 5 mm 32-lead LFCSP, Pb free

APPLICATIONS

GbE line card

1.25 Gbps Clock and Data Recovery IC

ADN2805

GENERAL DESCRIPTION

The ADN2805 provides the receiver functions of quantization

and clock and data recovery for 1.25 Gbps. The ADN2805

automatically locks to all data rates without the need for an

external reference clock or programming. All SONET jitter

requirements are met, including jitter transfer, jitter generation,

and jitter tolerance.

All specifications are specified for −40°C to +85°C ambient

temperature, unless otherwise noted. The ADN2805 is available

in a compact 5 mm × 5 mm 32-lead LFCSP.

FUNCTIONAL BLOCK DIAGRAM

REFCLKP/REFCLKN

(OPTIONAL)

LOL

CF1

CF2 VCC VEE

PIN

NIN

VREF

FREQUENCY

DETECT

LOOP

FILTER

BUFFER

PHASE

SHIFTER

PHASE

DETECT

LOOP

FILTER

VCO

DATA

RE-TIMING

2

2

DATAOUTP/

DATAOUTN

CLKOUTP/

CLKOUTN

Figure 1.

ADN2805

Rev. B

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarksandregisteredtrademarksarethepropertyoftheirrespectiveowners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

Fax: 781.461.3113 ©2008–2012 Analog Devices, Inc. All rights reserved.

1 page

ADN2805

Data Sheet

OUTPUT AND TIMING SPECIFICATIONS

Table 3.

Parameter

LVDS OUTPUT CHARACTERISTICS

CLKOUTP/CLKOUTN, DATAOUTP/DATAOUTN

Differential Output Swing

Output Offset Voltage

Output Impedance

LVDS Outputs Timing

Rise Time

Fall Time

Setup Time

Hold Time

I2C® INTERFACE DC CHARACTERISTICS

Input High Voltage

Input Low Voltage

Input Current

Output Low Voltage

I2C INTERFACE TIMING

SCK Clock Frequency

SCK Pulse Width High

SCK Pulse Width Low

Start Condition Hold Time

Start Condition Setup Time

Data Setup Time

Data Hold Time

SCK/SDA Rise/Fall Time

Stop Condition Setup Time

Bus Free Time Between a Stop and a Start

REFCLK CHARACTERISTICS

Input Voltage Range

Input Low Voltage

Input High Voltage

Minimum Differential Input Drive

Reference Frequency

Required Accuracy

LVTTL DC INPUT CHARACTERISTICS

Input High Voltage

Input Low Voltage

Input High Current

Input Low Current

LVTTL DC OUTPUT CHARACTERISTICS

Output High Voltage

Output Low Voltage

Conditions

Min

VOD (see Figure 3)

VOS (see Figure 3)

Differential

20% to 80%

80% to 20%

TS (see Figure 2), GbE

TH (see Figure 2), GbE

LVCMOS

VIH

VIL

VIN = 0.1 VCC or VIN = 0.9 VCC

VOL, IOL = 3.0 mA

See Figure 10

tHIGH

tLOW

tHD;STA

tSU;STA

tSU;DAT

tHD;DAT

tR/tF

tSU;STO

tBUF

Optional lock-to-REFCLK mode

@ REFCLKP or REFCLKN

VIL

VIH

240

1125

360

360

0.7 VCC

−10.0

600

1300

600

600

100

300

20 + 0.1 Cb1

600

1300

10

VIH

VIL

IIH, VIN = 2.4 V

IIL, VIN = 0.4 V

VOH, IOH = −2.0 mA

VOL, IOL = 2.0 mA

2.0

−5

2.4

1 Cb = total capacitance of one bus line in pF. If mixed with high speed mode devices, faster fall times are allowed.

Typ Max

300

1200

100

400

1275

115 220

115 220

400 440

400 440

0.3 VCC

+10.0

0.4

400

300

0

VCC

100

160

100

0.8

5

0.4

Unit

mV

mV

Ω

ps

ps

ps

ps

V

V

μA

V

kHz

ns

ns

ns

ns

ns

ns

ns

ns

ns

V

V

mV p-p

MHz

ppm

V

V

μA

μA

V

V

Rev. B | Page 4 of 16

5 Page

ADN2805

Data Sheet

THEORY OF OPERATION

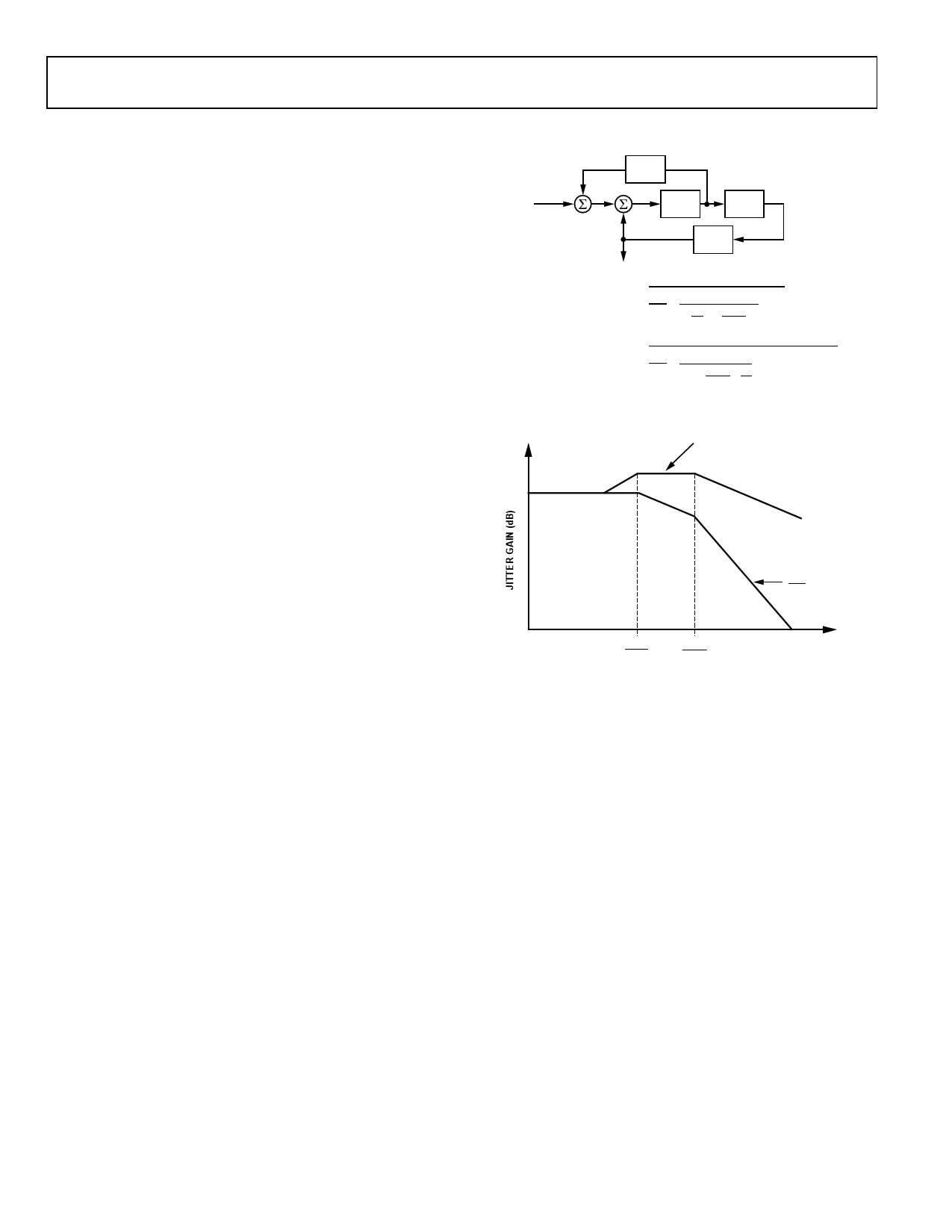

The ADN2805 is a delay- and phase-locked loop circuit for

clock recovery and data retiming from an NRZ encoded data

stream. The phase of the input data signal is tracked by two

separate feedback loops that share a common control voltage. A

high speed delay-locked loop path uses a voltage controlled

phase shifter to track the high frequency components of input

jitter. A separate phase control loop, comprised of the VCO,

tracks the low frequency components of input jitter. The initial

frequency of the VCO is set by yet a third loop, which compares

the VCO frequency with the input data frequency and sets the

coarse tuning voltage. The jitter tracking phase-locked loop

(PLL) controls the VCO by the fine-tuning control.

The delay and phase loops together track the phase of the input

data signal. For example, when the clock lags input data, the

phase detector drives the VCO to a higher frequency and

increases the delay through the phase shifter; both of these

actions serve to reduce the phase error between the clock and

data. The faster clock picks up phase, while simultaneously, the

delayed data loses phase. Because the loop filter is an integrator,

the static phase error is driven to zero.

Another view of the circuit is that the phase shifter implements

the zero required for frequency compensation of a second-order

phase-locked loop, and this zero is placed in the feedback path

and, thus, does not appear in the closed-loop transfer function.

Jitter peaking in a conventional second-order phase-locked loop

is caused by the presence of this zero in the closed-loop transfer

function. Because this circuit has no zero in the closed-loop

transfer, jitter peaking is minimized.

The delay and phase loops together simultaneously provide

wideband jitter accommodation and narrow-band jitter

filtering. The linearized block diagram in Figure 11 shows that

the jitter transfer function, Z(s)/X(s), is second-order low-pass,

providing excellent filtering. Note that the jitter transfer has no

zero, unlike an ordinary second-order phase-locked loop. This

means that the main PLL has virtually zero jitter peaking (see

Figure 12). This makes this circuit ideal for signal regenerator

applications where jitter peaking in a cascade of regenerators

can contribute to hazardous jitter accumulation.

The error transfer, e(s)/X(s), has the same high-pass form as an

ordinary phase-locked loop. This transfer function is free to be

optimized to give excellent wideband jitter accommodation

because the jitter transfer function, Z(s)/X(s), provides the

narrow-band jitter filtering.

INPUT X(s)

DATA

psh

e(s)

d/sc

o/s

Z(s)

RECOVERED

CLOCK

1/n

d = PHASE DETECTOR GAIN

o = VCO GAIN

c = LOOP INTEGRATOR

psh = PHASE SHIFTER GAIN

n = DIVIDE RATIO

JITTER TRANSFER FUNCTION

Z(s)

X(s)

=

s2

cn

do

+

1

sn

psh

o

+

1

TRACKING ERROR TRANSFER FUNCTION

e(s)

X(s)

=

s2

+

s2

sd

psh

c

+

do

cn

Figure 11. ADN2805 PLL/DLL Architecture

JITTER PEAKING

IN ORDINARY PLL

ADN2805

Z(s)

X(s)

o

n psh

d psh

c

FREQUENCY (kHz)

Figure 12. ADN2805 Jitter Response vs. Conventional PLL

The delay and phase loops contribute to overall jitter accom-

modation. At low frequencies of input jitter on the data signal,

the integrator in the loop filter provides high gain to track large

jitter amplitudes with small phase error. In this case, the VCO is

frequency modulated and jitter is tracked as in an ordinary

phase-locked loop. The amount of low frequency jitter that can

be tracked is a function of the VCO tuning range. A wider

tuning range gives larger accommodation of low frequency

jitter. The internal loop control voltage remains small for small

phase errors; therefore, the phase shifter remains close to the

center of its range and thus contributes little to the low

frequency jitter accommodation.

At medium jitter frequencies, the gain and tuning range of the

VCO are not large enough to track input jitter. In this case, the

VCO control voltage becomes large and saturates, and the VCO

frequency dwells at either one extreme of its tuning range or at

the other. The size of the VCO tuning range, therefore, has only

a small effect on the jitter accommodation. As such, the delay-

locked loop control voltage is larger, and, consequently, the

phase shifter takes on the burden of tracking the input jitter.

The phase shifter range, in UI, can be seen as a broad plateau on

the jitter tolerance curve. The phase shifter has a minimum

range of 2 UI at all data rates.

Rev. B | Page 10 of 16

11 Page | ||

| Páginas | Total 17 Páginas | |

| PDF Descargar | [ Datasheet ADN2805.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ADN2804 | Clock and Data Recovery IC | Analog Devices |

| ADN2805 | 1.25 Gbps Clock and Data Recovery IC | Analog Devices |

| ADN2806 | Clock and Data Recovery IC | Analog Devices |

| ADN2807 | Clock and Data Recovery IC | Analog Devices |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |