|

|

PDF P4C167L Data sheet ( Hoja de datos )

| Número de pieza | P4C167L | |

| Descripción | ULTRA HIGH SPEED 16K X 1 STATIC CMOS RAMS | |

| Fabricantes | Pyramid Semiconductor Corporation | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de P4C167L (archivo pdf) en la parte inferior de esta página. Total 10 Páginas | ||

|

No Preview Available !

P4C167/P4C167L

ULTRA HIGH SPEED 16K X 1

STATIC CMOS RAMS

FEATURES

Full CMOS, 6T Cell

High Speed (Equal Access and Cycle Times)

– 10/12/15/20/25 ns (Commercial)

– 12/15/20/25/35 ns (Industrial)

– 15/20/25/35/45 ns (Military)

Low Power Operation

www.DataSheet4U.com

Single 5V±10% Power Supply

Data Retention with 2.0V Supply (P4C167L

Military)

Separate Data I/O

Three-State Output

TTL Compatible Output

Fully TTL Compatible Inputs

Standard Pinout (JEDEC Approved)

– 20-Pin 300 mil DIP

– 20-Pin 300 mil SOJ

– 20-Pin LCC

DESCRIPTION

The P4C167/L are 16,384-bit high speed static RAMs or-

ganized as 16K x 1. The CMOS memories require no clocks

or refreshing and have equal access and cycle times. The

RAMs operate from a single 5V ± 10% tolerance power

supply. Data integrity is maintained for supply voltages

down to 2.0V, typically drawing 10µA.

Access times as fast as 10 nanoseconds are available,

greatly enhancing system speeds. CMOS reduces power

consumption to low levels.

The P4C167/L are available in 20-pin 300 mil DIP, 20-pin

300 mil SOJ, and 20-pin LCC packages providing excel-

lent board level densities.

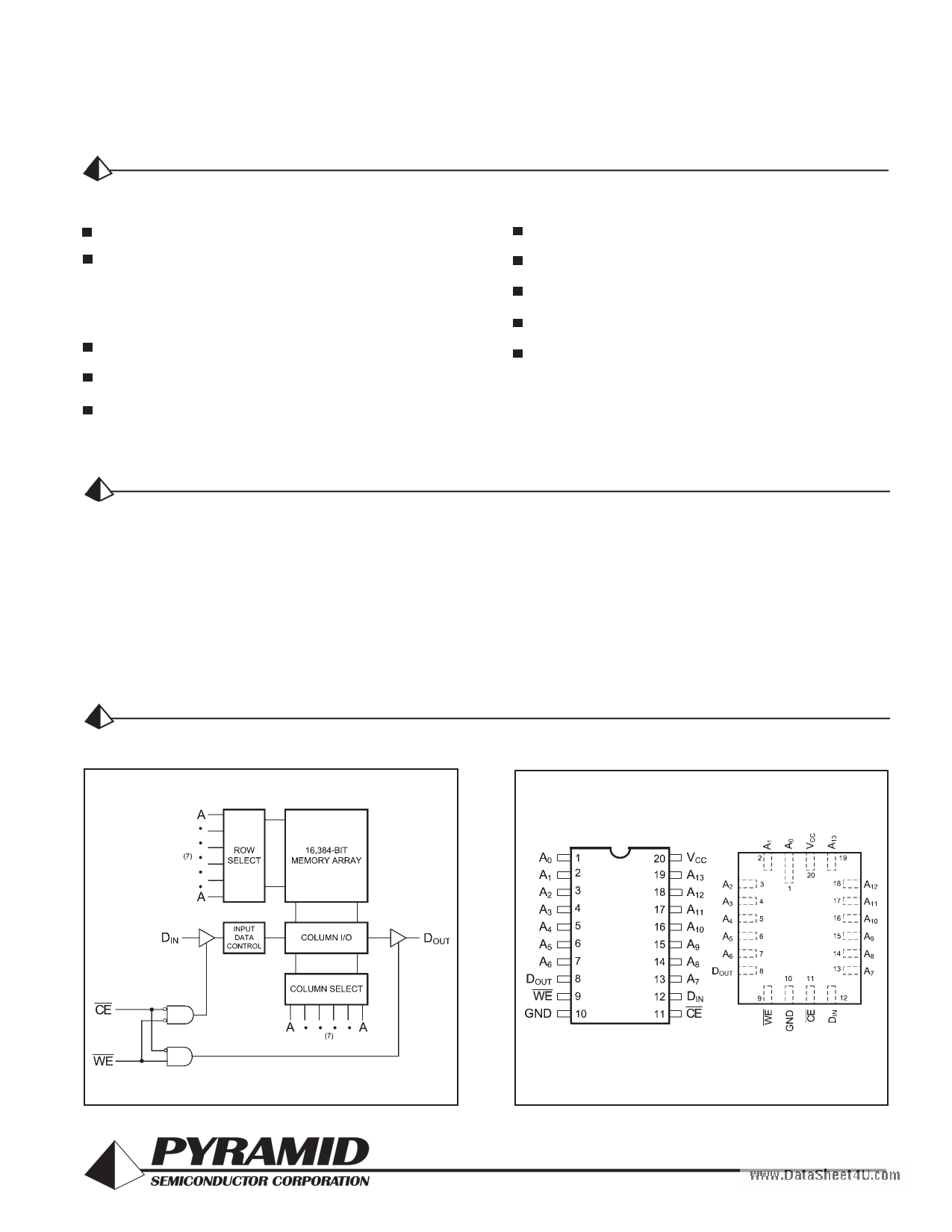

FUNCTIONAL BLOCK DIAGRAM

PIN CONFIGURATIONS

DIP (P2, C6)

SOJ (J2) SIMILAR

LCC (L9)

Document # SRAM106 REV A

Revised October 2005

1

1 page

P4C167

AC CHARACTERISTICS - WRITE CYCLE

(VCC = 5V ± 10%, All Temperature Ranges)(2)

Symbol

Parameter

–10 –12 –15 –20 –25 –35 –45

Min Max Min Max Min Max Min Max Min Max Min Max Min Max

tWC Write Cycle Time 10 12 15 20 25 35 45

tCW Chip Enable Time 8 10 2 15 20 25 30

to End of Write

tAW Address Valid to 8

End of Write

10 12 15 20 25 30

tAS

tWP

www.DataSheet4tAUH.com

Address Set-up

Time

Write Pulse Width

Address Hold Time

from End of Write

0

8

0

0 0 0000

10 12 15 20 25 30

0 0 0000

tDW Data Valid to End 6

of Write

7 10 13 15 20 25

tDH Data Hold Time

0

0

0

0

0

0

0

tWZ Write Enable to

Output in High Z

6 7 8 12 15 17 20

tOW Output Active from 0 0 0 0 0 0 0

End of Write

Unit

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

TIMING WAVEFORM OF WRITE CYCLE NO. 1 (WE CONTROLLED)(9)

Notes:

9. CE and WE must be LOW for WRITE cycle.

10. If CE goes HIGH simultaneously with WE HIGH, the output remains

in a high impedance state.

11. Write Cycle Time is measured from the last valid address to the first

transition address.

Document # SRAM106 REV A

Page 5 of 10

5 Page | ||

| Páginas | Total 10 Páginas | |

| PDF Descargar | [ Datasheet P4C167L.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| P4C167 | ULTRA HIGH SPEED 16K X 1 STATIC CMOS RAMS | Pyramid Semiconductor Corporation |

| P4C167L | ULTRA HIGH SPEED 16K X 1 STATIC CMOS RAMS | Pyramid Semiconductor Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |