|

|

PDF EDR2518ABSE Data sheet ( Hoja de datos )

| Número de pieza | EDR2518ABSE | |

| Descripción | 288M bits Direct Rambus DRAM | |

| Fabricantes | Elpida Memory | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de EDR2518ABSE (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

PRELIMINARY DATA SHEET

288M bits Direct Rambus DRAM

EDR2518ABSE (512K words × 18 bits × 32s banks)

Description

The EDR2518AB (Direct RDRAM) is a general

purpose high-performance memory device suitable for

use in a broad range of applications including

computer memory, graphics, video, and any other

application where high bandwidth and low latency are

required.

The EDR2518AB is 1066MHz 288Mbits Direct Rambus

DRAM (RDRAM), organized as 16M words by 18 bits.

The use of Rambus Signaling Level (RSL) technology

permits 800MHz to 1066MHz transfer rates while using

www.DataSchoenevt4eUn.tcioonmal system and board design technologies.

Direct RDRAM devices are capable of sustained data

transfers at 0.9375ns per two bytes (7.5ns per sixteen

bytes).

The architecture of the Direct RDRAM devices allows

the highest sustained bandwidth for multiple,

simultaneous randomly addressed memory

transactions.

The separate control and data buses with independent

row and column control yield over 95% bus efficiency.

The Direct RDRAM devices 32 banks support up to

four simultaneous transactions.

System oriented features for mobile, graphics and

large memory systems include power management,

byte masking.

It is offered in a CSP horizontal package suitable for

desktop as well as low-profile add-in card and mobile

applications. Direct RDRAM devices operate from a

2.5V supply.

Features

• Highest sustained bandwidth per DRAM device

— 2.1 GB/s sustained data transfer rate

— Separate control and data buses for maximized

efficiency

— Separate row and column control buses for easy

scheduling and highest performance

— 32 banks: four transactions can take place

simultaneously at full bandwidth data rates

• Low latency features

— Write buffer to reduce read latency

— 3 precharge mechanisms for controller flexibility

— Interleaved transactions

• Advanced power management:

— Multiple low power states allows flexibility in power

consumption versus time to active state

— Power-down self-refresh

• Organization: 2K bytes pages and 32 banks, x 18

• Uses Rambus Signaling Level (RSL) for up to

1066MHz operation

• FBGA (µ BGA) package is Sn-Pb or lead free

solder (Sn-Ag-Cu)

Document No. E0260E40 (Ver. 4.0)

Date Published April 2003 (K) Japan

URL: http://www.elpida.com

Elpida Memory, Inc. 2002-2003

1 page

EDR2518ABSE

Block Diagram

DQB8..DQB0

9

RQ7..RQ5 or

ROW2..ROW0

3

1:8 Demux

CTM CTMN SCK, CMD SIO0, SIO1 CFM CFMN

22

RCLK

RQ4..RQ0 or

COL4..COL0

5

1:8 Demux

DQA8..DQA0

9

RCLK

Packet Decode

ROWR

ROWA

11 5 5 9

ROP DR BR

AV

R

TCLK

Control Registers

RCLK

COLX

655

Packet Decode

COLC

555

7

REFR Power Modes DEVID

XOP DX BX COP DC BC

MS

C

COLM

88

MB MA

Match

DM

Mux

Row Decode

PRER

ACT

www.DataSheet4U.com

Sense Amp DRAM Core

64x72

64x72

512x128x144

Internal DQB Data Path

72

Bank 0

72 Bank 1

99

•

•

•

Bank 2

•

•

•

Bank 13

9 Bank 14

Bank 15

Match

XOP Decode

PREX

Match

Write

Buffer

Mux Mux

Column Decode & Mask

PREC

RD, WR

64x72

72 Internal DQA Data Path

72

• 99

•

•

9

9

•

•

9•

Bank 16

Bank 17

Bank 18

•

•

•

Bank 29

Bank 30

Bank 31

9

•

•

•9

Preliminary Data Sheet E0260E40 (Ver. 4.0)

5

5 Page

EDR2518ABSE

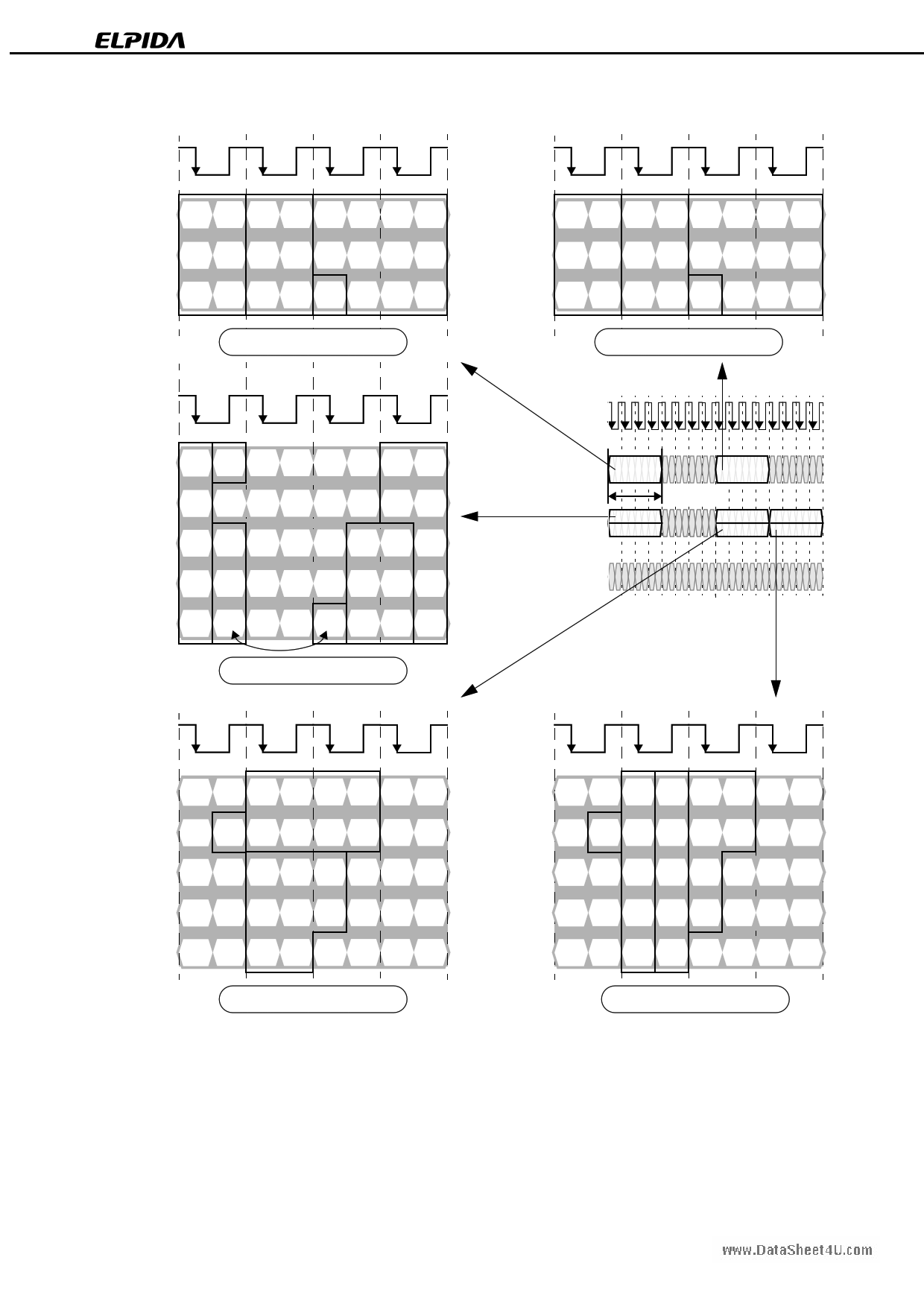

Figure 2-1 Packet Formats

T0 T1 T2 T3

CTM/CFM

T8 T9 T10 T11

CTM/CFM

ROW2 DR4T DR2 BR0 BR3 RsvR R8 R5 R2

ROW1 DR4F DR1 BR1 BR4 RsvR R7 R4 R1

ROW0 DR3 DR0 BR2 RsvB AV=1 R6 R3 R0

ROW2 DR4T DR2 BR0 BR3 ROP10ROP8ROP5ROP2

ROW1 DR4F DR1 BR1 BR4 ROP9ROP7ROP4ROP1

ROW0 DR3 DR0 BR2 RsvB AV=0 ROP6ROP3ROP0

ROWA Packet

CTM/CFM

T0

www.DataSheet4U.com

COL4 DC4 S=1

T1

T2 T3

C6 C4

COL3 DC3

C5 C3

COL2 DC2 COP1

RsvB BC2 C2

COL1 DC1 COP0

BC4 BC1 C1

COL0 DC0 COP2

COP3 BC3 BC0 C0

CTM/CFM

T8

COLC Packet

T9 T10

T11

ROWR Packet

T0 T1 T2 T3 T4 T5 T6 T7 T8 T9 T10 T11T12 T13 T14 T15

CTM/CFM

ROW2

..ROW0

COL4

..COL0

ACT a0

PRER c0

WR b1

tPACKET

MSK (b1) PREX d0

DQA8..0

DQB8..0

T12 T13 T14 T15

CTM/CFM

COL4

COL3

COL2

COL1

COL0

Note1

S=1 MA7 MA5 MA3 MA1

M=1 MA6 MA4 MA2 MA0

MB7 MB4 MB1

MB6 MB3 MB0

MB5 MB2

COL4

COL3

COL2

COL1

COL0

Note2

S=1 DX4 XOP4 RsvB BX1

M=0 DX3 XOP3 BX4 BX0

DX2 XOP2 BX3

DX1 XOP1 BX2

DX0 XOP0

COLM Packet

COLX Packet

Notes 1. The COLM is associated with a previous COLC, and is aligned with the present COLC, indicated

by the Start bit (S=1) position.

2. The COLX is aligned with the present COLC, indicates by the Start bit (S=1) position.

Preliminary Data Sheet E0260E40 (Ver. 4.0)

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet EDR2518ABSE.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| EDR2518ABSE | 288M bits Direct Rambus DRAM | Elpida Memory |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |