|

|

PDF DS2460 Data sheet ( Hoja de datos )

| Número de pieza | DS2460 | |

| Descripción | SHA-1 Coprocessor | |

| Fabricantes | Dallas Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de DS2460 (archivo pdf) en la parte inferior de esta página. Total 9 Páginas | ||

|

No Preview Available !

3/10

Abridged Data Sheet

DS2460

SHA-1 Coprocessor with EEPROM

www.maxim-ic.com

GENERAL DESCRIPTION

The DS2460 SHA-1 Coprocessor with EEPROM is a

hardware implementation of the ISO/IEC 10118-3

Secure Hash Algorithm (SHA-1), eliminating the need

to develop software to perform the complex SHA

computation required for authenticating SHA devices

and for performing the validation of digitally signed

service data. The DS2460 communicates with a

microcontroller through the popular I²C interface.

Applications include hosts of access control and

electronic payment systems for token authentication

and service data validation as well as generation of

one-time-use encryption keys for short message

encryption and decryption for messages not exceed-

ing the length of a SHA-1 result, which is 20 bytes.

APPLICATIONS

License Management

Secure Feature Control

System Authentication

Clone Prevention

Door Locks

Utility Meters

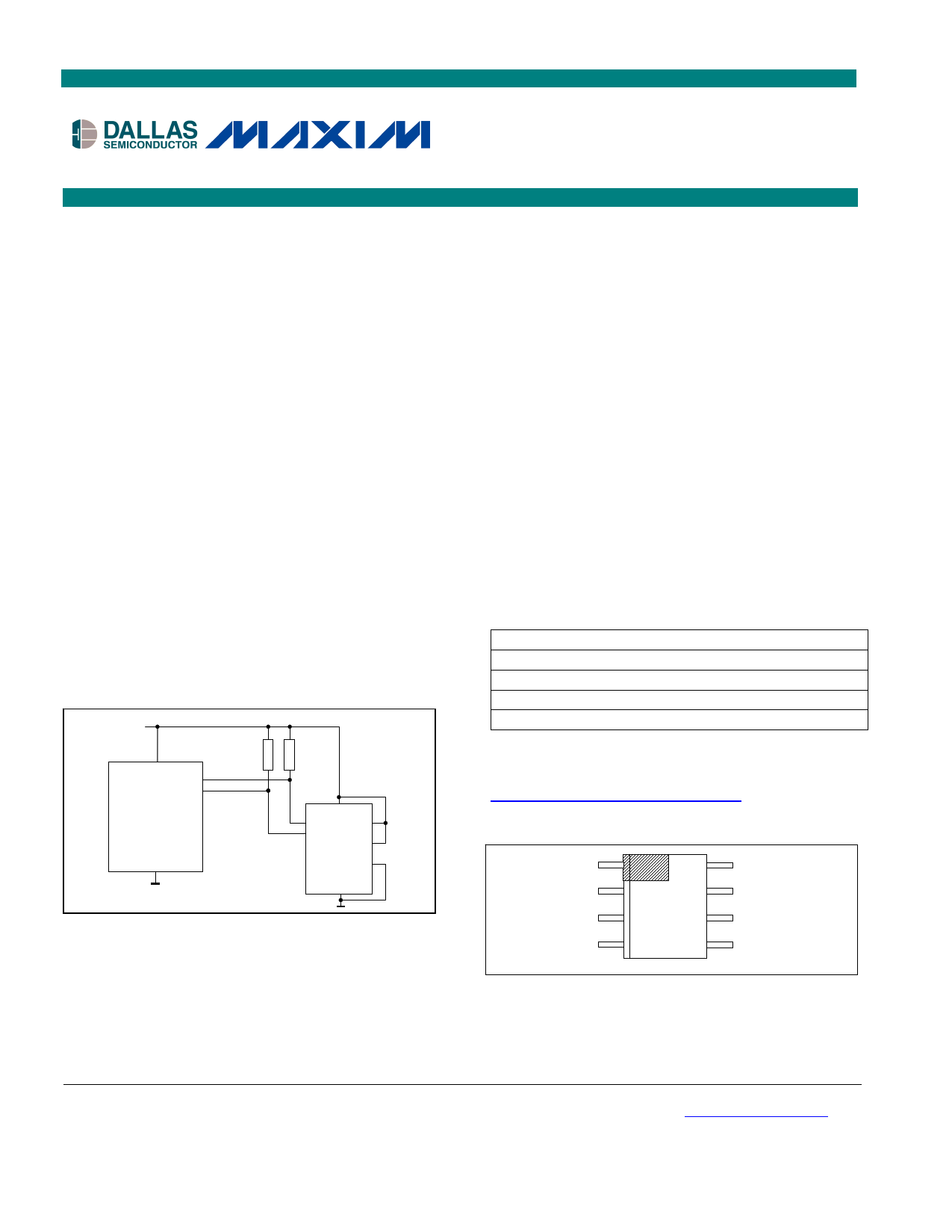

TYPICAL OPERATING CIRCUIT

VCC

RP RP

VCC

µC

SDA

SCL

GND

VCC

SDA AD0

SCL

AD1

AD2

GND

FEATURES

Dedicated Hardware-Accelerated SHA Engine

for Generating SHA-1 MACs

112 Bytes User EEPROM for Storing End

Equipment Property Data

I²C Host Interface, Supports 100kHz and 400kHz

Communication Speeds

Three Address Inputs for I²C Address

Assignment

Single-Byte to 8-Byte EEPROM Write

Sequences

64-Bit Unique Registration Number

EEPROM Endurance: 200k Cycles per 8-Byte

Block at 25°C

10ms max EEPROM Write Cycle

Wide Operating Range: 2.7V to 5.5V,

-40°C to +85°C

±4kV IEC 1000-4-2 ESD Protection Level on All

Pins

8-Pin SO (150 mils) Package

ORDERING INFORMATION

PART

TEMP RANGE PIN-PACKAGE

DS2460S

-40°C to +85°C 8 SO (150 mils)

DS2460S/T&R

-40°C to +85°C 8 SO (150 mils)

DS2460S+

-40°C to +85°C 8 SO (150 mils)

DS2460S+T&R -40°C to +85°C 8 SO (150 mils)

+Denotes a lead(Pb)-free/RoHS-compliant package.

Request full data sheet at:

www.maxim-ic.com/fullds/DS2460

PIN CONFIGURATION

AD0

AD1

AD2

GND

1

2

3

4

8 VCC

7 SCL

6 SDA

5 N.C.

Note: Some revisions of this device may incorporate deviations from published specifications known as errata. Multiple revisions of any device

may be simultaneously available through various sales channels. For information about device errata, click here: www.maxim-ic.com/errata.

1 of 9

1 page

Abridged Data Sheet

DS2460

Slave Address

The slave address to which the DS2460 responds is shown in Figure 5. The logic states at the address pins AD0,

AD1 and AD2 determine the value of the address bits A0, A2, and A4. The address pins allow the device to

respond to one of eight possible slave addresses. The slave address is part of the slave-address/control byte. The

last bit of the slave-address/control byte (R/W) defines the data direction. When set to a 0, subsequent data will

flow from master to slave (write access mode); when set to a 1, data will flow from slave to master (read access

mode).

Figure 4. I²C Protocol Overview

MS-bit

SDA

Slave Address

R/W ACK

bit

ACK

bit

Acknowledgment

from Receiver

Repeated if more bytes

are transferred

SCL

Idle START

Condition

12

6 78

9

ACK

12

Figure 5. DS2460 Slave Address

7-Bit Slave Address

89

ACK

A6 A5 A4 A3 A2 A1 A0

1 0 AD2 0 AD1 0 AD0 R/W

STOP Condition

Repeated START

Condition

Most Signi-

ficant Bit

AD2, AD1, AD0

Pin States

Determines

Read or Write

I²C Definitions

The following terminology is commonly used to describe I²C data transfers. The timing references are defined in

Figure 6.

Bus Idle or Not Busy

Both, SDA and SCL, are inactive and in their logic HIGH states.

START Condition

To initiate communication with a slave, the master has to generate a START condition. A START condition is

defined as a change in state of SDA from HIGH to LOW while SCL remains HIGH. A valid slave address must be

sent by the master and acknowledged by the slave before subsequent START conditions are recognized.

STOP Condition

To end communication with a slave, the master has to generate a STOP condition. A STOP condition is defined as

a change in state of SDA from LOW to HIGH while SCL remains HIGH. A valid slave address must be sent by the

master and acknowledged by the slave before subsequent STOP conditions are recognized.

5 of 9

5 Page | ||

| Páginas | Total 9 Páginas | |

| PDF Descargar | [ Datasheet DS2460.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| DS2460 | SHA-1 Coprocessor | Dallas Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |