|

|

PDF DP83820 Data sheet ( Hoja de datos )

| Número de pieza | DP83820 | |

| Descripción | 10/100/1000 Mb/s PCI Ethernet Network Interface Controller | |

| Fabricantes | National Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de DP83820 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

PRELIMINARY

February 2001

DP83820 10/100/1000 Mb/s PCI Ethernet Network Interface

Controller

www.DataSheet4U.com

General Description

DP83820 is a single-chip 10/100/1000 Mb/s Ethernet

Controller for the PCI bus. It is targeted at high-

performance adapter cards and mother boards. The

DP83820 fully implements the V2.2 66 MHz, 64-bit PCI bus

interface for host communications with power management

support. Packet descriptors and data are transferred via

bus-mastering, reducing the burden on the host CPU. The

DP83820 can support full duplex 10/100/1000 Mb/s

transmission and reception.

Features

— IEEE 802.3 Compliant, 66/33 Mhz, 64/32-bit PCI V2.2

MAC/BIU supports data rates from 1 Mb/s to 1000 Mb/s.

This allows support for traditional 10 Mb/s Ethernet, 100

Mb/s Fast Ethernet, as well as 1000 Mb/s Gigabit

Ethernet.

— Flexible, programmable Bus master - burst sizes of up to

256 dwords (1024 bytes)

— BIU compliant with PC 97 and PC 98 Hardware Design

Guides, PC 99 Hardware Design Guide draft, ACPI v1.0,

PCI Power Management Specification v1, OnNow

Device Class Power Management Reference

Specification - Network Device Class v1.0a

— Wake on LAN (WOL) support compliant with PC98,

PC99, and OnNow, including directed packets, Magic

Packet with SecureOn, ARP packets, pattern match

packets, and Phy status change

— GMII/MII provides IEEE 802.3 standard interface to

support 10/100/1000 Mb/s physical layer devices

— Ten-Bit Interface (TBI) for support of 1000BASE-X

— Virtual LAN (VLAN) and long frame support. VLAN tag

insertion support for transmit packets. VLAN tag

detection and removal for receive packets

— 802.3x Full duplex flow control, including automatic

transmission of Pause frames based on Rx FIFO

thresholds

— IPv.4 checksum task off-loading. Supports checksum

generation and verification of IP, TCP, and UDP headers

— 802.1D and 802.1Q priority queueing support. Supports

multiple priority queues in both transmit and receive

directions.

— Extremely flexible Rx packet filtration including: single

address perfect filter with MSb masking, broadcast,

2,048 entry multicast/unicast hash table, deep packet

pattern matching for up to 4 unique patterns.

— Statistics gathered for support of RFC 1213 (MIB II),

RFC 1398 (Ether-like MIB), IEEE 802.3 LME, reducing

CPU overhead for management.

— Internal 8 KB Transmit and 32 KB Receive data FIFOs

— Supports Jumbo packets

— Serial EEPROM port with auto-load of configuration data

from EEPROM at power-on

— Flash/PROM interface for remote boot support

— Full Duplex support for 10/100/1000 Mb/s data rates

— 208-pin PQFP package

— Low power CMOS design

— 3.3V powered I/Os with 5V tolerant inputs

— JTAG Boundary Scan supported

System Diagram

PCI Bus

DP83820

MII

GMII

10/100/1000 Mb/s

PHY

EEPROM (optional)

Boot ROM (optional)

© 2001 National Semiconductor Corporation

www.national.com

1 page

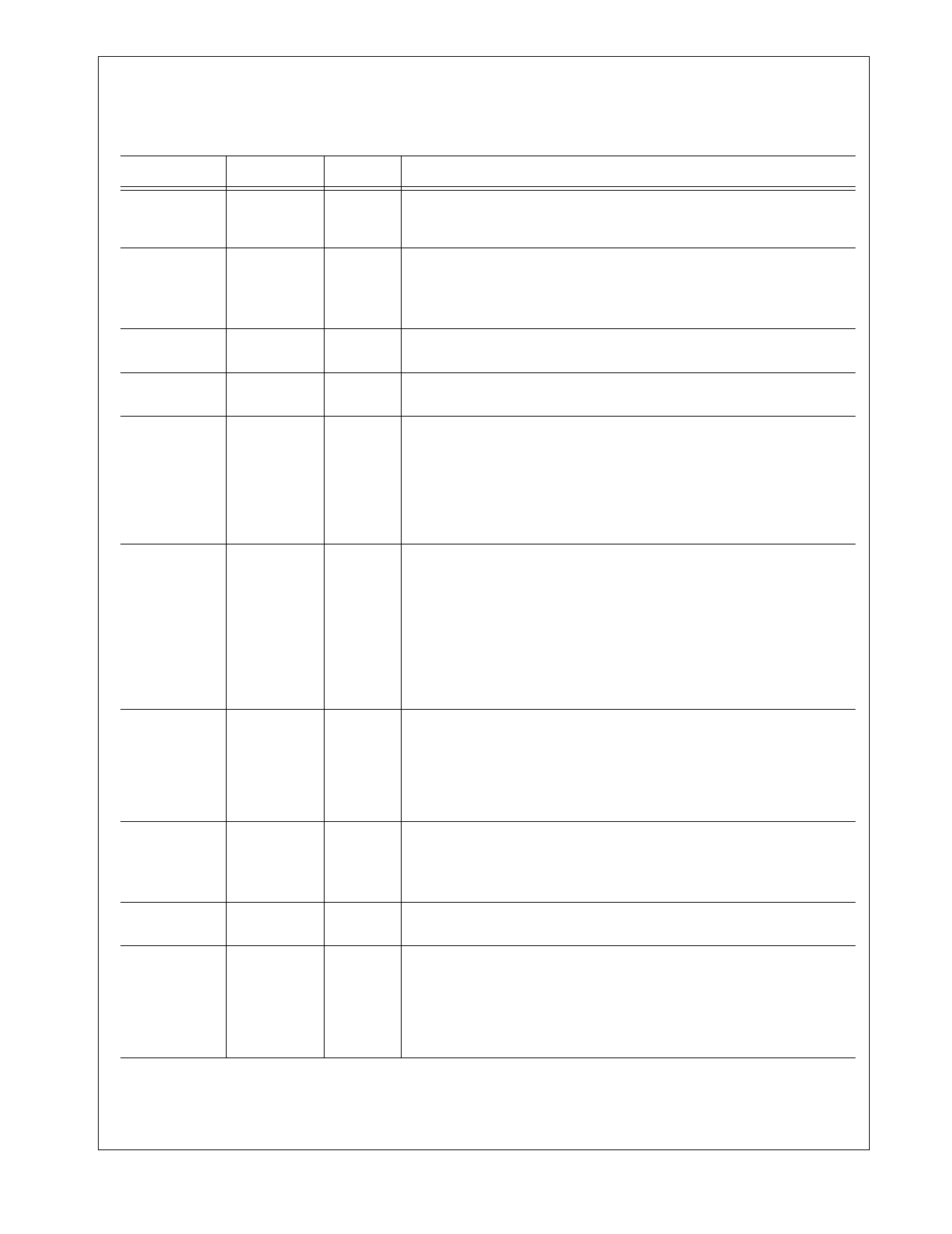

2.0 Pin Descriptions (Continued)

Media Independent Interface (MII) - and Gigabit Media Independent Interface (GMII).

Symbol

COL

CRS/SIGDET

MDC

MDIO

RXCLK/

RXPMACLK1

RXD7,

RXD6,

RXD5,

RXD4,

RXD3,

RXD2,

RXD1,

RXD0

RXDV/RXD8

RXER/RXD9

RXEN

TXCLK/

RXPMACLK0

Pin No(s)

170

169

138

139

156

166,

165,

164,

163,

160,

159,

158,

157

167

168

171

155

Direction

Description

I Collision Detect: The COL signal is asserted high asynchronously by the

external PMD upon detection of a collision on the medium. It will remain

asserted as long as the collision condition persists.

I Carrier Sense: This signal is asserted high asynchronously by the external

physical unit upon detection of a non-idle medium.

Signal Detect: In TBI mode, this signal is used to bring in the Signal Detect

indication from the Phy.

O Management Data Clock: Clock signal with a maximum rate of 2.5 MHz used

to transfer management data for the external PMD on the MDIO pin.

I/O Management Data I/O: Bidirectional signal used to transfer management

information for the external PMD. Requires an external 4.7 KΩ pullup resistor.

I Receive Clock: A continuous clock, sourced by an external PMD device, that is

recovered from the incoming data. During 1000 Mb/s mode RX_CLK is 125

MHz, during 100 Mb/s operation RX_CLK is 25 MHz and during 10 Mb/s this is

2.5 MHz.

Receive PMA Clock 1: In TBI mode, this 62.5Mhz clock is used in conjunction

with RXPMACLK0 to clock 10-bit TBI data into the DP83820. The rising edge of

RXPMACLK1 clocks the even-numbered bytes.

I Gigabit Receive Data: This is a group of 8 signals, sourced from an external

PMD, that contains data aligned on byte boundaries and are driven

synchronous to the RX_CLK. RXD7 is most significant bit.

Receive Data: This is a group of 4 signals, sourced from an external PMD, that

contains data aligned on nibble boundaries and are driven synchronous to the

RX_CLK. RXD3 is the most significant bit and RXD0 is the least significant bit.

RXD7 through RXD4 are not used in this mode.

TBI Receive Data: In TBI mode, these bits are the lower 8 bits of the 10-bit TBI

Receive data.

I Receive Data Valid: This indicates that the external PMD is presenting

recovered and decoded nibbles on the RXD signals, and that RX_CLK is

synchronous to the recovered data in 100 Mb/s operation. This signal will

encompass the frame, starting with the Start-of-Frame delimiter (JK) and

excluding any End-of-Frame delimiter (TR).

TBI Receive Data: In TBI mode, this is RXD8 of the 10-bit TBI Receive data.

I Receive Error: This signal is asserted high synchronously by the external PMD

whenever it detects a media error and RXDV is asserted in 100 Mb/s or 1000

Mb/s operation.

TBI Receive Data: In TBI mode, this is RXD9 of the 10-bit TBI Receive data.

O Receive Output Enable: This pin is used to disable an external PMD while the

BIOS ROM is being accessed.

I MII Transmit Clock: A continuous clock that is sourced by the external PMD.

During 100 Mb/s operation this is 25 MHz +/- 100 ppm. During 10 Mb/s

operation this clock is 2.5 MHz +/- 100 ppm.

Receive PMA Clock 0: In TBI mode, this 62.5Mhz clock is used in conjunction

with RXPMACLK1 to clock 10-bit TBI data into the DP83820. The rising edge of

RXPMACLK0 clocks the odd-numbered bytes.

5 www.national.com

5 Page

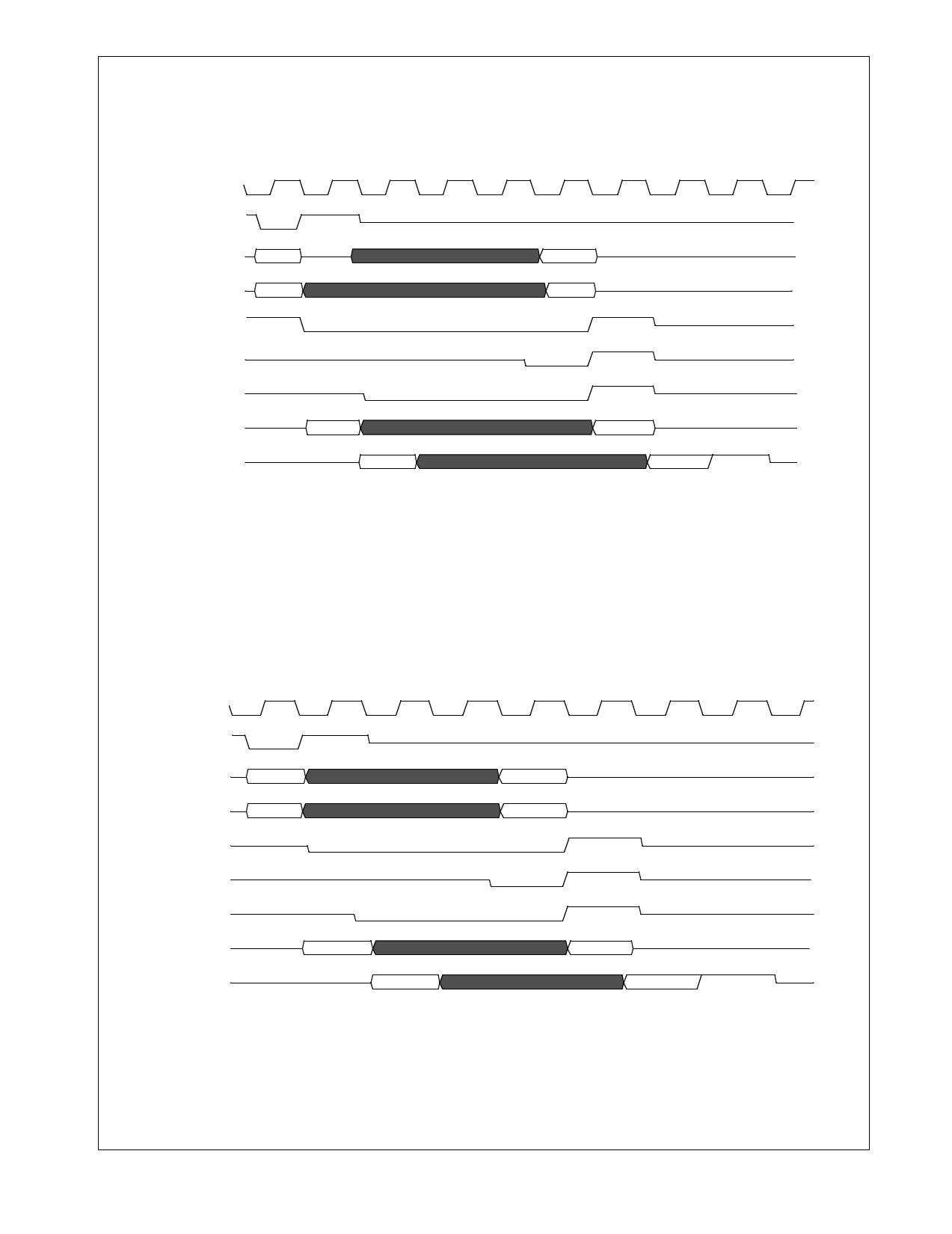

3.0 Functional Description (Continued)

If FRAMEN is asserted beyond the assertion of IRDYN, the STOPN signal with TRDYN. STOPN will remain asserted

DP83820 will still make data available as described above, until FRAMEN is detected as deasserted.

but will also issue a Disconnect. That is, it will assert the

CLK

Figure 3-4 Target Read Operation

FRAMEN

AD[31:0]

C/BEN[3:0]

Addr

Data

IRDYN

TRDYN

DEVSELN

PAR

PERRN

3.3.2 Target Write

A Target Write operation starts with the system generating

FRAMEN, Address, and Command (0011b or 0111b). See

Figure 3-5. If the upper 24 bits on the address bus match

CFGIOA:IOBASE (for I/O reads) or CFGMA:MEMBASE

(for memory reads), the DP83820 will generate DEVSELN

2 clock cycles later.

On the 2nd cycle after the assertion of DEVSELN, the

device will monitor the IRDYN signal. If IRDYN is asserted

at that time, the DP83810 will assert TRDYN. On the next

clock the 32-bit double word will be latched in, and TRDYN

will be forced HIGH for 1 cycle and then tri-stated.

Note: Target write operations must be 32-bits wide.

If FRAMEN is asserted beyond the assertion of IRDYN, the

DP83820 will still latch the first double word as described

above, but will also issue a Disconnect. That is, it will assert

the STOPN signal with TRDYN. STOPN will remain

asserted until FRAMEN is detected as deasserted.

CLK

Figure 3-5 Target Write Operation

FRAMEN

AD[31:0]

C/BEN[3:0]

Addr

Data

IRDYN

TRDYN

DEVSELN

PAR

PERRN

11 www.national.com

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet DP83820.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| DP83820 | DP83820 10/100/1000 Mb/s PCI Ethernet Network Interface Controller (Rev. B) | Texas Instruments |

| DP83820 | 10/100/1000 Mb/s PCI Ethernet Network Interface Controller | National Semiconductor |

| DP83821 | DP83821 10/100/1000 Mb/s PCI Ethernet Network Interface Controller (Rev. A) | Texas Instruments |

| DP83821 | 10/100/1000 Mb/s PCI Ethernet Network Interface Controller | National Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |