|

|

PDF ATTINY24 Data sheet ( Hoja de datos )

| Número de pieza | ATTINY24 | |

| Descripción | (ATTINYx4) 8-bit Microcontroller | |

| Fabricantes | ATMEL Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ATTINY24 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

ATtiny24/44/84

8-bit AVR Microcontroller with 2/4/8K Bytes In-System

Programmable Flash

DATASHEET

Features

● High performance, low power AVR® 8-bit microcontroller

● Advanced RISC architecture

● 120 powerful instructions – most single clock cycle execution

● 32 x 8 general purpose working registers

● Fully static operation

● Non-volatile program and data memories

● 2/4/8K byte of in-system programmable program memory flash (Atmel®

ATtiny24/44/84)

● Endurance: 10,000 write/erase cycles

● 128/256/512 bytes in-system programmable EEPROM (Atmel ATtiny24/44/84)

● Endurance: 100,000 write/erase cycles

● 128/256/512 bytes internal SRAM (Atmel ATtiny24/44/84)

● Programming lock for self-programming flash program and EEPROM data

security

● Peripheral features

● Two Timer/Counters, 8- and 16-bit counters with two PWM channels on both

● 10-bit ADC

● Eight single-ended channels

● 12 differential ADC channel pairs with programmable gain (1x, 20x)

● Temperature measurement

● Programmable watchdog timer with separate on-chip oscillator

● On-chip analog comparator

● Universal serial interface

● Special microcontroller features

● debugWIRE on-chip debug system

● In-system programmable via SPI port

● External and internal interrupt sources

● Pin change interrupt on 12 pins

● Low power idle, ADC noise reduction, standby and power-down modes

● Enhanced power-on reset circuit

● Programmable brown-out detection circuit

● Internal calibrated oscillator

● On-chip temperature sensor

● I/O and packages

● 14-pin SOIC, 20-pin QFN/MLF: Twelve programmable I/O lines

7701G-AVR-02/15

1 page

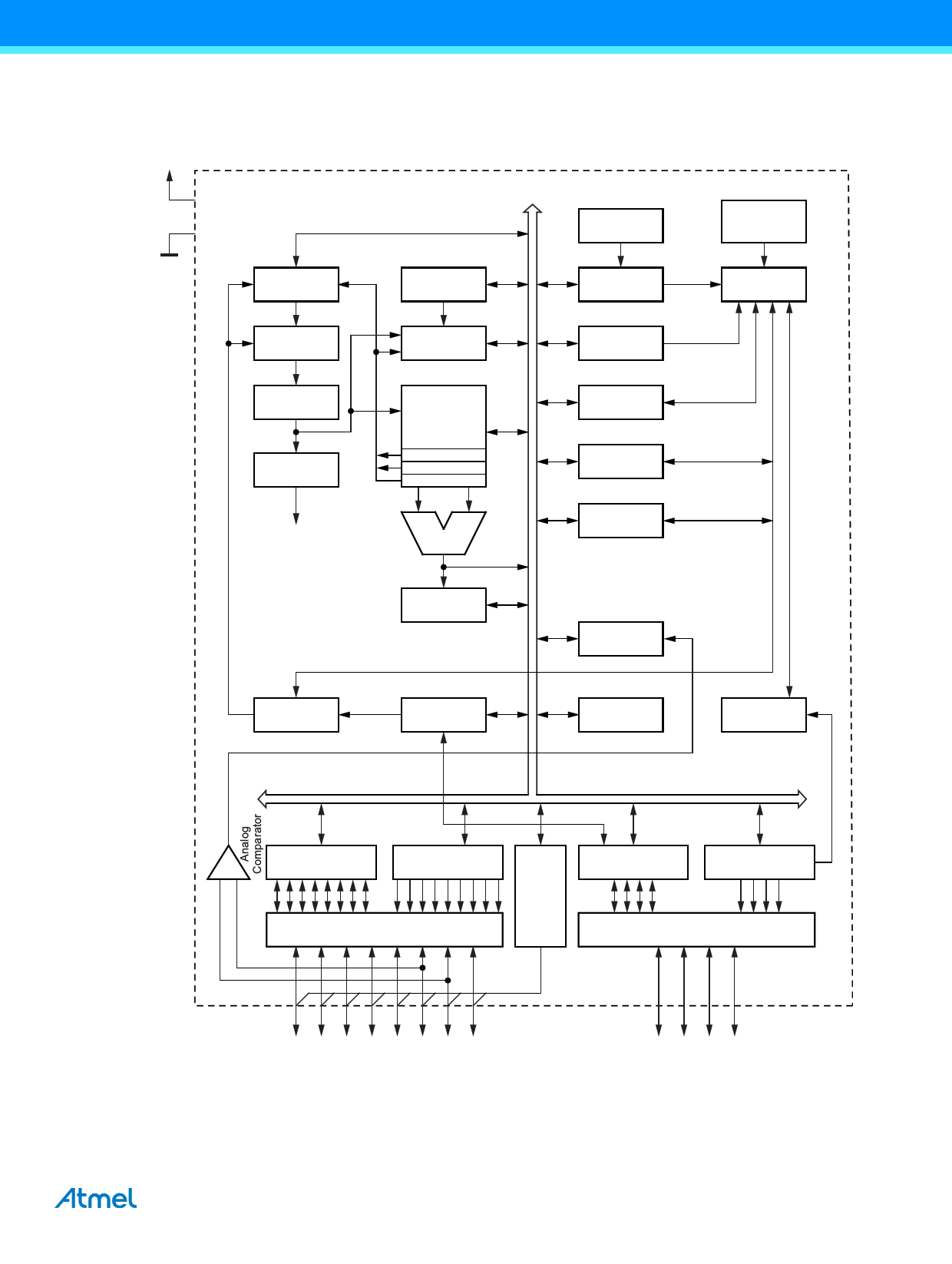

2.1 Block Diagram

Figure 2-1. Block Diagram

VCC

GND

Program

Counter

Program

Flash

Instruction

Register

Instruction

Decoder

Control

Lines

Programming

Logic

8-bit Databus

Internal

Oscillator

Stack

Pointer

Watchdog

Timer

SRAM

MCU Control

Register

General

Purpose

Registers

X

Y

Z

ALU

MCU Status

Register

Timer/

Counter 0

Timer/

Counter 1

Status

Register

Interrupt

Unit

ISP

Interface

EEPROM

Internal

Calibrated

Oscillator

Timing and

Control

Oscillators

+-

Data Register

Port A

Data Dir. Register

Port A

ADC

Data Register

Port B

Data Dir. Register

Port B

Port A Drivers

Port B Drivers

PA7-PA0

PB3-PB0

ATtiny24/44/84 [DATASHEET]

7701G–AVR–02/15

5

5 Page

5.4.1 SREG – AVR Status Register

Bit 7 6 5 4 3 2 1 0

0x3F (0x5F)

I

T

HSVNZ

C SREG

Read/Write

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Initial Value

0

0

0

0

0

0

0

0

• Bit 7 – I: Global Interrupt Enable

The global interrupt enable bit must be set for the interrupts to be enabled. The individual interrupt enable control is then

performed in separate control registers. If the global interrupt enable register is cleared, none of the interrupts are enabled

independently of the individual interrupt enable settings. The I-bit is cleared by hardware after an interrupt has occurred, and

is set by the RETI instruction to enable subsequent interrupts. The I-bit can also be set and cleared by the application with

the SEI and CLI instructions, as described in the instruction set summary.

• Bit 6 – T: Bit Copy Storage

The bit copy instructions BLD (Bit LoaD) and BST (Bit STore) use the T-bit as source or destination for the operated bit. A bit

from a register in the register file can be copied into T by the BST instruction, and a bit in T can be copied into a bit in a

register in the register file by the BLD instruction.

• Bit 5 – H: Half Carry Flag

The half carry flag H indicates a half carry in some arithmetic operations. Half carry is useful in BCD arithmetic. See the

instruction set reference for detailed information.

• Bit 4 – S: Sign Bit, S = N V

The S-bit is always an exclusive OR between the negative flag N and the two's complement overflow flag V. See the

“Instruction Set Description” for detailed information.

• Bit 3 – V: Two’s Complement Overflow Flag

The two's complement overflow flag V supports two's complement arithmetic. See the instruction set summary for detailed

information.

• Bit 2 – N: Negative Flag

The negative flag N indicates a negative result in an arithmetic or logic operation. See the instruction set summary for

detailed information.

• Bit 1 – Z: Zero Flag

The zero flag Z indicates a zero result in an arithmetic or logic operation. See the instruction set summary for detailed

information.

• Bit 0 – C: Carry Flag

The carry flag C indicates a carry in an arithmetic or logic operation. See the instruction set summary for detailed

information.

ATtiny24/44/84 [DATASHEET]

7701G–AVR–02/15

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet ATTINY24.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ATTINY20 | 8-bit AVR Microcontroller | ATMEL Corporation |

| ATTINY22L | 8-bit Microcontroller with 2K Bytes of In-System Programmable Flash | ATMEL Corporation |

| ATTINY2313 | 8-bit AVR Microcontroller with 2K Bytes In-System Programmable Flash | ATMEL Corporation |

| ATTINY2313 | 8-bit AVR Microcontroller with 2K Bytes In-System Programmable Flash | ATMEL Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |