|

|

PDF A49LF004 Data sheet ( Hoja de datos )

| Número de pieza | A49LF004 | |

| Descripción | 4 Mbit CMOS 3.3Volt-only Firmware Hub Flash Memory | |

| Fabricantes | AMIC Technology | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de A49LF004 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

Preliminary

A49LF004

4 Mbit CMOS 3.3Volt-only Firmware Hub Flash Memory

Document Title

4 Mbit CMOS 3.3 Volt-only Firmware Hub Flash Memory

Revision History

Rev. No. History

0.0 Initial issue

Issue Date

November 21, 2003

Remark

Preliminary

PRELIMINARY (November, 2003, Version 0.0)

AMIC Technology, Corp.

1 page

A49LF004

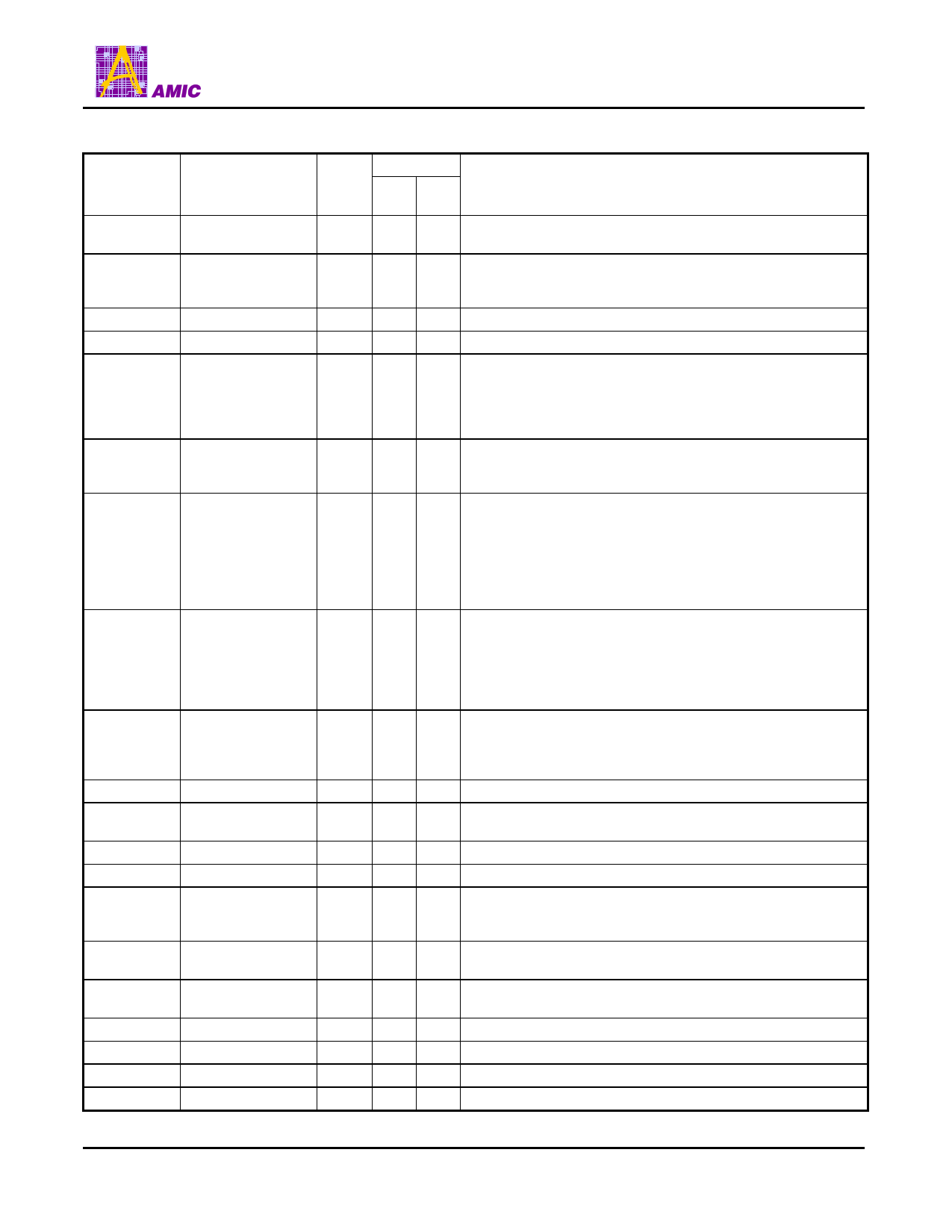

Table 1: Pin Description

Symbol

Pin Name

Type

Interface

A/A

Mux

FWH

Descriptions

A10-A0

Address

IN X

Inputs for addresses during Read and Write operations in A/A

Mux mode. Row and column addresses are latched by R/C# pin.

I/O7-I/O0

Data

I/O X

To output data during Read cycle and receive input data during

Write cycle in A/A Mux mode. The outputs are in tri-state when

OE# is high.

OE#

Output Enable

IN X

To control the data output buffers.

WE#

Write Enable

IN X

To control the Write operations.

To determine which interface is operational. When held high, A/A

IC

Interface

Configuration Pin

IN

Mux mode is enabled and when held low, FWH mode is enabled.

X X This pin must be setup at power-up or before return from reset

and not change during device operation. This pin is internally

pulled down with a resistor between 20-100 KΩ.

INIT#

Initialize

IN

This is the second reset pin for in-system use. INIT# and RST#

X pins are internally combined and initialize a device reset when

driven low.

ID[3:0]

Identification Inputs IN

These four pins are part of the mechanism that allows multiple

FWH devices to be attached to the same bus. To identify the

component, the correct strapping of these pins must be set. The

X boot device must have ID[3:0]=0000 and it is recommended that

all subsequent devices should use sequential up-count

strapping. These pins are internally pulled down with a resistor

between 20-100 KΩ.

FGPI[4:0]

General Purpose

Inputs

IN

These individual inputs can be used for additional board

flexibility. The state of these pins can be read immediately at

X

boot, through FWH internal registers. These inputs should be at

their desired state before the start of the PCI clock cycle during

which the read is attempted, and should remain in place until the

end of the Read cycle. Unused FGPI pins must not be floated.

TBL#

Top Block Lock

IN

To prevent any write operations to the Boot Block when driven

X

low, regardless of the state of the block lock registers. When

TBL# is high it disables hardware write protection for the top

Boot Block. This pin cannot be left unconnected.

FWH[3:0]

FWH I/Os

I/O

X I/O Communications in FWH mode.

CLK

Clock

IN

X

To provide a clock input to the device. This pin is the same as

that for the PCI clock and adheres to the PCI specifications.

FWH4

FWH Input

IN

X Input communication in FWH mode.

RST#

Reset

IN X X To reset the operation of the device

WP#

Write Protect

IN

When low, prevents any write operations to all but the highest

X addressable block. When WP# is high it disables hardware write

protection for these blocks. This pin cannot be left unconnected.

R/C#

Row/Column Select IN

X

This pin determines whether the address pins are pointing to the

row addresses or the column addresses in A/A Mux mode.

RB#

Ready/Busy#

OUT X

To determine if the device is busy in write operations. Valid only

in A/A Mux mode.

RES

Reserved

X Reserved. These pins must be left unconnected.

VDD

Power Supply

PWR X

X To provide power supply (3.0-3.6Volt).

VSS

Ground

PWR X

X Circuit ground. All VSS pins must be grounded.

NC No Connection

X X Unconnected pins.

1. IN=Input, OUT=output, I/O=Input/Output, PWR=Power

PRELIMINARY (November, 2003, Version 0.0)

4

AMIC Technology, Corp.

5 Page

A49LF004

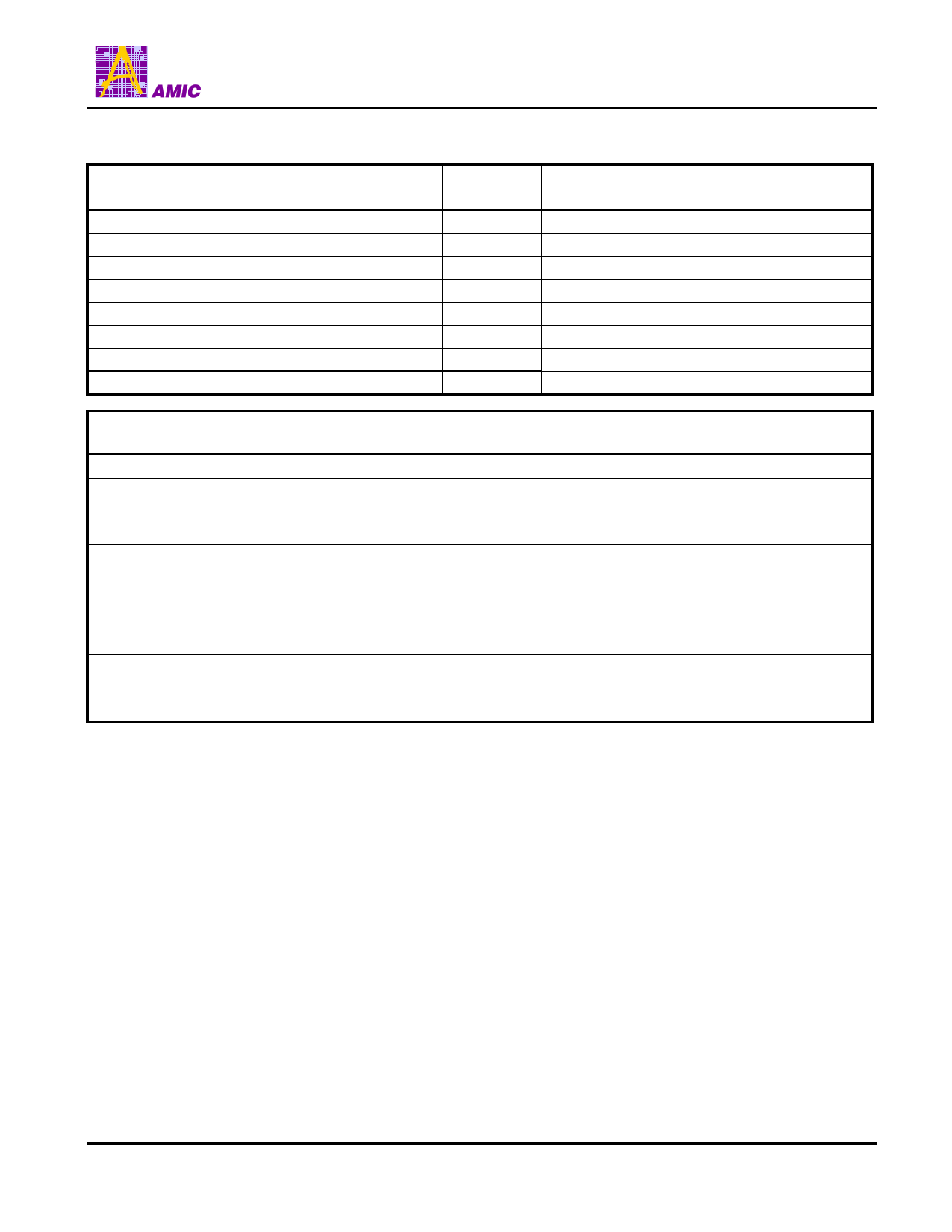

Table 6: Lock Register Bit Definition

Data

00h

01h

02h

03h

04h

05h

06h

07h

Reserved

Bit 7:3

00000

00000

00000

00000

00000

00000

00000

00000

Read-Lock

Bit 2

0

0

0

0

1

1

1

1

Lock-Down

Bit 1

0

0

1

1

0

0

1

1

Write-Lock

Bit 0

0

1

0

1

0

1

0

1

Function

Full Access.

Write locked. Default state at power-up.

Locked open (full access locked down).

Write-locked down.

Read locked.

Read and Write locked.

Read-locked down

Read- and Write-locked down

Data

7:3

2

1

0

Function

Reserved

Read-Lock

1 = Prevents read operations in the block where set

0 = Normal operation for reads in the block where clear. This is the default state.

Lock-Down

1 = Prevents further set or clear operations to the Write-Lock and Read-Lock bits. Lock-Down only can be set

but not clear. The block will remain lock-down until reset (with RST# or INIT# being Low), or until the device

is power-on reset.

0 = Normal operation for Write-Lock and Read-Lock bit altering in the block where clear. This is the default state.

Write-Lock

1 = Prevents program or erase operations in the block where set. This is the default state.

0 = Normal operation for programming and erase in the block where clear.

ADDRESS/ADDRESS MULTIPLEXED (A/A

MUX) MODE

Device Operation

Commands are used to initiate the memory operation

functions of the device. The data portion of the software

command sequence is latched on the rising edge of WE#.

During the software command sequence the row address is

latched on the falling edge of R/C# and the column address

is latched on the rising edge of R/C#. Refer to Table 7 and

Table 8 for operation modes and the command sequence.

Read

The Read operation of the A49LF004 device is controlled by

OE#. OE# is the output control and is used to gate data from

the output pins. Refer to the Read cycle timing diagram,

Figure 10 for further details.

Reset

A VIL on RST# pin initiates a device reset.

Byte-Program Operation

The A49LF004 device is programmed on a byte-by-byte

basis. Before programming, one must ensure that the block,

in which the byte which is being programmed exists, is fully

erased. The Byte-Program operation is initiated by executing

a four-byte command load sequence for Software Data

Protection with address and data in the last byte sequence.

During the Byte-Program operation, the row address (A10-

A0) is latched on the falling edge of R/C# and the column

Address (A21-A11) is latched on the rising edge of R/C#.

The data bus is latched in the rising edge of WE#. See

Figure 11 for Program operation timing diagram, Figure 14

for timing waveforms, and Figure 19 for its flowchart. During

the Program operation, the only valid reads are Data#

Polling and Toggle Bit. During the internal Program

operation, the host is free to perform additional tasks. Any

commands written during the internal Program operation will

be ignored.

PRELIMINARY (November, 2003, Version 0.0)

10

AMIC Technology, Corp.

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet A49LF004.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| A49LF004 | 4 Mbit CMOS 3.3Volt-only Firmware Hub Flash Memory | AMIC Technology |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |