|

|

PDF DP83840A Data sheet ( Hoja de datos )

| Número de pieza | DP83840A | |

| Descripción | 10/100 Mb/s Ethernet Physical Layer | |

| Fabricantes | National Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de DP83840A (archivo pdf) en la parte inferior de esta página. Total 70 Páginas | ||

|

No Preview Available !

March 1997

DP83840A

10/100 Mb/s Ethernet Physical Layer

General Description

The DP83840A is a Physical Layer device for Ethernet

10BASE-T and 100BASE-X using category 5 Unshielded,

Type 1 Shielded and Fiber Optic cables.

This VLSI device is designed for easy implementation of

10/100 Mb/s Ethernet LANs. It interfaces to the PMD sub-

layer through National Semiconductor's DP83223 Twisted

Pair Transceiver, and to the MAC layer through a Media

Independent Interface (MII), ensuring interoperability

between products from different vendors.

The DP83840A is designed with National Semiconductor's

BiCMOS process. Its system architecture is based on the

integration of several of National Semiconductor's industry

proven core technologies:

10BASE-T ENDEC/Transceiver module to provide the 10

Mb/s IEEE 802.3 functions

Clock Recovery/Generator Modules from National

Semiconductor's leading FDDI product

FDDI Stream Cipher (Cyclone)

100BASE-X physical coding sub-layer (PCS) and control

logic that integrate the core modules into a dual speed

Ethernet physical layer controller

Features

• IEEE 802.3 10BASE-T compatible--ENDEC and UTP/

STP transceivers and filters built-in

• IEEE 802.3u 100BASE-X compatible--support for 2 pair

Category 5 UTP (100m), Type 1 STP and Fiber Optic

Transceivers--Connects directly to the DP83223 Twisted

Pair Transceiver

• ANSI X3T12 TP-PMD compatible

• IEEE 802.3u Auto-Negotiation for automatic speed

selection

• IEEE 802.3u compatible Media Independent Interface

(MII) with Serial Management Interface

• Integrated high performance 100 Mb/s clock recovery

circuitry requiring no external filters

• Full Duplex support for 10 and 100 Mb/s

• MII Serial 10 Mb/s output mode

• Fully configurable node and repeater modes--allows

operation in either application

• Programmable loopback modes for easy system

diagnostics

• Flexible LED support

• IEEE 1149.1 Standard Test Access Port and Boundary-

Scan compatible

• Small footprint 100-pin PQFP package

• Individualized scrambler seed for multi-PHY applications

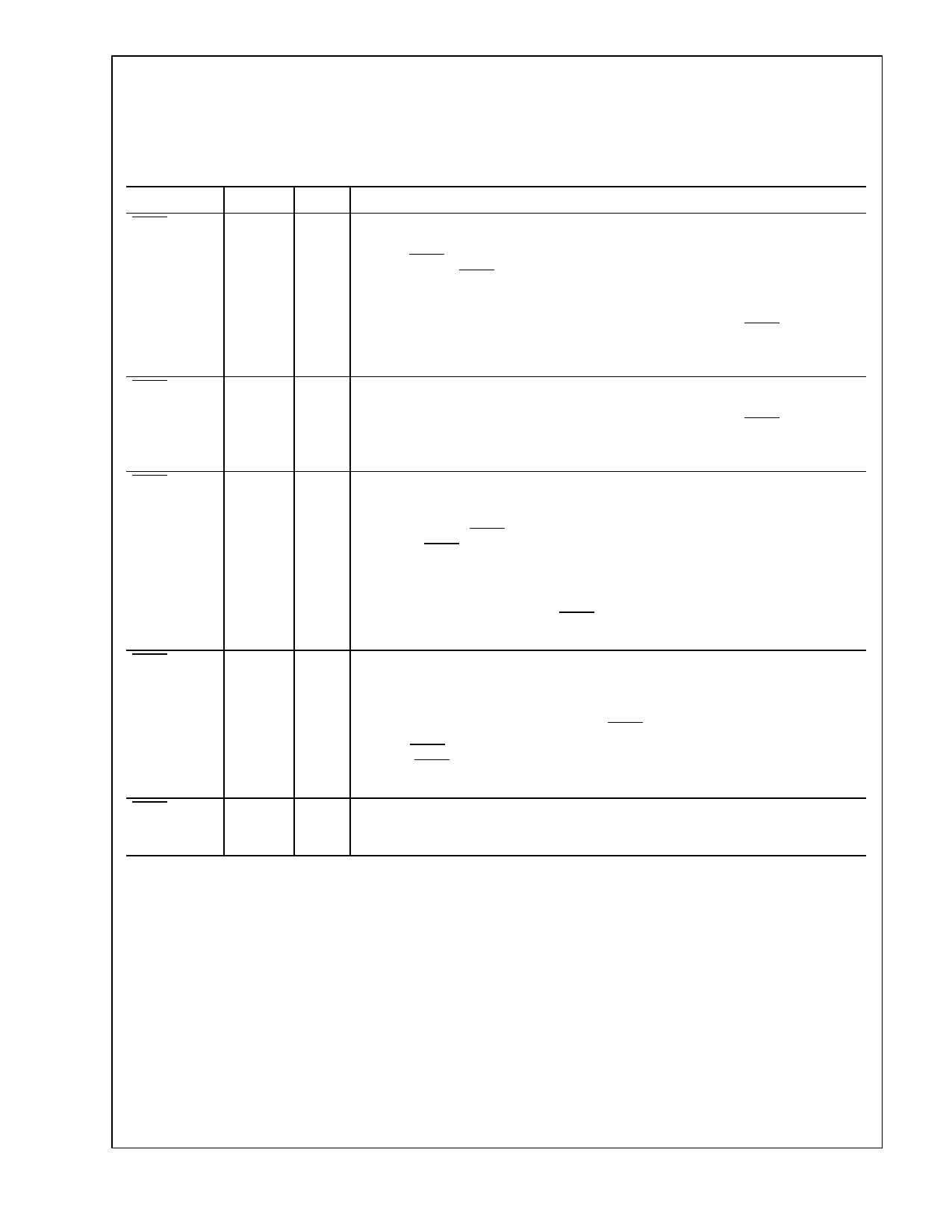

System Diagram

10 AND/OR 100 Mb/s

ETHERNET MAC OR

REPEATER/SWITCH

PORT

MII

DP83840A

10/100 Mb/s

ETHERNET PHYSICAL LAYER

CLOCKS

STATUS

LEDS

10BASE-T

DP83223

100BASE-TX

TRANSCEIVER

100BASE-FX

TRANSCEIVER

RJ-45

10BASE-T

OR

100BASE-TX

Version A

1 National Semiconductor

1 page

2.0 Pin Description

The DP83840A pins are classified into the following interface categories (each interface is described in the sections that

follow):

MII INTERFACE

100 Mb/s SERIAL PMD INTERFACE

10 Mb/s INTERFACE

CLOCK INTERFACE

DEVICE CONFIGURATION INTERFACE

LED INTERFACE

IEEE 1149.1 INTERFACE

PHY ADDRESS INTERFACE

MISCELLANEOUS PINS

POWER AND GROUND PINS

SPECIAL CONNECT PINS

2.1 MII INTERFACE

Signal Name

TX_CLK

Type

O, Z

TXD[3]

TXD[2]

TXD[1]

TXD[0]

TX_EN

I, J

I, J

TX_ER

(TXD[4])

I, J

MDC

I,J

MDIO

I/O, Z, J

Pin #

Description

82 TRANSMIT CLOCK: Transmit clock output from the DP83840A:

25 MHz nibble transmit clock derived from Clock Generator Module's (CGM) PLL

in 100BASE-TX mode

2.5 MHz transmit clock in 10BASE-T nibble mode

10 MHz transmit clock in 10BASE-T serial mode

75 TRANSMIT DATA: Transmit data MII input pins that accept nibble data during

76

normal nibble-wide MII operation at either 2.5 MHz (10BASE-T mode) or 25MHz

(100BASE-X mode)

77

In 10 Mb/s serial mode, the TXD[0] pin is used as the serial data input pin. TXD[3:1]

78 are ignored.

74 TRANSMIT ENABLE: Active high input indicates the presence of valid nibble data

on TXD[3:0] for both 100 Mb/s or 10 Mb/s nibble mode.

In 10 Mb/s serial mode, active high indicates the presence of valid 10 Mb/s data on

TXD[0].

73 TRANSMIT ERROR: In 100 Mb/s mode, when this signal is high and TX_EN is

active the HALT symbol is substituted for the actual data nibble.

In 10 Mb/s mode, this input is ignored.

In encoder bypass mode (BP_4B5B or BP_ALIGN), TX_ER becomes the TXD [4]

pin, the new MSB for the transmit 5-bit data word.

72 MANAGEMENT DATA CLOCK: Synchronous clock to the MDIO management

data input/output serial interface which may be asynchronous to transmit and

receive clocks. The maximum clock rate is 2.5 MHz. There is no minimum clock

rate.

67 MANAGEMENT DATA I/O: Bi-directional management instruction/data signal that

may be sourced by the station management entity or the PHY. This pin requires a

1.5kΩ pullup resistor.

I = TTL/CMOS input

O = TTL/CMOS output

Z = TRI-STATE output

J = IEEE 1149.1 pin

Version A

5 National Semiconductor

Subject to change without notice.

5 Page

2.0 Pin Description (Continued)

2.6 LED INTERFACE

These outputs can be used to drive LEDs directly, or can be used to provide status information to a network

management device. Refer to Figure 12 for the LED connection diagram. Refer to section 2.2 for a description of how to

generate LED indication of 100 Mb/s mode. Note that these outputs are standard CMOS voltage drivers and not

open-drain.

Signal Name Type Pin #

Description

LED1

O, J 42 TRANSMIT LED: Indicates the presence of transmit activity (TXE asserted) for 10

Mb/s and 100 Mb/s operation. Active low.

If bit 2 (LED1_MODE) of the PCS Configuration Register (address 17h) is set

high, then the LED1 pin function is changed to indicate the status of the

Disconnect Function as defined by the state of bit 5 (CON_STATUS) in the PHY

address register (address 19h).

The DP83840A incorporates a “monostable” function on the LED1 output. This

ensures that even minimum size packets generate adequate LED ON time

(approximately 50ms) for visibility.

LED2

O, J 41 RECEIVE LED: Indicates the presence of any receive activity (CRS active) for 10

Mb/s and 100 Mb/s operation. Active low.

The DP83840A incorporates a “monostable” function on the LED2 output. This

ensures that even minimum size packets generate adequate LED ON time

(approximately 50ms) for visibility.

LED3

O, J 38 LINK LED: Indicates Good Link status for 10 Mb/s and 100 Mb/s operation. Active

low.

100 Mb/s Link is established as a result of the assertion of the Signal Detect input

to the DP83840A. LED3 will assert after SD has remained asserted for a minimum

of 500µs. LED3 will deassert immediately following the deassertion of Signal

Detect.

10 Mb/s Link is established as a result of the reception of at least seven

consecutive normal Link Pulses or the reception of a valid 10BASE-T packet

which will cause the assertion of LED3. LED3 will deassert in accordance with the

Link Loss Timer as specified in 802.3.

LED4

O, J 37 POLARITY/FULL DUPLEX LED: Indicates Good Polarity status for 10 Mb/s

operation. Can be configured to Indicate Full Duplex mode status for 10 Mb/s or

100 Mb/s operation. Active low.

The DP83840A automatically compensates for polarity inversion. Polarity

inversion is indicated by the assertion of LED4.

If bit 1 (LED4_MODE) in the PCS Configuration Register (address 17h) is set

high, the LED4 pin function is changed to indicate Full Duplex mode status for 10

Mb/s and 100 Mb/s operation.

LED5

O, J 36 COLLISION LED: Indicates the presence of collision activity for 10 Mb/s and 100

Mb/s Half Duplex operation. This LED has no meaning for 10 Mb/s or 100 Mb/s

Full Duplex operation and will remain deasserted. Active low.

I = TTL/CMOS input

O = TTL/CMOS output

Z = TRI-STATE output

J = IEEE 1149.1 pin

Version A

11 National Semiconductor

11 Page | ||

| Páginas | Total 70 Páginas | |

| PDF Descargar | [ Datasheet DP83840A.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| DP83840A | 10/100 Mb/s Ethernet Physical Layer | National Semiconductor |

| DP83840A | DP83840A 10/100 Mb/s Ethernet Physical Layer (Rev. A) | Texas Instruments |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |