|

|

PDF DP83846A Data sheet ( Hoja de datos )

| Número de pieza | DP83846A | |

| Descripción | DsPHYTER -Single 10/100 Ethernet Transceiver | |

| Fabricantes | National Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de DP83846A (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

May 2002

DP83846A DsPHYTER — Single 10/100 Ethernet Transceiver

General Description

Features

The DP83846A is a full feature single Physical Layer

device with integrated PMD sublayers to support both

10BASE-T and 100BASE-TX Ethernet protocols over Cat-

egory 3 (10 Mb/s) or Category 5 Unsheilded twisted pair

cables.

The DP83846A is designed for easy implementation of

10/100 Mb/s Ethernet home or office solutions. It interfaces

to Twisted Pair media via an external transformer. This

device interfaces directly to MAC devices through the IEEE

802.3u standard Media Independent Interface (MII) ensur-

ing interoperability between products from different ven-

dors.

The DP83846A utilizes on chip Digital Signal Processing

(DSP) technology and digital Phase Lock Loops (PLLs) for

robust performance under all operating conditions,

enhanced noise immunity, and lower external component

count when compared to analog solutions.

■ IEEE 802.3 ENDEC, 10BASE-T transceivers and filters

■ IEEE 802.3u PCS, 100BASE-TX transceivers and filters

■ IEEE 802.3 compliant Auto-Negotiation

■ Output edge rate control eliminates external filtering for

Transmit outputs

■ BaseLine Wander compensation

■ 5V/3.3V MAC interface

■ IEEE 802.3u MII (16 pins/port)

■ LED support (Link, Rx, Tx, Duplex, Speed, Collision)

■ Single register access for complete PHY status

■ 10/100 Mb/s packet loopback BIST (Built in Self Test)

■ Low-power 3.3V, 0.35um CMOS technology

■ Power consumption < 495mW (typical)

■ 5V tolerant I/Os

■ 80-pin LQFP package (12w) x (12l) x (1.4h) mm

Applications

■ Network Interface Cards

■ PCMCIA Cards

System Diagram

Ethernet MAC

MII

DP83846A

10/100 Mb/s

DsPHYTER

25 MHz

Clock

Status

LEDs

RJ-45

10BASE-T

or

100BASE-TX

Typical DsPHYTER application

©2002 National Semiconductor Corporation

www.national.com

1 page

1.0 Pin Descriptions

The DP83846A pins are classified into the following inter-

face categories (each interface is described in the sections

that follow):

— MII Interface

— 10/100 Mb/s PMD Interface

— Clock Interface

— Special Connect Pins

— LED Interface

— Strapping Options/Dual Function pins

— Reset

— Power and Ground pins

Note: Strapping pin option (BOLD) Please see Section 1.6

for strap definitions.

Note: All DP83846A signal pins are I/O cells regardless of

the particular use. Below definitions define the functionality

of the I/O cells for each pin.

Type: I

Inputs

Type: O

Outputs

Type: I/O Input/Output

Type OD Open Drain

Type: PD,PU Internal Pulldown/Pullup

Type: S

Strapping Pin (All strap pins except PHY-

AD[0:4] have internal pull-ups or pull-

downs. If the default strap value is needed

to be changed then an external 5 kΩ resistor

should be used. Please see Table 1.6 on

page 7 for details.)

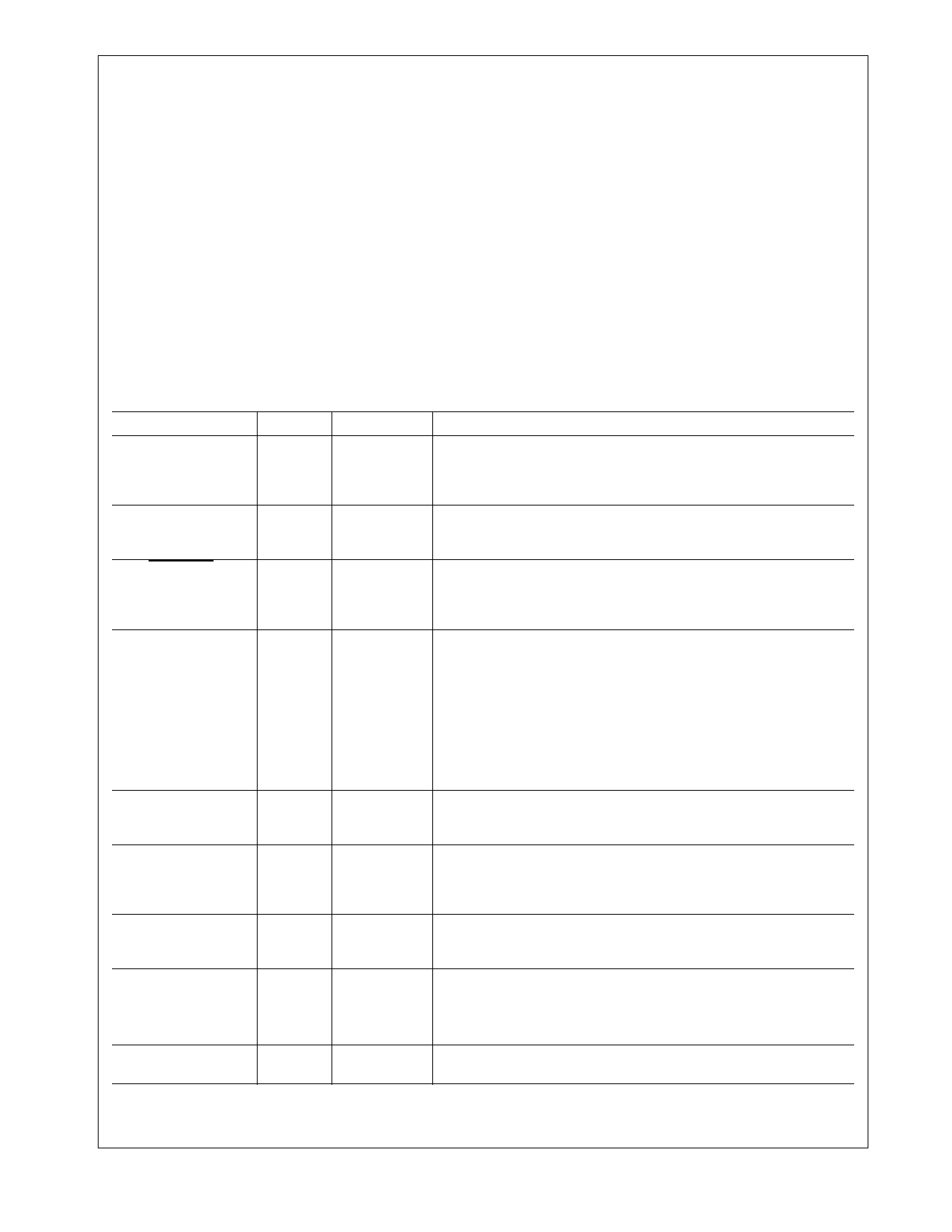

1.1 MII Interface

Signal Name

MDC

MDIO

CRS/LED_CFG

COL

TX_CLK

TXD[3]

TXD[2]

TXD[1]

TXD[0]]

TX_EN

TX_ER

RX_CLK

Type

I

I/O, OD

O, S

O

O

I

LQFP Pin #

Description

37 MANAGEMENT DATA CLOCK: Synchronous clock to the MDIO

management data input/output serial interface which may be asyn-

chronous to transmit and receive clocks. The maximum clock rate is

25 MHz with no minimum clock rate.

36 MANAGEMENT DATA I/O: Bi-directional management instruc-

tion/data signal that may be sourced by the station management en-

tity or the PHY. This pin requires a 1.5 kΩ pullup resistor.

61 CARRIER SENSE: Asserted high to indicate the presence of carrier

due to receive or transmit activity in 10BASE-T or 100BASE-TX Half

Duplex Modes, while in full duplex mode carrier sense is asserted to

indicate the presence of carrier due only to receive activity.

60 COLLISION DETECT: Asserted high to indicate detection of a colli-

sion condition (simultaneous transmit and receive activity) in 10

Mb/s and 100 Mb/s Half Duplex Modes.

While in 10BASE-T Half Duplex mode with Heartbeat enabled this

pin are also asserted for a duration of approximately 1µs at the end

of transmission to indicate heartbeat (SQE test).

In Full Duplex Mode, for 10 Mb/s or 100 Mb/s operation, this signal

is always logic 0. There is no heartbeat function during 10 Mb/s full

duplex operation.

51 TRANSMIT CLOCK: 25 MHz Transmit clock outputs in 100BASE-

TX mode or 2.5 MHz in 10BASE-T mode derived from the 25 MHz

reference clock.

59, 58, 55, 54 TRANSMIT DATA: Transmit data MII input pins that accept nibble

data synchronous to the TX_CLK (2.5 MHz in 10BASE-T Mode or

25 MHz in 100BASE-TX mode.

I

I

O, PU

52 TRANSMIT ENABLE: Active high input indicates the presence of

valid nibble data on data inputs, TXD[3:0] for both 100 Mb/s or 10

Mb/s nibble mode.

50 TRANSMIT ERROR: In 100MB/s mode, when this signal is high and

the corresponding TX_EN is active the HALT symbol is substituted

for data.

In 10 Mb/s this input is ignored.

45 RECEIVE CLOCK: Provides the 25 MHz recovered receive clocks

for 100BASE-TX mode and 2.5 MHz for 10BASE-T nibble mode.

5 www.national.com

5 Page

2.0 Configuration

This section includes information on the various configura-

tion options available with the DP83846A. The configura-

tion options described below include:

— Device Configuration

— Auto-Negotiation

— PHY Address and LEDs

— Half Duplex vs. Full Duplex

— Isolate mode

— Loopback mode

— BIST

2.1 Auto-Negotiation

The Auto-Negotiation function provides a mechanism for

exchanging configuration information between two ends of

a link segment and automatically selecting the highest per-

formance mode of operation supported by both devices.

Fast Link Pulse (FLP) Bursts provide the signalling used to

communicate Auto-Negotiation abilities between two

devices at each end of a link segment. For further detail

regarding Auto-Negotiation, refer to Clause 28 of the IEEE

802.3u specification. The DP83846A supports four differ-

ent Ethernet protocols (10 Mb/s Half Duplex, 10 Mb/s Full

Duplex, 100 Mb/s Half Duplex, and 100 Mb/s Full Duplex),

so the inclusion of Auto-Negotiation ensures that the high-

est performance protocol will be selected based on the

advertised ability of the Link Partner. The Auto-Negotiation

function within the DP83846A can be controlled either by

internal register access or by the use of the AN_EN, AN1

and AN0 pins.

2.1.1 Auto-Negotiation Pin Control

The state of AN_EN, AN0 and AN1 determines whether the

DP83846A is forced into a specific mode or Auto-Negotia-

tion will advertise a specific ability (or set of abilities) as

given in Table 1. These pins allow configuration options to

be selected without requiring internal register access.

The state of AN_EN, AN0 and AN1, upon power-up/reset,

determines the state of bits [8:5] of the ANAR register.

The Auto-Negotiation function selected at power-up or

reset can be changed at any time by writing to the Basic

Mode Control Register (BMCR) at address 00h.

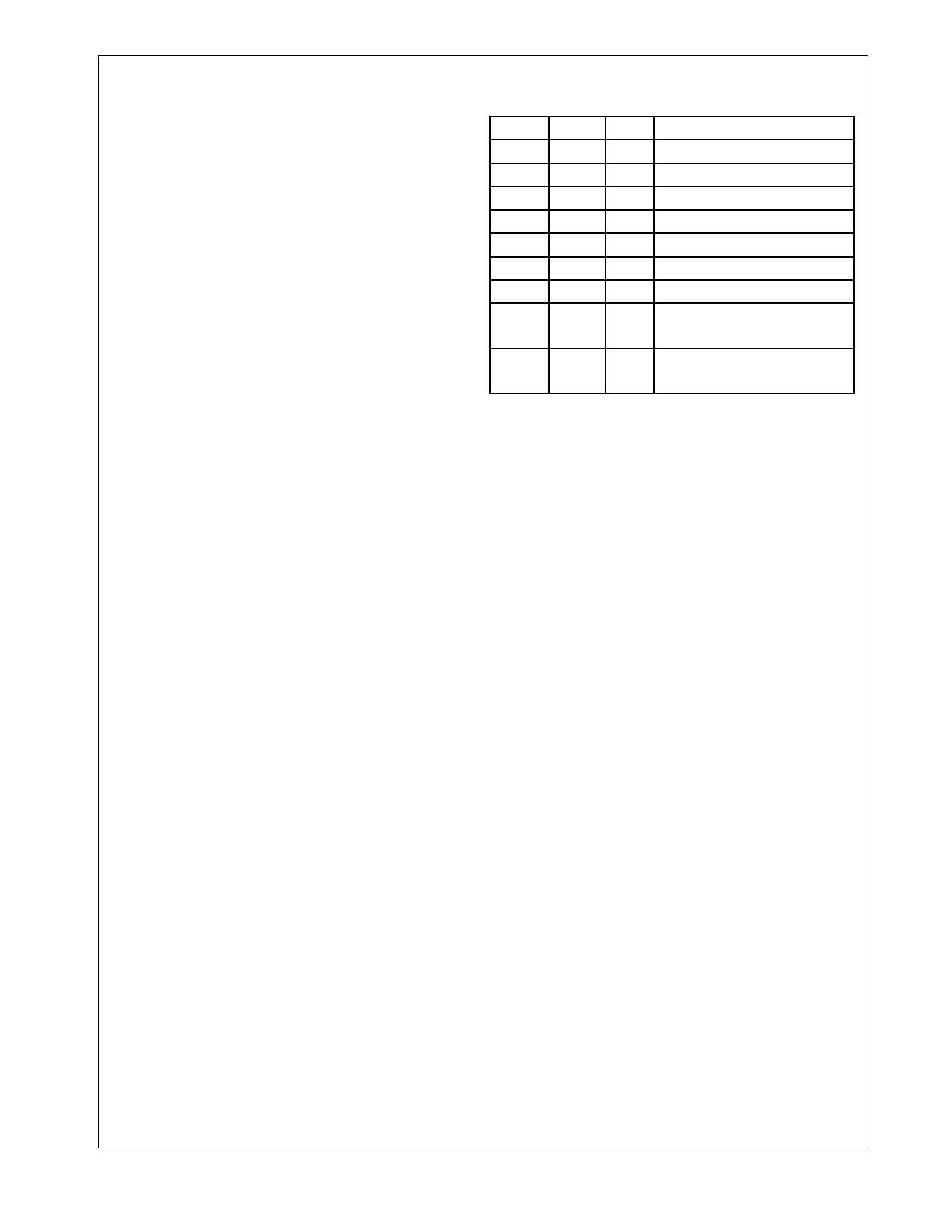

AN_EN

0

0

0

0

AN_EN

1

1

1

1

Table 1. Auto-Negotiation Modes

AN1 AN0

Forced Mode

0 0 10BASE-T, Half-Duplex

0 1 10BASE-T, Full-Duplex

1 0 100BASE-TX, Half-Duplex

1 1 100BASE-TX, Full-Duplex

AN1 AN0

Advertised Mode

0 0 10BASE-T, Half/Full-Duplex

0 1 100BASE-TX, Half/Full-Duplex

1 0 10BASE-T Half-Duplex

100BASE-TX, Half-Duplex

1 1 10BASE-T, Half/Full-Duplex

100BASE-TX, Half/Full-Duplex

2.1.2 Auto-Negotiation Register Control

When Auto-Negotiation is enabled, the DP83846A trans-

mits the abilities programmed into the Auto-Negotiation

Advertisement register (ANAR) at address 04h via FLP

Bursts. Any combination of 10 Mb/s, 100 Mb/s, Half-

Duplex, and Full Duplex modes may be selected. The

BMCR provides software with a mechanism to control the

operation of the DP83846A. The AN0 and AN1 pins do not

affect the contents of the BMCR and cannot be used by

software to obtain status of the mode selected. Bits 1 & 2 of

the PHYSTS register are only valid if Auto-Negotiation is

disabled or after Auto-Negotiation is complete. The Auto-

Negotiation protocol compares the contents of the

ANLPAR and ANAR registers and uses the results to auto-

matically configure to the highest performance protocol

between the local and far-end port. The results of Auto-

Negotiation (Auto-Neg Complete, Duplex Status and

Speed) may be accessed in the PHYSTS register.

Auto-Negotiation Priority Resolution:

— (1) 100BASE-TX Full Duplex (Highest Priority)

— (2) 100BASE-TX Half Duplex

— (3) 10BASE-T Full Duplex

— (4) 10BASE-T Half Duplex (Lowest Priority)

The Basic Mode Control Register (BMCR) at address 00h

provides control for enabling, disabling, and restarting the

Auto-Negotiation process. When Auto-Negotiation is dis-

abled the Speed Selection bit in the BMCR controls switch-

ing between 10 Mb/s or 100 Mb/s operation, and the

Duplex Mode bit controls switching between full duplex

operation and half duplex operation. The Speed Selection

and Duplex Mode bits have no effect on the mode of oper-

ation when the Auto-Negotiation Enable bit is set.

The Basic Mode Status Register (BMSR) indicates the set

of available abilities for technology types, Auto-Negotiation

ability, and Extended Register Capability. These bits are

permanently set to indicate the full functionality of the

DP83846A (only the 100BASE-T4 bit is not set since the

DP83846A does not support that function).

11 www.national.com

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet DP83846A.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| DP83846A | DsPHYTER -Single 10/100 Ethernet Transceiver | National Semiconductor |

| DP83846A | DP83846A DsPHYTER - Single 10/100 Ethernet Transceiver (Rev. E) | Texas Instruments |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |