|

|

PDF DS1010 Data sheet ( Hoja de datos )

| Número de pieza | DS1010 | |

| Descripción | 10-Tap Silicon Delay Line | |

| Fabricantes | Dallas Semiconducotr | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de DS1010 (archivo pdf) en la parte inferior de esta página. Total 6 Páginas | ||

|

No Preview Available !

www.dalsemi.com

DS1010

10-Tap Silicon Delay Line

FEATURES

All-silicon time delay

10 taps equally spaced

Delays are stable and precise

Leading and trailing edge accuracy

Delay tolerance ±5% or ±2 ns, whichever is

greater

Economical

Auto-insertable, low profile

Standard 14-pin DIP or 16-pin SOIC

Low-power CMOS

TTL/CMOS-compatible

Vapor phase, IR and wave solderable

Custom delays available

Fast turn prototypes

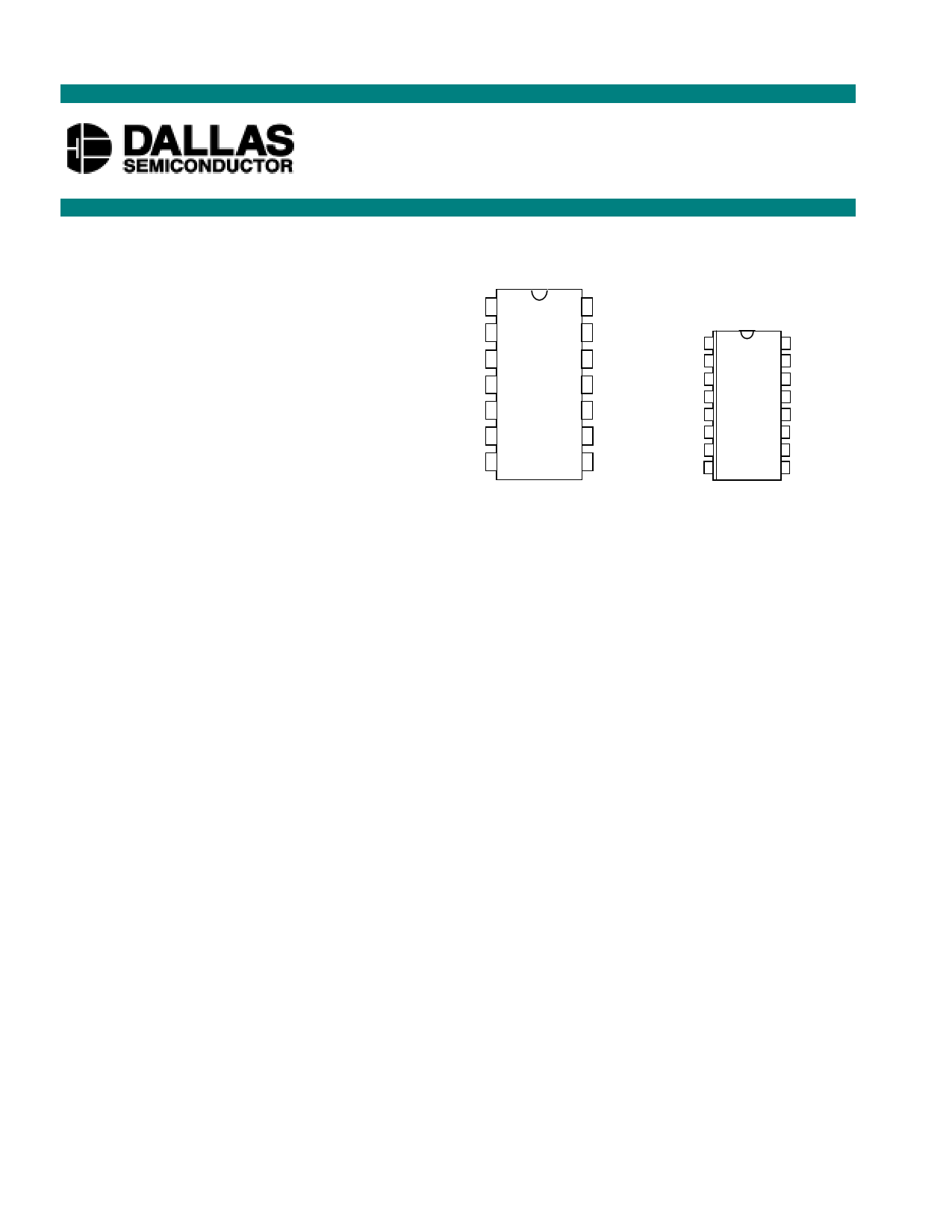

PIN ASSIGNMENT

IN1 1

14 VCC

NC

TAP 2

TAP 4

TAP 6

TAP 8

GND

2

3

4

5

6

7

13 TAP 1

12 TAP 3

IN1 1 16 VCC

NC 2 15 NC

11 TAP 5

NC 3 14 TAP 1

TAP 2 4 13 TAP 3

10 TAP 7 TAP 4 5 12 TAP 5

9 TAP 9 TAP 6 6 11 TAP 7

TAP 8 7 10 TAP 9

8 TAP 10

GND 8

9 TAP 10

DS1010 14-Pin DIP (300-mil) DS1010S 16-Pin SOIC

See Mech. Drawings Section

(300-mil)

See Mech. Drawings Section

PIN DESCRIPTION

TAP 1 - TAP 10 - TAP Output Number

VCC - 5 Volts

GND

- Ground

NC - No Connection

IN - Input

DESCRIPTION

The DS1010 series delay line has ten equally spaced taps providing delays from 5 ns to 500 ns. The

devices are offered in a standard 14-pin DIP which is pin-compatible with hybrid delay lines.

Alternatively, a 16-pin SOIC is available for surface mount technology which reduces PC board area.

Since the DS1010 is an all-silicon solution, better economy is achieved when compared to older methods

using hybrid techniques. The DS1010 series delay lines provide a nominal accuracy of ±5% or ±2 ns,

whichever is greater. The DS1010 reproduces the input logic state at the TAP 10 output after a fixed

delay as specified by the dash number extension of the part number. The DS1010 is designed to produce

both leading and trailing edge with equal precision. Each tap is capable of driving up to 10 74LS type

loads. Dallas Semiconductor can customize standard products to meet special needs. For special requests

and rapid delivery, call (972) 371-4348.

1 of 6

111799

1 page

TEST CIRCUIT Figure 3

DS1010

TERMINOLOGY

Period: The time elapsed between the leading edge of the first pulse and the leading edge of the

following pulse.

tWI (Pulse Width): The elapsed time on the pulse between the 1.5V point on the leading edge and the

1.5V point on the trailing edge, or the 1.5V point on the trailing edge and the 1.5V point on the leading

edge.

tRISE (Input Rise Time): The elapsed time between the 20% and the 80% point on the leading edge of the

input pulse.

tFALL (Input Fall Time): The elapsed time between the 80% and the 20% point on the trailing edge of the

input pulse.

tPLH (Time Delay Rising): The elapsed time between the 1.5V point on the leading edge of the input

pulse and the 1.5V point on the leading edge of any tap output pulse.

tPHL (Time Delay, Falling): The elapsed time between the 1.5V point on the trailing edge of the input

pulse and the 1.5V point on the trailing edge of any tap output pulse.

5 of 6

5 Page | ||

| Páginas | Total 6 Páginas | |

| PDF Descargar | [ Datasheet DS1010.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| DS1010 | 10-Tap Silicon Delay Line | Dallas Semiconducotr |

| DS1012 | 2-in-1 Sub-Miniature Silicon Delay Linw | Dallas Semiconductor |

| DS1013 | 3-in-1 Silicon Delay Line | Dallas Semiconducotr |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |