|

|

PDF DS1337 Data sheet ( Hoja de datos )

| Número de pieza | DS1337 | |

| Descripción | Serial Real-Time Clock | |

| Fabricantes | Dallas Semiconducotr | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de DS1337 (archivo pdf) en la parte inferior de esta página. Total 13 Páginas | ||

|

No Preview Available !

www.maxim-ic.com

www.maxim-ic.com

GENERAL DESCRIPTION

The DS1337 serial real-time clock is a low-power

clock/calendar with two programmable time-of-day

alarms and a programmable square-wave output.

Address and data are transferred serially via a 2-wire,

bidirectional bus. The clock/calendar provides

seconds, minutes, hours, day, date, month, and year

information. The date at the end of the month is

automatically adjusted for months with fewer than 31

days, including corrections for leap year. The clock

operates in either the 24-hour or 12-hour format with

AM/PM indicator.

APPLICATIONS

Handhelds (GPS, POS Terminal, MP3 Player)

Consumer Electronics (Set-Top Box, VCR/Digital

Recording)

Office Equipment (Fax/Printer, Copier)

Medical (Glucometer, Medicine Dispenser)

Telecommunications (Router, Switcher, Server)

Other (Utility Meter, Vending Machine, Thermostat,

Modem)

TYPICAL OPERATING CIRCUIT

DS1337

Serial Real-Time Clock

FEATURES

§ Real-Time Clock (RTC) Counts Seconds,

Minutes, Hours, Day, Date, Month, and Year

with Leap-Year Compensation Valid Up to 2100

§ Two-Wire Serial Interface

§ Two Time-of-Day Alarms

§ Oscillator Stop Flag

§ Programmable Square-Wave Output

– Defaults to 32kHz on Power-Up

§ Available in 8-Pin DIP, SO, or mSOP

ORDERING INFORMATION

PART

DS1337

DS1337S

DS1337U

TEMP RANGE

-40°C to +85°C

-40°C to +85°C

-40°C to +85°C

PIN-PACKAGE

8 DIP (300mil)

8 SO (150mil)

8 mSOP

TOP

MARK

DS1337

DS1337

1337

PIN CONFIGURATIONS

TOP VIEW

X1

X2

INTA

GND

DS1337

VCC

SQW/INTB

SCL

SDA

DIP

X1

X2

INTA

GND

DS1337

VCC

SQW/INTB

SCL

SDA

SO, mSOP

Note: Some revisions of this device may incorporate deviations from published specifications known as errata. Multiple revisions of any device

may be simultaneously available through various sales channels. For information about device errata, click here: www.maxim-ic.com/errata.

1 of 13

REV: 012003

1 page

DS1337

PIN DESCRIPTION

PIN NAME

DESCRIPTION

These signals are connections for a standard 32.768kHz quartz crystal. The internal

1

X1

oscillator circuitry is designed for operation with a crystal having a specified load

capacitance (CL) of 6pF. For more information about crystal selection and crystal layout

considerations, refer to Application Note 58: Crystal Considerations with Dallas Real-

Time Clocks. An external 32.768kHz oscillator can also drive the DS1337. In this

2 X2 configuration, the X1 pin is connected to the external oscillator signal and the X2 pin is

floated.

Interrupt Output. When enabled, INTA is asserted low when the time/day/date matches

3

INTA

the values set in the alarm registers. This pin is an open-drain output and requires an

external pullup resistor.

4

GND

DC power is provided to the device on these pins.

5

SDA

Serial Data Input/Output. SDA is the input/output pin for the 2-wire serial interface. The

SDA pin is open-drain output and requires an external pullup resistor.

6 SCL Serial Clock Input. SCL is used to synchronize data movement on the serial interface.

7

SQW/INTB

Square-Wave/Interrupt Output. Programmable square-wave or interrupt output signal. It

is an open-drain output and requires an external pullup resistor.

8

VCC

DC power is provided to the device on these pins.

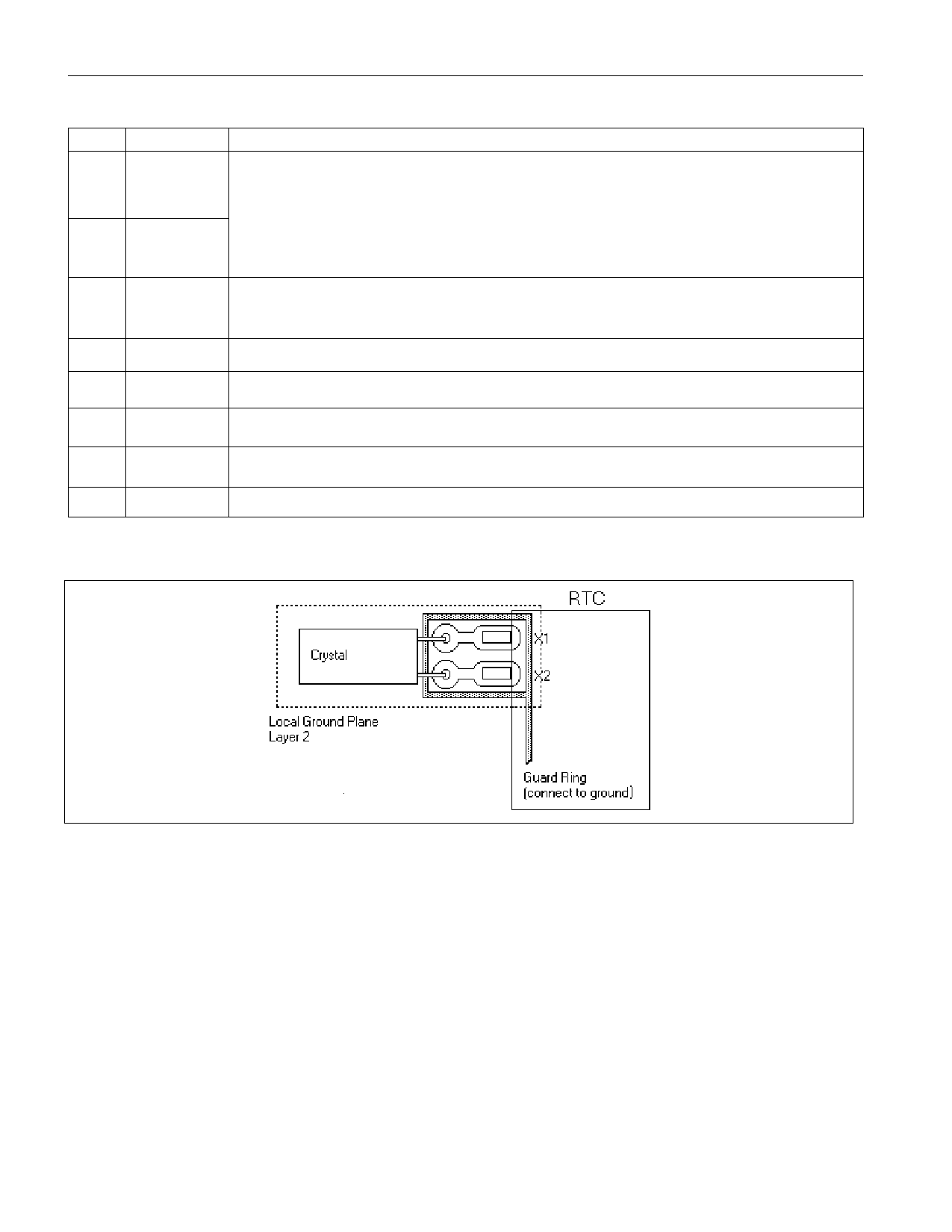

Figure 1. Recommended Layout for Crystal

5 of 13

5 Page

DS1337

2-WIRE SERIAL DATA BUS

The DS1337 supports a bidirectional 2-wire bus and data transmission protocol. A device that sends data

onto the bus is defined as a transmitter and a device receiving data as a receiver. The device that controls

the message is called a master. The devices that are controlled by the master are referred to as slaves. A

master device that generates the serial clock (SCL), controls the bus access, and generates the START

and STOP conditions must control the bus. The DS1337 operates as a slave on the 2-wire bus. Within the

bus specifications a standard mode (100kHz maximum clock rate) and a fast mode (400kHz maximum

clock rate) are defined. The DS1337 works in both modes. Connections to the bus are made through the

open-drain I/O lines SDA and SCL.

The following bus protocol has been defined (Figure 4):

§ Data transfer may be initiated only when the bus is not busy.

§ During data transfer, the data line must remain stable whenever the clock line is HIGH. Changes in

the data line while the clock line is HIGH are interpreted as control signals.

Accordingly, the following bus conditions have been defined:

Bus not busy: Both data and clock lines remain HIGH.

Start data transfer: A change in the state of the data line, from HIGH to LOW, while the clock is

HIGH, defines a START condition.

Stop data transfer: A change in the state of the data line, from LOW to HIGH, while the clock line is

HIGH, defines the STOP condition.

Data valid: The state of the data line represents valid data when, after a START condition, the data line

is stable for the duration of the HIGH period of the clock signal. The data on the line must be changed

during the LOW period of the clock signal. There is one clock pulse per bit of data.

Each data transfer is initiated with a START condition and terminated with a STOP condition. The

number of data bytes transferred between START and STOP conditions are not limited, and are

determined by the master device. The information is transferred byte-wise and each receiver

acknowledges with a ninth bit.

Acknowledge: Each receiving device, when addressed, is obliged to generate an acknowledge after the

reception of each byte. The master device must generate an extra clock pulse that is associated with this

acknowledge bit.

A device that acknowledges must pull down the SDA line during the acknowledge clock pulse in such a

way that the SDA line is stable LOW during the HIGH period of the acknowledge related clock pulse. Of

course, setup and hold times must be taken into account. A master must signal an end of data to the slave

by not generating an acknowledge bit on the last byte that has been clocked out of the slave. In this case,

the slave must leave the data line HIGH to enable the master to generate the STOP condition.

11 of 13

11 Page | ||

| Páginas | Total 13 Páginas | |

| PDF Descargar | [ Datasheet DS1337.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| DS1330AB | (DS1330Y / DS1330AB) 256k Nonvolatile SRAM with Battery Monitor | Dallas Semiconducotr |

| DS1330W | 3.3V 256K Nonvolatile SRAM with Battery Monitor | Dallas Semiconducotr |

| DS1330Y | (DS1330Y / DS1330AB) 256k Nonvolatile SRAM with Battery Monitor | Dallas Semiconducotr |

| DS1336 | Afterburner Chip | Dallas Semiconducotr |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |