|

|

PDF PDM41256 Data sheet ( Hoja de datos )

| Número de pieza | PDM41256 | |

| Descripción | 256K Static RAM 32K x 8-Bit | |

| Fabricantes | ETC | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de PDM41256 (archivo pdf) en la parte inferior de esta página. Total 8 Páginas | ||

|

No Preview Available !

Features

s High-speed access times

Com’l: 7, 8, 10, 12, and 15 ns

Ind’l: 8, 10, 12, and 15 ns

s Low power operation (typical)

- PDM41256SA

Active: 400 mW

Standby: 150 mW

- PDM41256LA

Active: 350 mW

Standby: 25 mW

s Single +5V (±10%) power supply

s TTL-compatible inputs and outputs

s Packages

Plastic SOJ (300 mil) - TSO

Plastic TSOP - T

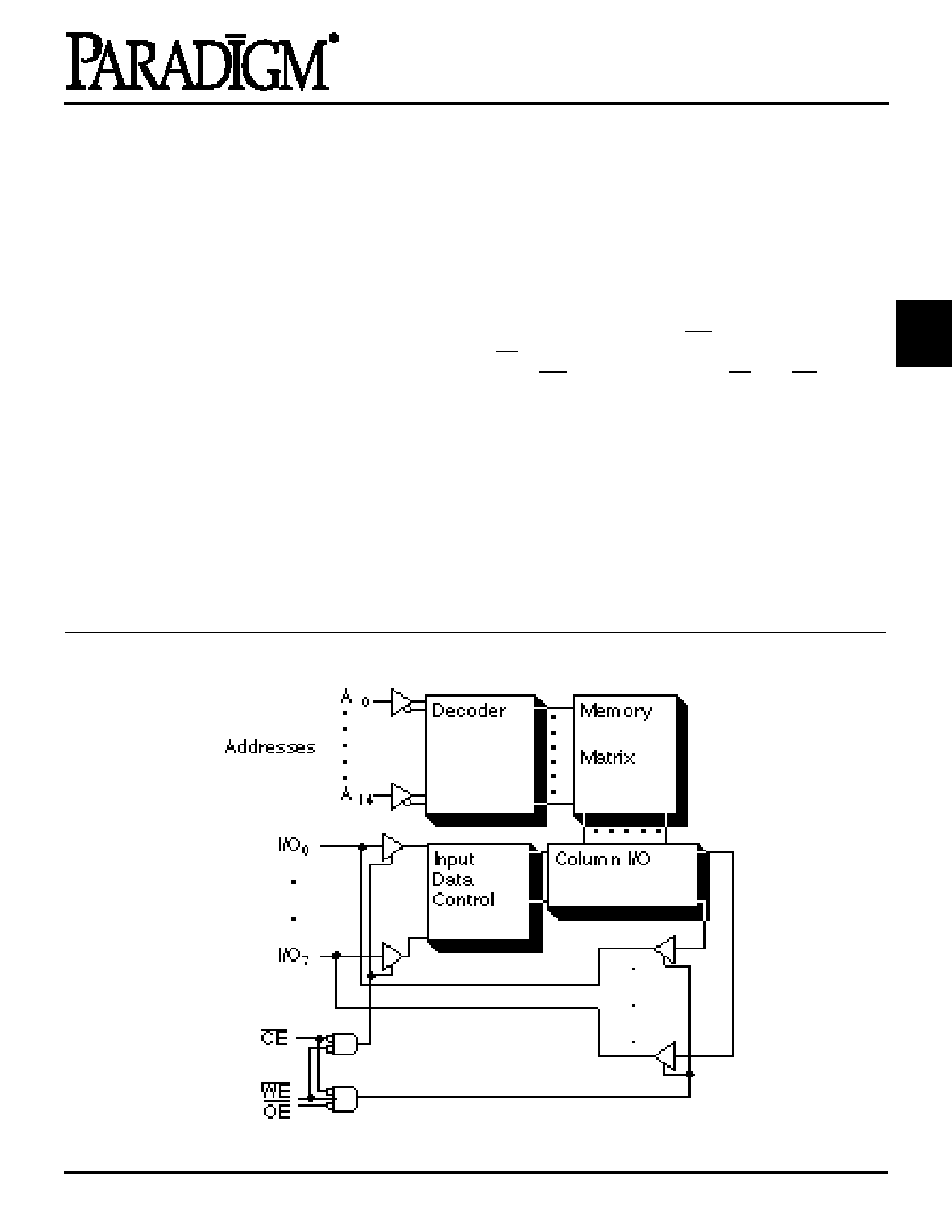

Functional Block Diagram

Rev. 2.0 - 7/17/96

PDM41256

256K Static RAM

32K x 8-Bit

1

Description

The PDM41256 is a high-performance CMOS static

RAM organized as 32,768 x 8 bits. This product is

produced in Paradigm’s proprietary CMOS

technology which offers the designer the highest

speed parts. Writing to this device is accomplished

when the write enable (WE) and the chip enable

(CE) inputs are both LOW. Reading is accomplished

when WE remains HIGH and CE and OE are both

LOW.

The PDM41256 operates from a single +5V power

supply and all the inputs and outputs are fully TTL-

compatible. The PDM41256 comes in two versions,

the standard power version PDM41256SA and a low

power version the PDM41256LA. The two versions

are functionally the same and only differ in their

power consumption.

The PDM41256 is available in a 28-pin plastic TSOP

and a 28-pin 300-mil plastic SOJ.

2

3

4

5

6

7

8

9

10

11

12

3-33

1 page

PDM41256

Read Cycle No. 1(1)

Read Cycle No. 2(2)

AC Electrical Characteristics

Description

--7(6)

--8(6)

-10(6)

-12

-15

READ Cycle

Sym Min. Max. Min. Max. Min. Max. Min. Max. Min. Max. Units

READ cycle time

tRC 7

8 10 12 15 ns

Address access time

tAA 7 8 10 12 15 ns

Chip enable access time

tACE

7

8 10 12 15 ns

Output hold from address change

Chip enable to output in low Z(3, 4, 5)

Chip disable to output in high Z(3, 4, 5)

Chip enable to power up time(4)

Chip disable to power down time(4)

tOH

tLZCE

tHZCE

tPU

tPD

3

5

0

3 3 3 3 ns

5 5 5 5 ns

5 6 6 6 6 ns

0 0 0 0 ns

7 8 10 12 15 ns

Output enable access time

tAOE

5

5

5

6

8 ns

Output enable to output in low Z(4, 5)

tLZOE 0

0

0

0

0

ns

Output disable to output in high Z(4, 5)

tHZOE

5

6

6

6

6 ns

SHADED AREA = PRELIMINARY DATA.

Notes referenced are after Data Retention Table.

1

2

3

4

5

6

7

8

9

10

11

12

Rev. 2.0 - 7/17/96

3-37

5 Page | ||

| Páginas | Total 8 Páginas | |

| PDF Descargar | [ Datasheet PDM41256.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| PDM41256 | 256K Static RAM 32K x 8-Bit | ETC |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |