|

|

PDF PDI1394P25BD Data sheet ( Hoja de datos )

| Número de pieza | PDI1394P25BD | |

| Descripción | 1-port 400 Mbps physical layer interface | |

| Fabricantes | NXP Semiconductors | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de PDI1394P25BD (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

INTEGRATED CIRCUITS

PDI1394P25

1-port 400 Mbps physical layer interface

Preliminary data

Supersedes data of 2001 Jul 18

2001 Sep 06

Philips

Semiconductors

1 page

Philips Semiconductors

1-port 400 Mbps physical layer interface

Preliminary data

PDI1394P25

5.0 PIN DESCRIPTION

Name

Pin Type

LQFP

Pin

Numbers

AGND

Supply

32, 33,

39, 48,

49, 50

AVDD

Supply

30, 31,

42, 51,

52

LFBGA

Ball

Numbers

A1, A5,

A8, B1,

B2, B7

B8, C2,

C3, C5,

C7, D2

I/O

—

—

BRIDGE

CMOS

28

D6

I

C/LKON CMOS 5 V tol 19

F6

I/O

CNA

CPS

CMOS

CMOS

3

24

CTL0,

CTL1

CMOS 5 V tol 4

5

F3

E5

G3

G4

O

I

I/O

Description

Analog circuit ground terminals. These terminals should be tied together

to the low impedance circuit board ground plane.

Analog circuit power terminals. A combination of high frequency

decoupling capacitors on each side are suggested, such as paralleled

0.1 µF and 0.001 µF. These supply terminals are separated from

PLLVDD and DVDD internal to the device to provide noise isolation. They

should be tied at a low impedance point on the circuit board.

BRIDGE input. This input is used to set the Bridge_Aware bits located in

the Vendor-Dependent register Page 7, base address 1001b, bit

positions 6 and 7. This pin is sampled during a hardware reset (RESET

low). When the BRIDGE pin is tied low (or through a 1 kΩ resistor to

accommodate other vendor’s pin-compatible chips), the Bridge_Aware

bits are set to “00” indicating a “non-bridge device.” When the BRIDGE

pin is tied high, the Bridge_Aware bits are set to “11” indicating a “1394.1

bridge compliant” device. The default setting of the Bridge_Aware bits

can be overridden by writing to the register. The Bridge_Aware bits are

reported in the self-ID packet at bit positions 18 and 19.

Bus Manager Contender programming input and link-on output. On

hardware reset, this terminal is used to set the default value of the

contender status indicated during self-ID. Programming is done by tying

the terminal through a 10-kΩ resistor to a high (contender) or low (not

contender). The resistor allows the link-on output to override the input.

If this pin is connected to a LLC driver pin for setting Bus Manager/IRM

contender status, then a 10-kΩ series resistor should be placed on this

line between the PHY and the LLC to prevent possible contention. In this

case. the pull-high or pull-low resistors mentioned in the previous

paragraph should not be used. Refer to Figure 9.

Following hardware reset, this terminal is the link-on output, which is

used to notify the LLC to power-up and become active. The link-on

output is a square-wave signal with a period of approximately 163 ns (8

SYSCLK cycles) when active. The link-on output is otherwise driven low,

except during hardware reset when it is high impedance.

The link-on output is activated if the LLC is inactive (LPS inactive or the

LCtrl bit cleared) and when:

a) the PHY receives a link-on PHY packet addressed to this node,

b) the PEI (port-event interrupt) register bit is 1, or

c) any of the CTOI (configuration-timeout interrupt), CPSI

(cable-power-status interrupt), or STOI (state-timeout interrupt)

register bits are 1 and the RPIE (resuming-port interrupt enable)

register bit is also 1.

Once activated, the link-on output will continue active until the LLC

becomes active (both LPS active and the LCtrl bit set). The PHY also

deasserts the link-on output when a bus-reset occurs unless the link-on

output would otherwise be active because one of the interrupt bits is set

(i.e., the link-on output is active due solely to the reception of a link-on

PHY packet).

NOTE: If an interrupt condition exists which would otherwise cause the

link-on output to be activated if the LLC were inactive, the link-on output

will be activated when the LLC subsequently becomes inactive.

Cable Not Active output. This terminal is asserted high when there are

no ports receiving incoming bias voltage.

Cable Power Status input. This terminal is normally connected to cable

power through a 390 kΩ resistor. This circuit drives an internal

comparator that is used to detect the presence of cable power.

Control I/Os. These bi-directional signals control communication

between the PDI1394P25 and the LLC. Bus holders are built into

these terminals.

2001 Sep 06

5

5 Page

Philips Semiconductors

1-port 400 Mbps physical layer interface

Preliminary data

PDI1394P25

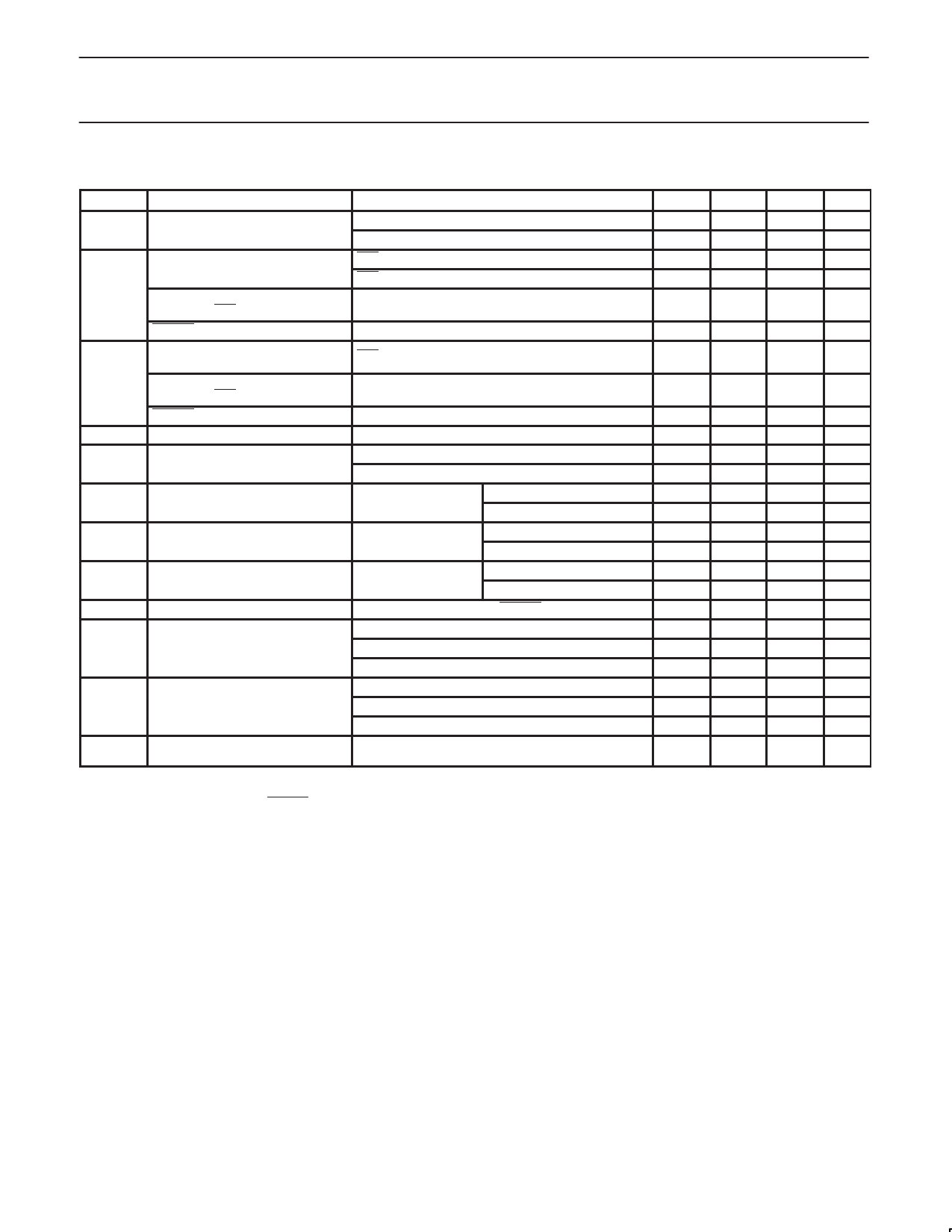

9.0 RECOMMENDED OPERATING CONDITIONS

SYMBOL

PARAMETER

CONDITION

MIN

VDD Supply voltage

Source power node

Non-source power node

3.0

2.7 1

High-level input voltage, LREQ,

ISO = VDD, VDD >= 2.7 V

CTL0, CTL1, D0-D7

ISO = VDD, VDD >= 3.0 V

VIH High-level input voltage, C/LKON2,

PC0–PC2, ISO, PD

2.3

2.6

0.7 VDD

RESET

Low-level input voltage, LREQ,

CTL0, CTL1, D0–D7

ISO = VDD

VIL Low-level input voltage, C/LKON2,

PC0–PC2, ISO, PD,

0.6 VDD

—

—

RESET

—

IO Output current

TPBIAS outputs

TPA, TPB cable inputs, during data reception

VID

Differential input voltage amplitude

TPA, TPB cable inputs, during data arbitration

–6

118

168

VIC-100

TPB common-mode input voltage

Speed signaling off Source power node

or S100 speed signal Non-source power node

1.165

1.165

VIC-200 TPB common-mode input voltage S200 speed signal

Source power node

Non-source power node

0.935

0.935

VIC-400 TPB common-mode input voltage S400 speed signal

Source power node

Non-source power node

0.523

0.523

tPU Power-up reset time

Receive input jitter

Set by capacitor between RESET pin and GND

TPA, TPB cable inputs, S100 operation

TPA, TPB cable inputs, S200 operation

2

—

—

TPA, TPB cable inputs, S400 operation

—

Receive input skew

Between TPA and TPB cable inputs, S100 operation

Between TPA and TPB cable inputs, S200 operation

—

—

Between TPA and TPB cable inputs, S400 operation —

fXTAL

Crystal or external clock frequency

Crystal connected according to Figure 10 or external

clock input at pin XI

24.5735

NOTES:

1. For a node that does not source power to the bus (see Section 4.2.2.2 in the IEEE 1394-1995 standard).

2. C/LKON is only an input when RESET = 0.

TYP

3.3

3.0

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

24.576

MAX

3.6

3.6

—

—

—

—

0.7

0.2 VDD

0.3 VDD

2.5

260

265

2.515

2.0151

2.515

2.0151

2.515

2.0151

—

1.08

0.5

0.315

0.8

0.55

0.5

24.5785

UNIT

V

V

V

V

V

V

V

—

mA

mV

mV

V

V

V

V

V

V

ms

ns

ns

ns

ns

ns

ns

MHz

2001 Sep 06

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet PDI1394P25BD.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| PDI1394P25BD | 1-port 400 Mbps physical layer interface | NXP Semiconductors |

| PDI1394P25BY | 1-port 400 Mbps physical layer interface | NXP Semiconductors |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |