|

|

PDF PCM1738 Data sheet ( Hoja de datos )

| Número de pieza | PCM1738 | |

| Descripción | DIGITAL-TO-ANALOG CONVERTER | |

| Fabricantes | Burr-Brown Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de PCM1738 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

PCM1738

PCM1738

www.ti.com

24-Bit, 192kHz Sampling,

Advanced Segment, Audio-Stereo

DIGITAL-TO-ANALOG CONVERTER

FEATURES

24-BIT RESOLUTION

ANALOG PERFORMANCE (VCC = +5V):

Dynamic Range: 117dB typ

SNR: 117dB typ

THD+N: 0.0004% typ

Full-Scale Output: 2.2Vrms (at post amp)

DIFFERENTIAL CURRENT OUTPUT: 2.48mA

SAMPLING FREQUENCY: 10kHz to 200kHz

SYSTEM CLOCK: 128, 192, 256, 384, 512,

or 768fS with Auto Detect

ACCEPTS 16-, 20-, AND 24-BIT AUDIO DATA

DATA FORMATS: Standard, I2S, and Left-

Justified

8x OVERSAMPLING DIGITAL FILTER:

Stopband Attenuation: –82dB

Passband Ripple: 0.002dB

OPTIONAL INTERFACE TO EXTERNAL

DIGITAL FILTER AVAILABLE

OPTIONAL INTERFACE TO DSD DE-

CODER FOR SACD PLAYBACK

USER-PROGRAMMABLE MODE CONTROLS:

Digital Attenuation: 0dB to –120dB, 0.5dB/Step

Digital De-Emphasis

Digital Filter Roll-Off: Sharp or Slow

Soft Mute

Zero Detect Mute

Zero Flags for Each Output

DUAL-SUPPLY OPERATION:

+5V Analog, +3.3V Digital

5V TOLERANT DIGITAL INPUTS

SMALL SSOP-28 PACKAGE

APPLICATIONS

AV RECEIVERS

DVD MOVIE PLAYERS

SACD PLAYERS

HDTV RECEIVERS

CAR AUDIO SYSTEMS

DIGITAL MULTI-TRACK RECORDERS

OTHER MULTICHANNEL AUDIO SYSTEMS

DESCRIPTION

The PCM1738 is a CMOS, monolithic, Integrated Cir-

cuit (IC) that includes stereo Digital-to-Analog Convert-

ers (DACs) and support circuitry in a small SSOP-28

package. The data converters utilize a newly developed

advanced segment DAC architecture to achieve excel-

lent dynamic performance and improved tolerance to

clock jitter. The PCM1738 provides balanced current

outputs, allowing the user to optimize analog perfor-

mance externally, and accepts industry standard audio

data formats with 16- to 24-bit data, providing easy

interfacing to audio DSP and decoder chips. Sampling

rates up to 200kHz are supported. The PCM1738 also

has two optional modes of operation: an external digital-

filter mode (for use with the DF1704, DF1706, and

PMD200), and a DSD decoder interface for SACD

playback applications. A full set of user-programmable

functions are accessible through a 4-wire serial control

port that supports register write and read functions.

Copyright © 2000, Texas Instruments Incorporated

SBAS174B

Printed in U.S.A. February, 2002

1 page

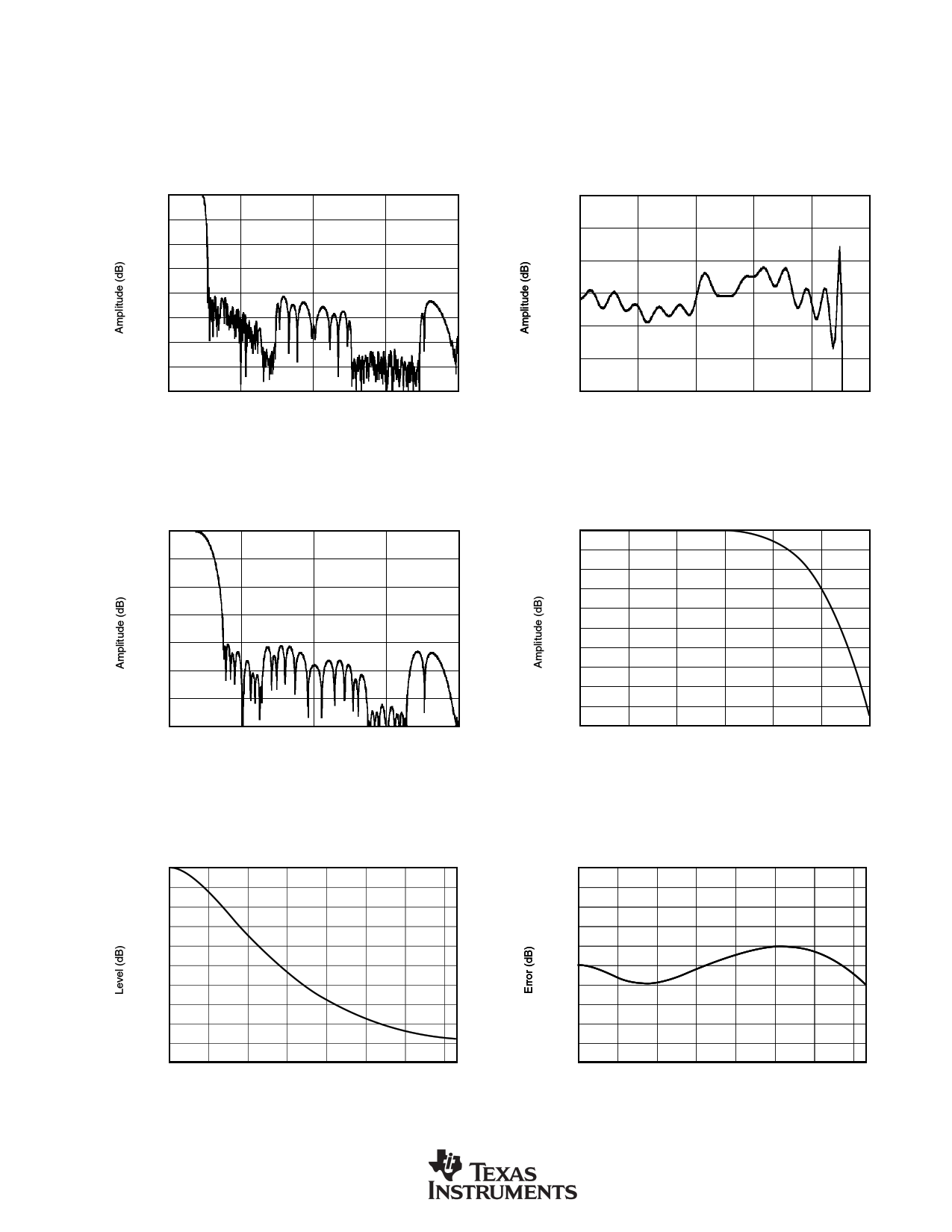

TYPICAL PERFORMANCE CURVES

All specifications at TA = +25 C, VDD = +3.3V, VCC = +5V, SCKI = 256fS (fS = 44.1kHz), and 24-bit input data, unless otherwise noted.

DIGITAL FILTER

Digital Filter (De-Emphasis Off, fS = 44.1kHz)

0

–20

–40

–60

–80

–100

–120

–140

–160

0

FREQUENCY RESPONSE (Sharp Roll-Off)

123

Frequency (x fS)

4

0.003

0.002

0.001

0

–0.001

–0.002

–0.003

0

PASSBAND RIPPLE (Sharp Roll-Off)

0.1 0.2 0.3 0.4 0.5

Frequency (x fS)

0

–20

–40

–60

–80

–100

–120

–140

0

FREQUENCY RESPONSE (Slow Roll-Off)

123

Frequency (x fS)

4

De-Emphasis Error

0.0

–1.0

–2.0

–3.0

–4.0

–5.0

–6.0

–7.0

–8.0

–9.0

–10.0

0

DE-EMPHASIS (fS = 32kHz)

2 4 6 8 10 12 14

Frequency (kHz)

PCM1738

SBAS174B

0

–2

–4

–6

–8

–10

–12

–14

–16

–18

–20

0

TRANSITION CHARACTERISTICS (Slow Roll-Off)

0.1 0.2 0.3 0.4 0.5

Frequency (x fS)

0.6

0.5

0.4

0.3

0.2

0.1

0.0

–0.1

–0.2

–0.3

–0.4

–0.5

0

DE-EMPHASIS ERROR (fS = 32kHz)

2 4 6 8 10 12 14

Frequency (kHz)

5

5 Page

SYSTEM CLOCK AND RESET

FUNCTIONS

SYSTEM CLOCK INPUT

The PCM1738 requires a system clock for operating the

digital interpolation filters and advanced segment DAC

modulators. The system clock is applied at the SCKI input

(pin 7). The PCM1738 has a system-clock detection circuit

that automatically senses if the system clock is operating at

128fS to 768fS. Table I shows examples of system-clock

frequencies for common audio sampling rates.

Figure 1 shows the timing requirements for the system clock

input. For optimal performance, it is important to use a clock

source with low phase jitter and noise. The PLL1700 multi-

clock generator is an excellent choice for providing the

PCM1738 system clock.

SYSTEM CLOCK OUTPUT

A buffered version of the system clock input is available at

the SCKO output (pin 10). SCKO can operate at either full

(fSCKI) or half (fSCKI/2) rate. The SCKO output frequency

may be programmed using the CLKD bit of Control Regis-

ter 19. The SCKO output pin can also be enabled or disabled

using the CLKE bit of Control Register 19. The default is

SCKO enabled.

POWER-ON AND EXTERNAL RESET FUNCTIONS

The PCM1738 includes a power-on reset function (see

Figure 2). The system clock input at SCKI should be active

for at least one clock period prior to VDD = 2.0V. With the

system clock active, and VDD > 2.0V, the power-on reset

function will be enabled. The initialization sequence re-

quires 1024 system clocks from the time VDD > 2.0V. After

the initialization period, the PCM1738 will be set to its reset

default state, as described in the Mode Control Register

section of this data sheet.

The PCM1738 also includes an external reset capability

using the RST input (pin 1). This allows an external control-

ler or master reset circuit to force the PCM1738 to initialize

to its reset default state.

See Figure 3 for external reset operation and timing. The

RST pin is set to a logic “0” for a minimum of 20ns. The

RST pin is then set to a logic “1” state that starts the

initialization sequence that requires 1024 system clock peri-

ods. After the initialization sequence is complete, the

PCM1738 will be set to its reset default state, as described

in the Mode Control Register section of this data sheet.

The external reset is especially useful in applications where

there is a delay between the PCM1738 power-up and system

clock activation. In this case, the RST pin should be held at

a logic “0” level until the system clock has been activated.

The RST pin may then be set to a logic “1” state to start the

initialization sequence.

SAMPLING

FREQUENCY

32kHz

44.1kHz

48kHz

96kHz

192kHz

128fS

4.0960

5.6488

6.1440

12.2880

24.5760

192fS

6.1440

8.4672

9.2160

18.4320

36.8640

SYSTEM CLOCK FREQUENCY (fSCLK) (MHz)

256fS

8.1920

11.2896

12.2880

24.5760

49.1520

384fS

12.2880

16.9344

18.4320

36.8640

73.7280

NOTE: (1) This system clock is not supported for the given sampling frequency.

TABLE I. System Clock Rates for Common Audio Sampling Frequencies.

512fS

16.3840

22.5792

24.5760

49.1520

See Note (1)

768fS

24.5760

33.8688

36.8640

73.7280

See Note (1)

“H”

System Clock

“L”

tSCKH

tSCKL

System clock pulse

cycle time(1)

System Clock Pulse Width HIGH tSCKH: 5ns (min)

System Clock Pulse Width LOW tSCKL: 5ns (min)

FIGURE 1. System Clock Input Timing.

2.0V

0.8V

PCM1738

SBAS174B

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet PCM1738.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| PCM1730 | 24-Bit 192-kHz Sampling Advanced Segment Audio Stereo Digital-to-Analog Conver | Texas Instruments |

| PCM1732 | 24-Bit/ 96kHz/ Stereo Audio DIGITAL-TO-ANALOG CONVERTER With HDCD Decoder | Burr-Brown Corporation |

| PCM1733 | Stereo Audio DIGITAL-TO-ANALOG CONVERTER 18 Bits/ 96kHz Sampling | Burr-Brown Corporation |

| PCM1733 | SoundPlus Stereo Audio Digital-To-Analog Converter 18 Bits 96kHz Sampling | Texas Instruments |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |