|

|

PDF PCM16C010 Data sheet ( Hoja de datos )

| Número de pieza | PCM16C010 | |

| Descripción | Configurable PC Card Interface Chip | |

| Fabricantes | National Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de PCM16C010 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

August 1996

PCM16C010

Configurable PC Card Interface Chip

General Description

National’s PCM16C010 acts as a standard interface be-

tween the PC Card Host bus and local card busses found on

I O and memory PC Cards This device allows the card de-

signer to focus on the design of the I O functions while

providing a one-chip solution for I O memory window con-

trol EEPROM interfacing and power management

The PCM16C010 provides a PC Card interface for any ISA

like function which allows it to be placed on a PC Card

In addition the PCM16C010 provides the capability to con-

figure the function as a NAND Flash (NM29N16) interface

supporting all of the necessary control signals required to

handshake with NAND Flash (NM29N16) memory devices

The PCM16C010 is fully compliant with the PC Card Stan-

dard This IC allows the system software to setup an I O

decode window and provides the Attribute memory decode

control that allow attribute read and write data transfers

Note PC Card refers to technology developed to the PC

Card Standards determined by the PCMCIA Standards

Committee

Features

Y PC Card bus interface

Y PC Card Standard configuration registers

Y 100 pin TQFP package

Y Configurable as NAND Flash (NM29N16) interface

Y Serial EEPROM Interface compatible with

MICROWIRETM EEPROM protocol

Y 1-kbyte on chip RAM for attribute memory which shad-

ows the CIS and is used for loading static registers

Y Address decoding and control for I O functions

Y Power management and clock control

Y Common memory logic for common memory devices in-

cluding NOR Flash devices

Y Operating voltage range e VCC(opr) e 3VE5 0V

1 0 System Diagram

FIGURE 1-1

TL F 12147 – 1

TRI-STATE is a registered trademark of National Semiconductor Corporation

MICROWIRETM is a trademark of National Semiconductor Corporation

C1996 National Semiconductor Corporation TL F 12147

RRD-B30M17 Printed in U S A

http www national com

1 page

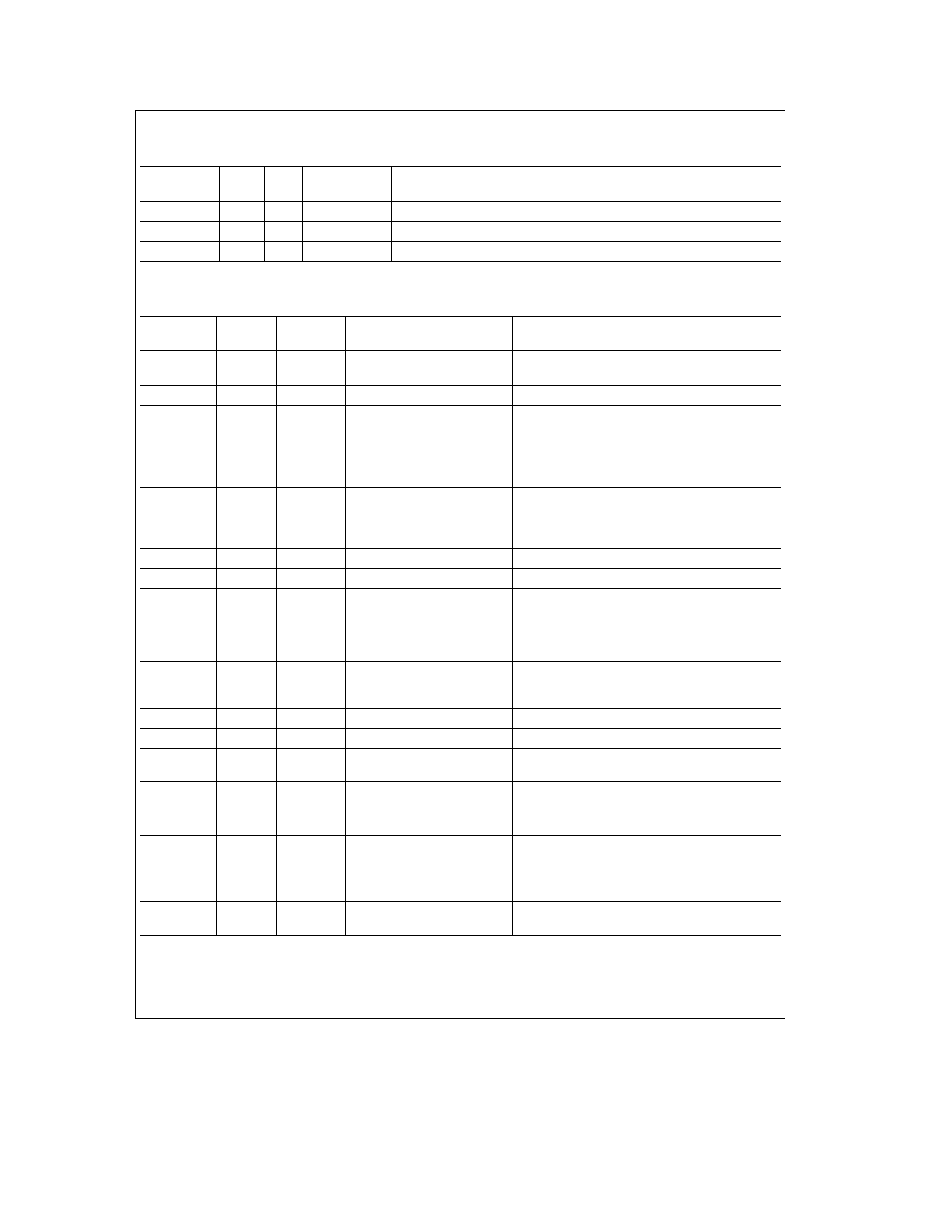

3 0 Pinout Description (Continued)

TABLE 3-2 Serial EEPROM Interface Pins

Pin

Name

Pin Pin

Level

Internal

Type No Compatibility Resistor

Description

EEDI EEDO I O 81 TTL 6 mA

Serial Data in to from EEPROM

EECS

O 83 CMOS 6 mA

EEPROM Chip Select

EESK

O 82 CMOS 6 mA

EEPROM Clock Freq e MCLK(0) 32

Note The Enable EEPROM function is performed in software by writing to the EEPROM Control Register The Enable EEPROM bit will default to low (disabled)

upon power on

TABLE 3-3 Card-Side Interface Pins

Pin

Name

LDATA(15 0)

SPK IN

RI IN

CIORD

Pin

Type

IO

I

I (Note 2)

O

Pin

No

1–5 7–13

97 – 100

86

23

19

CIOWR

O 18

CWAIT

CS

BHE

I (Note 2)

O

O

31

30

17

READY

I 27

CINT

SRESET

IOCS16

PCNTL

MCLK

FCLK

MEMWEH

MEMWEL

I (Note 2)

O

I (Note 2)

O

I

O

O Tri

O Tri

29

28

26

14

24

25

21

22

Level

Compatibility

TTL 6 mA

TTL Schmitt

TTL Schmitt

CMOS 6 mA

CMOS 6 mA

TTL

CMOS 6 mA

CMOS 6 mA

TTL

TTL Schmitt

CMOS 6 mA

TTL

CMOS 6 mA

TTL Schmitt

CMOS 6 mA

CMOS 6 mA

CMOS 6 mA

Internal

Resistor

Hold Circuit

(Note 1)

l100k to VCC

l10k to VCC

l10k to VCC

Description

Card-side Data Bus

Input Audio Signal

Ring Indicator for function 0

I O read signals are passed through from HIORD

according to the expression shown below when a

valid address is decoded

CIORD e HIORD a REG a (CE1 CE2

)

I O write signals are passed through from HIOWR

according to the expression shown below when a

valid address is decoded

CIOWR e HIOWR a REG a (CE1 CE2

)

Card-side transaction wait state input

Chip select for function

Byte high enable When de-asserted and CS( )

asserted an 8-bit access on LDATA(7 0) is in

progress This holds for both odd and even

addresses When asserted and CS( ) asserted a

16-bit access on LDATA(15 0) is in progress

Indicates that the function is either READY or

EREADY (i e - Busy) This signal is used to assert

the Rdy Bsy bit in Pin Replacement Registers

Card-side interrupt input signal

Signals reset to Card-side function

This pin is asserted during an access to a function if

that function is capable of a 16-bit access

Power management control signals or general

output

Input clock for function

Output clock signal for function This may be gated

on off or be a divided value of MCLK

Common Memory write output for upper byte of data

word

Common Memory write output for lower byte of data

word

Note 1 The Hold Circuit will hold the signal to the logic value it was last set to when the line is TRI-STATE This will insure that inputs do not float during a

TRI-STATE condition

Note 2 The CWAIT CINT RI IN and IOCS16 pins are outputs (O) when the function is configured for the NAND Flash (NM29N16) Mode

5 http www national com

5 Page

5 0 Functional Description (Continued)

NAND EN This bit if set to one (1) configures the func-

tion as a NAND Flash (NM29N16) interface (see Section

5 4 4 for specific function details) If set to zero (0) the func-

tion assumes normal I O interface functionality

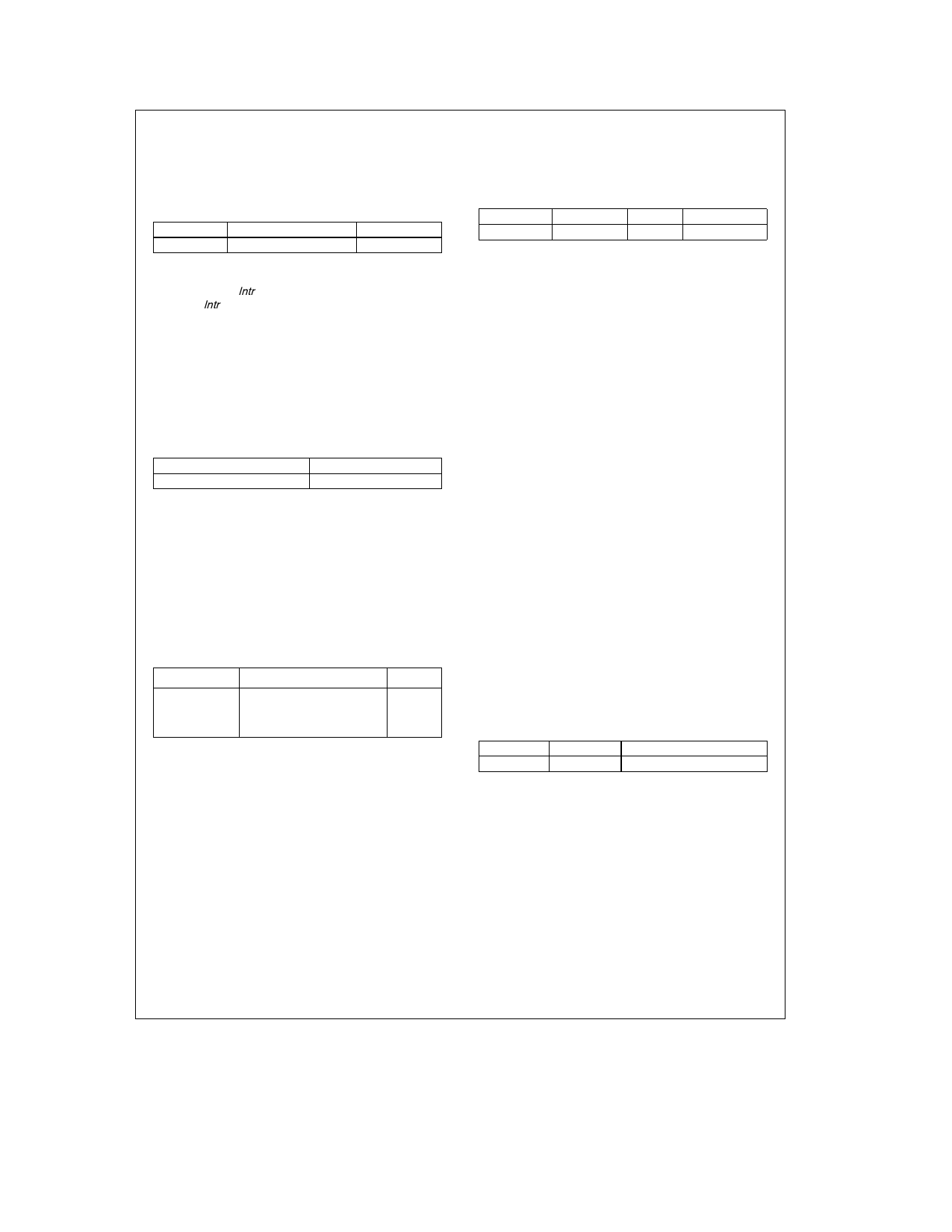

Watchdog Time-Out Register

0x03FC

D7

RFU

D6

Wait Tout Enable

D5 – D0

RFU

Wait Tout Enable When this bit is set to a one (1) the

HWAIT time-out watchdog timer is enabled In addition

the ability to set Intr in the Function Configuration Option

Register Intr in the Card Configuration Register and

IREQ is enabled once the watchdog timer expires The

watchdog timer may expire if HWAIT is asserted for more

than approximately 11 2 ms when MCLK is set to 20 MHz

This prevents the system from hanging due to prolonged

HWAIT assertions If this bit is reset to zero (0) Wait

Tout and its associated interrupt capability is disabled during

HWAIT assertions

ID Register

0x1000

This read only register provides the software with IC revision

information

D7 – D3

PCM16C010 Code e 00010b

D2 – D0

Revision Code e 001b

NSC PCM16C010 Code This code may be used to identi-

fy the NSC PCM16C010 IC The value of bits D7–D3 of this

register is 00010 which when appended to the three bits of

the revision code produce 00010 xxx which is 1x hex

Revision Code This will uniquely identify the silicon ver-

sion of the PCM16C010 IC as 001b

EEPROM Access

In order to avoid accidental EEPROM overwrite the

PCM16C010 utilizes two registers that must be written with

the proper byte sequence in order to enable EEPROM

writes In order to initiate an EEPROM write the following

register write sequence must be executed

Register Attribute Register Address Hex Data

EE Control Reg

EE Security Reg

EE Control Reg

1002

1004

1002

2E

B7

91

Failure to initiate the exact sequence will disable writes

regardless of the value placed in the WriteEEPROM or

EEPROMWriteEn bits of the EEPROM Control Register

EEPROM Control Register

0x1002

This register (in conjunction with the EEPROM Security

Register for writes) controls reading and writing the

EEPROM as well as the EEPROM enable

D7

WriteEEPROM

D6

ReadEEPROM

D5 – D1

Reserved

D0

EEPROMWriteEn

WriteEEPROM When set this tells the EEPROM control-

ler to copy the contents of the PCM16C010 Shadow RAM to

the EEPROM provided the proper write security sequence

listed above has been executed Once the EEPROM write

has completed the EEPROM controller clears this bit

ReadEEPROM When set this tells the EEPROM control-

ler to copy the contents of the EEPROM to the shadow

RAM Once done the EEPROM controller clears this bit

Any data modified in the Shadow RAM that has not first

been written back to the EEPROM will be lost The

EEPROM may be read independent of the value in the

EEPROMWriteEnable bit

EEPROMWriteEn This must be set to allow EEPROM

writes If clear the EEPROM may not be written The default

value at reset is low The EEPROM may be read indepen-

dent of the value of this bit

Note 1 Upon power-up the PCM16C010 EEPROM controller copies the

entire contents of the lower 1 kbytes of the EEPROM into the Shad-

ow RAM independent of writing to the EEPROM Control Register

Note 2 The PCM16C010 EEPROM controller stores data in a 16-bit orga-

nized EEPROM in low high format Although Attribute Memory is

on even byte boundaries only the entire EEPROM’s address space

is used This eliminates waste of EEPROM memory Therefore the

Attribute space used by the Shadow RAM is double the actual size

of the EEPROM For example if a 16-bit EEPROM is pre-pro-

grammed the low byte at word 0 in the EEPROM will be shadowed

at Attribute location 0x0000 and the high byte will be shadowed at

Attribute location 0x0002 The low byte at EEPROM word 1 will be

shadowed to Attribute location 0x0004 etc

EEPROM Security Register

0x1004

This register in conjunction with the EEPROM Control Reg-

ister is used to prevent accidental EEPROM overwriting

When written in the proper sequence as outlined above with

hex data B7 it allows EEPROM write access

5 3 2 PC Card Register

Function Configuration Option Register

0x1020

D7

SRESET

D6

LevIREQ

D5 – D0

Function Configuration Index

11 http www national com

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet PCM16C010.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| PCM16C010 | Configurable PC Card Interface Chip | National Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |