|

|

PDF W210 Data sheet ( Hoja de datos )

| Número de pieza | W210 | |

| Descripción | Spread Spectrum FTG for VIA K7 Chipset | |

| Fabricantes | Cypress Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de W210 (archivo pdf) en la parte inferior de esta página. Total 14 Páginas | ||

|

No Preview Available !

W210

Spread Spectrum FTG for VIA K7 Chipset

Features

• Maximized EMI Suppression using Cypress’s Spread

Spectrum technology

• Single-chip system frequency synthesizer for VIA K7

chipset

• One pair of differential CPU outputs for K7 Processor

• One open-drain CPU output for VIA K7 chipset

• Six copies of PCI output

• One 48-MHz output for USB

• One 24-MHz or 48-MHz output for SIO

• Two buffered reference outputs

• Thirteen SDRAM outputs provide support for 3 DIMMs

• Supports frequencies up to 200 MHz

• I2C™ interface for programming

• Power management control inputs

• Available in 48-pin SSOP

Key Specifications

CPU to CPU Output Skew: ......................................... 175 ps

PCI to PCI Output Skew: ............................................ 500 ps

VDDQ3: .................................................................... 3.3V±5%

Block Diagram

X1 XTAL

X2 OSC

PLL Ref Freq

I/O Pin

Control

VDDQ3

REF0/(CPU_STOP#)

REF1/FS0

PWRDWN#

PLL 1

Stop

Clock

Control

÷2,3,4

SDATA

SCLK

I2C

Logic

PLL2

÷2

SDRAMIN

I2C is a trademark of Philips Corporation.

CPUT_CS

CPUT0

CPUC0

VDDQ3

PCI0/MODE

PCI1/FS1

PCI2

PCI3

PCI4

PCI5

VDDQ3

48MHz/FS2

24_48MHz/FS3

VDDQ3

SDRAM0:12

13

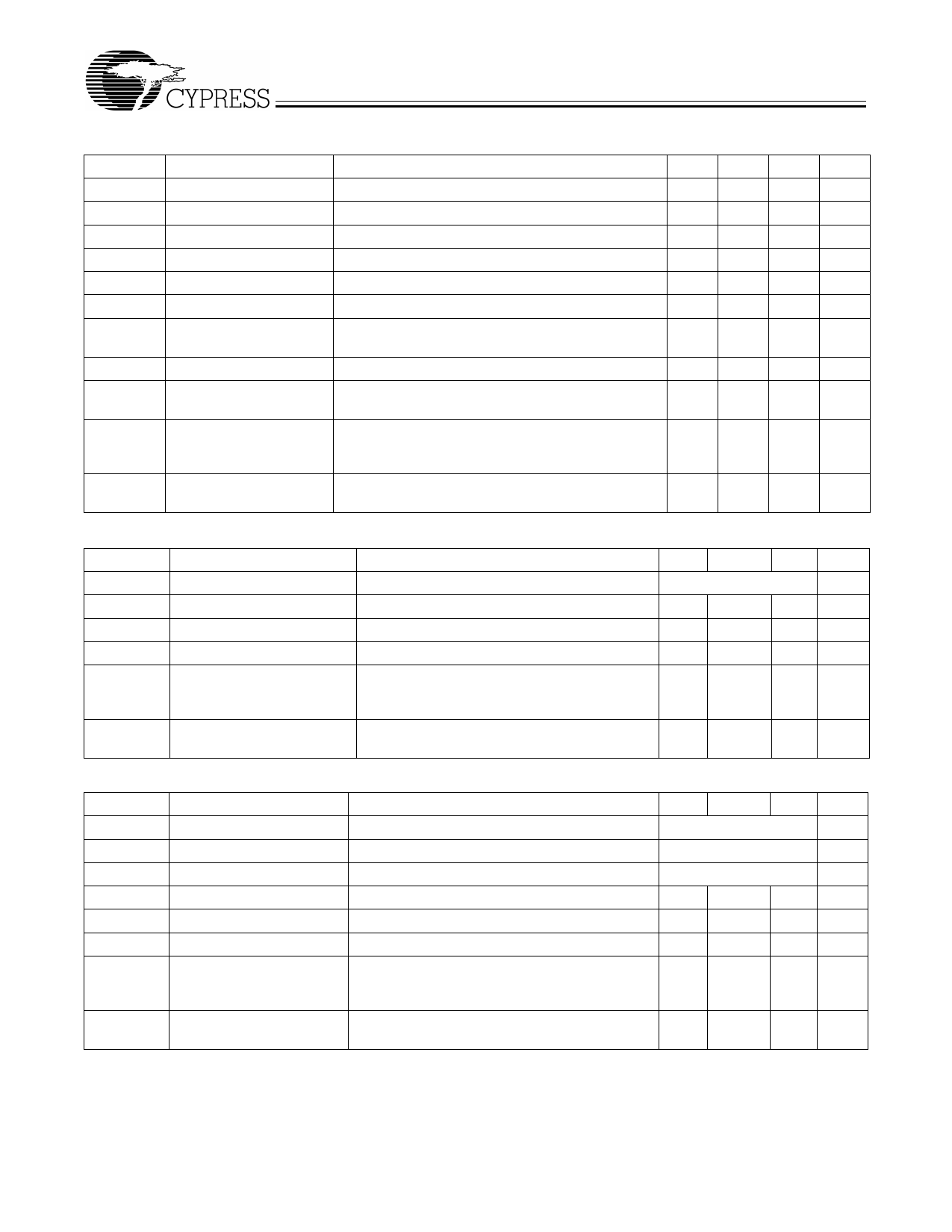

Table 1. Mode Input Table

Mode

0

1

Pin 2

CPU_STOP#

REF0

Table 2. Pin Selectable Frequency

Input Address

FS3 FS2 FS1 FS0

CPU

(MHz)

1111

133.3

1110

75

1101

100.2

1100

66.8

1011

79

1010

110

1001

115

1000

120

0111

133.3

0110

83.3

0101

100.2

0100

66.8

0011

124

0010

129

0001

138

0000

143

PCI0:5

(MHz)

33.3

37.5

33.3

33.4

39.5

36.7

38.3

30

33.3

27.7

33.3

33.4

31.0

32.3

34.5

35.8

Spread

Spectrum

±0.5%

±0.5%

±0.5%

±0.5%

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

Pin Configuration[1]

VDDQ3

REF0/(CPU_STOP#)

GND

X1

X2

VDDQ3

PCI0/MODE

PCI1/FS1*

GND

PCI2

PCI3

PCI4

PCI5

VDDQ3

SDRAMIN

GND

SDRAM11

SDRAM10

VDDQ3

SDRAM9

SDRAM8

GND

{I2C SDATA

SCLK

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

48 REF1/FS0*

47 GND

46 CPUT_CS

45 GND

44 CPUC0

43 CPUT0

42 VDDQ3

41 PWRDWN#*

40 SDRAM12

39 GND

38 SDRAM0

37 SDRAM1

36 VDDQ3

35 SDRAM2

34 SDRAM3

33 GND

32 SDRAM4

31 SDRAM5

30 VDDQ3

29 SDRAM6

28 SDRAM7

27 VDDQ3

26 48MHz/FS2*

25 24_48MHz/FS3^

Note:

1. Internal pull-up resistors should not be relied upon for setting I/O

pins HIGH. Pin function with parentheses determined by MODE pin

resistor strapping. Unlike other I/O pins, input FS3 has an internal

pull-down resistor.

Cypress Semiconductor Corporation • 3901 North First Street • San Jose • CA 95134 • 408-943-2600

April 11, 2000, rev. *C

1 page

W210

Serial Data Interface

The W210 features a two-pin, serial data interface that can be

used to configure internal register settings that control partic-

ular device functions. Upon power-up, the W210 initializes with

default register settings, therefore the use of this serial data

interface is optional. The serial interface is write-only (to the

clock chip) and is the dedicated function of device pins SDATA

and SCLOCK. In motherboard applications, SDATA and

SCLOCK are typically driven by two logic outputs of the

chipset. Clock device register changes are normally made

upon system initialization, if any are required. The interface

can also be used during system operation for power manage-

ment functions. Table 3 summarizes the control functions of

the serial data interface.

Operation

Data is written to the W210 in eleven bytes of eight bits each.

Bytes are written in the order shown in Table 4.

Table 3. Serial Data Interface Control Functions Summary

Control Function

Description

Common Application

Clock Output Disable

Any individual clock output(s) can be disabled. Dis- Unused outputs are disabled to reduce EMI

abled outputs are actively held LOW.

and system power. Examples are clock out-

puts to unused PCI slots.

CPU Clock Frequency

Selection

Provides CPU/PCI frequency selections through

software. Frequency is changed in a smooth and

controlled fashion.

For alternate microprocessors and power

management options. Smooth frequency tran-

sition allows CPU frequency change under

normal system operation.

Spread Spectrum

Enabling

Enables or disables spread spectrum clocking.

For EMI reduction.

Output Three-state

Puts clock output into a high impedance state.

Production PCB testing.

(Reserved)

Reserved function for future device revision or pro- No user application. Register bit must be writ-

duction device testing.

ten as 0.

Table 4. Byte Writing Sequence

Byte Sequence Byte Name

1 Slave Address

2 Command

Code

3 Byte Count

4 Data Byte 0

5 Data Byte 1

6 Data Byte 2

7 Data Byte 3

8 Data Byte 4

9 Data Byte 5

10 Data Byte 6

11 Data Byte 7

Bit Sequence

11010010

Don’t Care

Don’t Care

Refer to Table 5

Byte Description

Commands the W210 to accept the bits in Data Bytes 0–6 for internal

register configuration. Since other devices may exist on the same com-

mon serial data bus, it is necessary to have a specific slave address for

each potential receiver. The slave receiver address for the W210 is

11010010. Register setting will not be made if the Slave Address is not

correct (or is for an alternate slave receiver).

Unused by the W210, therefore bit values are ignored (“Don’t Care”).

This byte must be included in the data write sequence to maintain proper

byte allocation. The Command Code Byte is part of the standard serial

communication protocol and may be used when writing to another ad-

dressed slave receiver on the serial data bus.

Unused by the W210, therefore bit values are ignored (“Don’t Care”).

This byte must be included in the data write sequence to maintain proper

byte allocation. The Byte Count Byte is part of the standard serial com-

munication protocol and may be used when writing to another addressed

slave receiver on the serial data bus.

The data bits in Data Bytes 0–7 set internal W210 registers that control

device operation. The data bits are only accepted when the Address

Byte bit sequence is 11010010, as noted above. For description of bit

control functions, refer to Table 5, Data Byte Serial Configuration Map.

5

5 Page

W210

PCI Clock Outputs, PCI0:5 (Lump Capacitance Test Load = 30 pF

Parameter

Description

Test Condition/Comments

tP Period

Measured on rising edge at 1.5V

tH High Time

Duration of clock cycle above 2.4V

tL Low Time

Duration of clock cycle below 0.4V

tR Output Rise Edge Rate Measured from 0.4V to 2.4V

tF Output Fall Edge Rate Measured from 2.4V to 0.4V

tD Duty Cycle

Measured on rising and falling edge at 1.5V

tJC

Jitter, Cycle-to-Cycle

Measured on rising edge at 1.5V. Maximum

difference of cycle time between two adjacent cycles.

tSK Output Skew

Measured on rising edge at 1.5V

tO CPU to PCI Clock Skew Covers all CPU/PCI outputs. Measured on rising

edge at 1.5V. CPU leads PCI output.

fST Frequency Stabilization Assumes full supply voltage reached within 1 ms

from Power-up (cold

from power-up. Short cycles exist prior to frequency

start)

stabilization.

Zo AC Output Impedance Average value during switching transition. Used for

determining series termination value.

Min.

30

12

12

1

1

45

1.5

Typ.

30

Max.

4

4

55

250

500

4

3

Unit

ns

ns

ns

V/ns

V/ns

%

ps

ps

ns

ms

Ω

REF0:1 Clock Outputs (Lump Capacitance Test Load = 20 pF)

Parameter

Description

Test Condition/Comments

f

Frequency, Actual

Frequency generated by crystal oscillator

tR

Output Rise Edge Rate

Measured from 0.4V to 2.4V

tF

Output Fall Edge Rate

Measured from 2.4V to 0.4V

tD Duty Cycle

Measured on rising and falling edge at 1.5V

fST Frequency Stabilization from Assumes full supply voltage reached within

Power-up (cold start)

1 ms from power-up. Short cycles exist prior to

frequency stabilization.

Zo

AC Output Impedance

Average value during switching transition. Used

for determining series termination value.

Min.

0.5

0.5

45

Typ.

14.318

40

Max.

2

2

55

3

Unit

MHz

V/ns

V/ns

%

ms

Ω

48-MHz Clock Output (Lump Capacitance Test Load = 20 pF)

Parameter

Description

Test Condition/Comments

f

Frequency, Actual

Determined by PLL divider ratio (see m/n below)

fD

Deviation from 48 MHz

(48.008 – 48)/48

m/n PLL Ratio

(14.31818 MHz x 57/17 = 48.008 MHz)

tR Output Rise Edge Rate Measured from 0.4V to 2.4V

tF

Output Fall Edge Rate

Measured from 2.4V to 0.4V

tD Duty Cycle

Measured on rising and falling edge at 1.5V

fST Frequency Stabilization Assumes full supply voltage reached within 1 ms

from Power-up (cold start) from power-up. Short cycles exist prior to fre-

quency stabilization.

Zo

AC Output Impedance

Average value during switching transition. Used

for determining series termination value.

Min.

0.5

0.5

45

Typ.

48.008

+167

57/17

40

Max.

2

2

55

3

Unit

MHz

ppm

V/ns

V/ns

%

ms

Ω

11

11 Page | ||

| Páginas | Total 14 Páginas | |

| PDF Descargar | [ Datasheet W210.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| W210 | Spread Spectrum FTG for VIA K7 Chipset | Cypress Semiconductor |

| W210TS | HIGH VOLTAGE PHOTO MOS RELAY | ETC |

| W2115MC500 | Rectifier Diode | IXYS |

| W2115MC520 | Rectifier Diode | IXYS |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |