|

|

PDF EM73A89B Data sheet ( Hoja de datos )

| Número de pieza | EM73A89B | |

| Descripción | 4-BIT MICRO-CONTROLLER FOR LCD PRODUCT | |

| Fabricantes | ELAN Microelectronics Corp | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de EM73A89B (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

GENERAL DESCRIPTION

EM73A89B

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

Preliminary

EM73A89B is an advanced single chip CMOS 4-bit micro-controller. It contains 16K-byte ROM, 1012-nibble

RAM, 4-bit ALU, 13-level subroutine nesting, 22-stage time base, two 12-bit timer/counters for the kernel

function, and one high speed conter. EM73A89B also equipped with 6 interrupt sources, 3~7 I/O ports (including

1 input port and 2~7 bidirection ports), LCD display (64x16 or 64x32), built-in watch-dog-timer and speech

synthesizer.

It's low power consumption and high speed feature are further strengten with DUAL, SLOW, IDLE and STOP

operation mode for optimized power saving.

FEATURES

Operation voltage

: 2.2V to 3.6V.

Clock source

: Dual clock system. Low-frequency oscillator is 32KHz. Crystal oscillator or RC

oscillator by mask option and high-frequency oscillator is a built-in internal

oscillator.

Instruction set

: 107 powerful instructions.

Instruction cycle time : 0.85µs for 9.2M or 1.7µs for 4.6M Hz selected by mask option(high speed clock).

122µs for 32768 Hz (low speed clock, frequency double).

ROM capacity

: 16K x 8 bits.

RAM capacity

: 1012 x 4 bits.

Input port

: 1 port (P0.0-P0.3), IDLE/STOP releasing function is available by mask option.

(each input pin has a pull-up and pull-down resistor available by mask option).

Bidirection port

: 2~7 ports (P1, P2, P4, P5, P6, P7, P8). IDLE/STOP release function for P8(0..

3) is available by mask option. P1, P2, P5, P6, P7 are shared with LCD pins.

Built-in watch-dog-timer counter : It is available by mask option.

12-bit timer/counter

: Two 12-bit timer/counters are programmable for timer, event counter and pulse

width measurement mode.

Built-in time base counter : 22 stages.

Subroutine nesting

: Up to 13 levels.

Interrupt

: External interrupt . . . . . . 2 input interrupt sources.

Internal interrupt . . . . . . 2 timer overflow interrupts, 1 time base interrupt.

1 speech/HTC interrupt.

High speed counter

: The high speed counter includes one 8-bit high speed counter and a resistor to

frequency oscillator. It has resistor to frequrncy oscillation mode, melody mode

and auto load timer mode.

LCD driver

: 64x32 or 64x16 dots, 1/32 or 1/16 duty, 1/5 bias by mask option.

Speech synthesizer

: 992K speech data ROM (use as 992K nibbles data ROM).

PWM or current D/A : Output selection by mask option.

Power saving function : SLOW, IDLE, STOP operation modes.

Package type

: Chip form 126 pins.

* This specification are subject to be changed without notice.

8.16.2001 1

1 page

EM73A89B

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

PreliminaryUser's program and fixed data are stored in the program ROM. User's program is executed using the PC value

to fetch an instruction code.

The 16Kx8 bits program ROM can be divided into 4 banks. There are 4Kx8 bits per bank.

The program ROM bank is selected by P3(1..0). The program counter is a 13-bit binary counter. The PC and

P3 are initialized to "0" during reset.

When P3(1..0)=00B or 11B, the bank0 and bank1 of program ROM will be selected. P3(1..0)=01B, the bank0

and bank2 will be selected. P3(1..0)=10B, the bank0 and bank3 will be selected.

P3=xx00B

Address

P3=xx11B

P3=xx01B

P3=xx10B

0000h

:

:

Bank0

Bank0

Bank0

0FFFh

1000h

:

:

Bank1

Bank2

Bank3

1FFFh

PROGRAM EXAMPLE:

BANK 0

START: :

:

:

LDIA #00H

; set program ROM to bank1

OUTA P3

B XA1

:

XA :

:

:

LDIA #01H

; set program ROM to bank2

OUTA P3

B XB1

:

XB : :

:

LDIA #02H

; set program ROM to bank3

OUTA P3

B XC1

:

XC : :

:

B XD

XD :

:

:

:

;--------------------------------------------------------------------------------------

BANK 1

XA1 :

:

:

B XA

:

XA2 :

:

* This specification are subject to be changed without notice.

8.16.2001 5

5 Page

EM73A89B

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

Preliminary

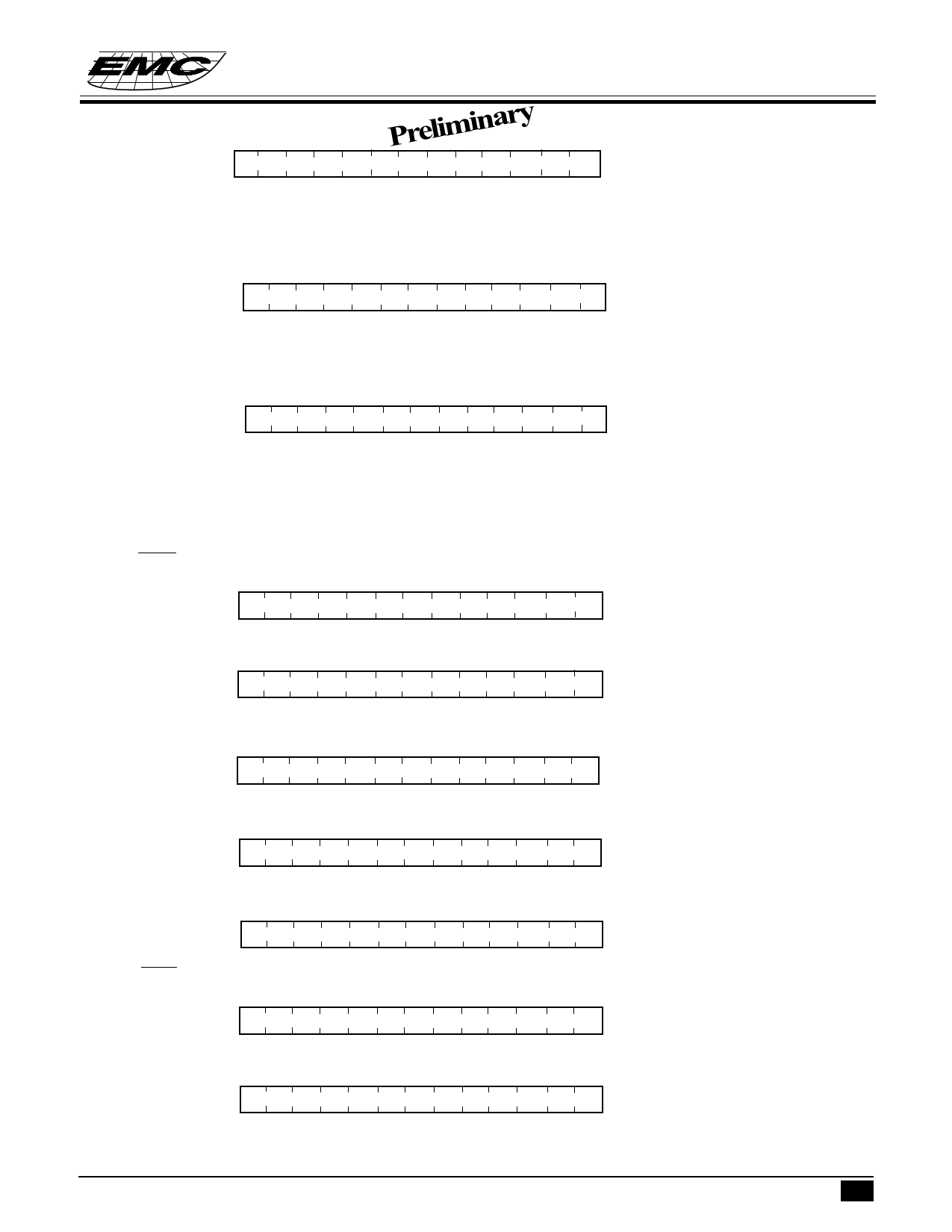

PC 0 0 a a a a a a a a a a a

RET

Object code: 0100 1111

Condition: PC ← STACK[SP]; SP + 1

PC The return address stored in stack

RT I

Object code: 0100 1101

Condition : FLAG. PC ← STACK[SP]; EI ← 1; SP + 1

PC The return address stored in stack

(3) Interrupt acceptance operation:

When an interrupt is accepted, the original PC is pushed into stack and interrupt vector will be loaded into

PC. The interrupt vectors are as follows :

INT0 (External interrupt from P8.2)

PC 0 0 0 0 0 0 0 0 0 0 0 1 0

SPI (speech end interrupt)

PC 0 0 0 0 0 0 0 0 0 0 1 0 0

TRGA (Timer A overflow interrupt)

PC 0 0 0 0 0 0 0 0 0 0 1 1 0

TRGB (Time B overflow interrupt)

PC 0 0 0 0 0 0 0 0 0 1 0 0 0

TBI (Time base interrupt)

PC 0 0 0 0 0 0 0 0 0 1 0 1 0

INT1 (External interrupt from P8.0)

PC 0 0 0 0 0 0 0 0 0 1 1 0 0

(4) Reset operation:

PC 0 0 0 0 0 0 0 0 0 0 0 0 0

* This specification are subject to be changed without notice.

8.16.2001 11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet EM73A89B.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| EM73A89B | 4-BIT MICRO-CONTROLLER FOR LCD PRODUCT | ELAN Microelectronics Corp |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |