|

|

PDF DM74AS646 Data sheet ( Hoja de datos )

| Número de pieza | DM74AS646 | |

| Descripción | Octal Bus Transceiver and Register | |

| Fabricantes | Fairchild Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de DM74AS646 (archivo pdf) en la parte inferior de esta página. Total 8 Páginas | ||

|

No Preview Available !

October 1986

Revised March 2000

DM74AS646 • DM74AS648

Octal Bus Transceiver and Register

General Description

This device incorporates an octal bus transceiver and an

octal D-type register configured to enable multiplexed

transmission of data from bus to bus or internal register to

bus.

This bus transceiver features totem-pole 3-STATE outputs

designed specifically for driving highly-capacitive or rela-

tively low-impedance loads. The high-impedance third

state and increased high-logic-level drive provide this

device with the capability of being connected directly to and

driving the bus lines in a bus-organized system without

need for interface or pull-up components. It is particularly

attractive for implementing buffer registers, I/O ports, bidi-

rectional bus drivers, and working registers.

The registers in the DM74AS646, DM74AS648 are edge-

triggered D-type flip-flops. On the positive transition of the

clock (CAB or CBA), the input bus data is stored.

The SAB and SBA control pins are provided to select

whether real-time data or stored data is transferred. A LOW

input level selects real-time data, and a HIGH level selects

stored data. The select controls have a “make before

break” configuration to eliminate a glitch which would nor-

mally occur in a typical multiplexer during the transition

between stored and real-time data.

The enable G and direction control pins provide four modes

of operation; real-time data transfer from bus A to B, real-

time data transfer from bus B to A, real-time bus A and/or B

data transfer to internal storage, or internal store data

transfer to bus A or B.

When the enable G pin is LOW, the direction pin selects

which bus receives data. When the enable G pin is HIGH,

both buses become disabled yet their input function is still

enabled.

Features

s Switching specifications at 50 pF

s Switching specifications guaranteed over full tempera-

ture and VCC range

s Advanced oxide-isolated, ion-implanted Schottky TTL

process

s Functionally and pin-for-pin compatible with LS TTL

counterpart

s 3-STATE buffer-type outputs drive bus lines directly

Ordering Code:

Order Number Package Number

Package Description

DM74AS646WM

M24B

24-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300 Wide

DM74AS646NT

N24C

24-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-100, 0.300 Wide

DM74AS648WM

M24B

24-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300 Wide

DM74AS648NT

N24C

24-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-100, 0.300 Wide

Devices also available in Tape and Reel. Specify by appending the suffix letter “X” to the ordering code.

© 2000 Fairchild Semiconductor Corporation DS006324

www.fairchildsemi.com

1 page

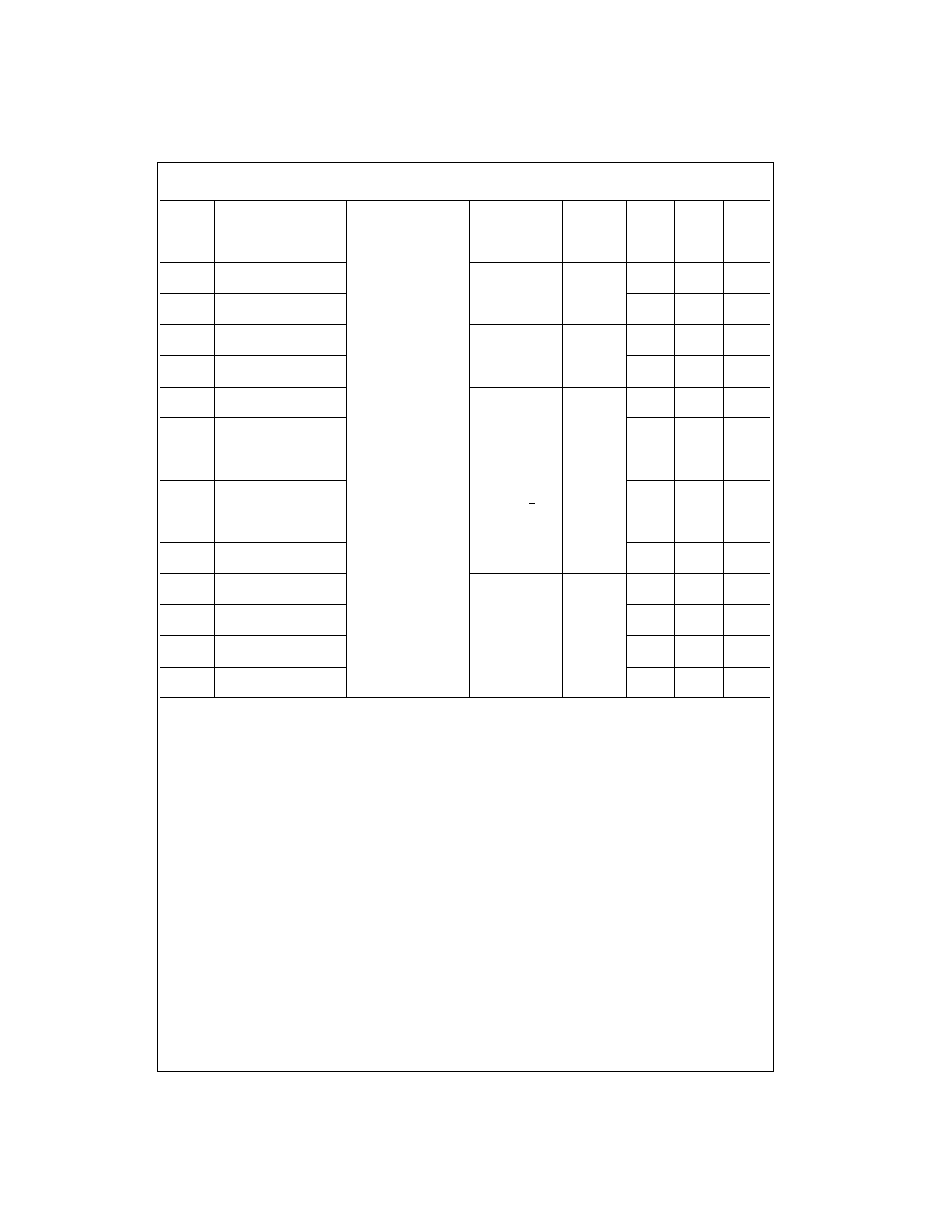

DM74AS646 Switching Characteristics

Symbol

Parameter

Conditions

From

(Input)

To

(Output)

Min

fMAX

tPLH

tPHL

Maximum Clock

Frequency

Propagation Delay Time

LOW-to-HIGH Level Output

Propagation Delay Time

HIGH-to-LOW Level Output

VCC = 4.5V to 5.5V,

R1 = R2 = 500Ω

CL = 50 pF

CBA or CAB

A or B

90

2

2

tPLH Propagation Delay Time

LOW-to-HIGH Level Output

tPHL Propagation Delay Time

HIGH-to-LOW Level Output

A or B

B or A

2

1

tPLH Propagation Delay Time

LOW-to-HIGH Level Output

tPHL Propagation Delay Time

HIGH-to-LOW Level Output

SBA or SAB

(Note 6)

A or B

2

2

tPZH Output Enable Time

to HIGH Level Output

2

tPZL Output Enable Time

to LOW Level Output

tPHZ Output Disable Time

from HIGH Level Output

Enable G

A or B

3

2

tPLZ Output Disable Time

from LOW Level Output

2

tPZH Output Enable Time

to HIGH Level Output

3

tPZL Output Enable Time

to LOW Level Output

tPHZ Output Disable Time

from HIGH Level Output

3

DIR A or B

2

tPLZ Output Disable Time

from LOW Level Output

2

Note 6: These parameters are measured with the internal output state of the storage register opposite to that of the bus input.

Max

8.5

9

9

7

11

9

9

14

9

9

16

18

10

10

Units

MHz

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

5 www.fairchildsemi.com

5 Page | ||

| Páginas | Total 8 Páginas | |

| PDF Descargar | [ Datasheet DM74AS646.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| DM74AS640 | 3-STATE Octal Bus Transceiver | Fairchild Semiconductor |

| DM74AS640N | 3-STATE Octal Bus Transceiver | Fairchild Semiconductor |

| DM74AS640WM | 3-STATE Octal Bus Transceiver | Fairchild Semiconductor |

| DM74AS646 | Octal Bus Transceiver and Register | Fairchild Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |