|

|

PDF DS2180A Data sheet ( Hoja de datos )

| Número de pieza | DS2180A | |

| Descripción | T1 Transceiver | |

| Fabricantes | Dallas Semiconducotr | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de DS2180A (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

www.dalsemi.com

FEATURES

Single chip DS1 rate transceiver

Supports common framing standards

– 12 frames/superframe “193S”

– 24 frames/superframe “193E”

Three zero suppression modes

– B7 stuffing

– B8ZS

– Transparent

Simple serial interface used for config-

uration, control and status monitoring in

“processor” mode

=“Hardware” mode requires no host

processor; intended for stand-alone app-

lications

Selectable 0, 2, 4, 16 state robbed bit

signaling modes

Allows mix of “clear” and “non-clear” DS0

channels on same DS1 link

Alarm generation and detection

Receive error detection and counting for

transmission performance monitoring

5V supply, low-power CMOS technology

Surface-mount package available, designated

DS2180AQ

Industrial temperature range of -40°C to

+85°C available, designated DS2180AN or

DS2180AQN

Compatible to DS2186 Transmit Line

Interface, DS2187 Receive Line Interface,

DS2188 Jitter Attenuator, DS2175 T1/CEPT

Elastic Store, DS2290 T1 Isolation Stik, and

DS2291 T1 Long Loop Stik

DS2180A

T1 Transceiver

PIN ASSIGNMENT

TMSYNC

TFSYNC

TCLK

TCHCLK

TSER

TMO

TSIGSEL

TSIGFR

TABCD

TLINK

TLCLK

TPOS

TNEG

INT

SDI

SDO

CS

SCLK

SPS

VSS

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

40 VDD

39 RLOS

38 RFER

37 RBV

36 RCL

35 RNEG

34 RPOS

33 RST

32 TEST

31 RSIGSEL

30 RSIGFR

29 RABCD

28 RMSYNC

27 RFSYNC

26 RSER

25 RCHCLK

24 RCLK

23 RLCLK

22 RLINK

21 RYEL

40-Pin DIP (600-mil)

TSER

TMO

TSIGSEL

TSIGFR

TABCD

TLINK

TLCLK

TPOS

TNEG

INT

SDI

7

8

9

10

11

12

13

14

15

16

17

39 RNEG

38 RPOS

37 RST

36 TEST

35 RSIGSEL

34 RSIGFR

33 RABCD

32 RMSYNC

31 RFSYNC

30 RSER

29 RCHCLK

1 of 35

112099

1 page

DS2180A

REGISTER SUMMARY Table 5

REGISTER

RSR

RIMR

ADDRESS

0000

0001

T/R1

R2

R

DESCRIPTION/FUNCTION

Receive Status Register. Reports all receive alarm conditions.

Receive Interrupt Mask Register. Allows masking of individual alarm-

generated interrupts.

BVCR

0010

R Bipolar Violation Count Register. 8-bit presettable counter which records

individual bipolar violations.

ECR

CCR3

RCR3

TCR3

0011

0100

0101

0110

R Error Count Register. Two independent 4-bit counters which record OOF

occurrences and individual frame bit or CRC errors.

T/R Common Control Register. Selects device operating characteristics common

to receive and transmit sides.

R Receive Control Register. Programs device operating characteristics

unique to the receive side.

T Transmit Control Register. Selects additional transmit side modes.

TIR1

TIR2

0111

1000

T Transmit Idle Registers. Designate which outgoing channels are to be

T substituted with idle code.

TIR3

1001

T

TTR1

TTR2

1010

1011

T Transmit Transparent Registers. Designate which outgoing channels are to be

T treated transparently. (No robbed bit signaling or bit 7 zero insertion.)

TTR3

1100

T

RMR1

RMR2

1101

1110

R Receive Mark Registers. Designate which incoming channels are to be replaced

R with idle or digital milliwatt codes (under control of RCR).

RMR3

1111

R

NOTES:

1. Transmit or receive side register.

2. RSR is a read only register; all other registers are read/write.

3. Reserved bit locations in the control registers should be programmed to 0 to maintain compatibility

with future transceiver products.

SERIAL PORT INTERFACE

Pins 14 through 18 of the DS2180A serve as a microprocessor/microcontroller-compatible serial port.

Sixteen onboard registers allow the user to update operational characteristics and monitor device status

via host controller, minimizing hardware interfaces. Port read/write timing is unrelated to the system

transmit and receive timing, allowing asynchronous reads and/or writes by the host.

ADDRESS/COMMAND

Reading or writing the control, configuration or status registers requires writing one address command

byte prior to transferring register data. The first bit written (LSB) of the address/command word specifies

register read or write. The following 4-bit nibble identifies register address. The next two bits are

reserved and must be set to 0 for proper operation. The last bit of the address/ command word enables

burst mode when set; the burst mode causes all registers to be consecutively written or read. Data is

written to and read from the transceiver LSB first.

CHIP SELECT AND CLOCK CONTROL

All data transfers are initiated by driving the CS input low. Input data is latched on the rising edge of

SCLK and must be valid during the previous low period of SCLK to prevent momentary corruption of

register data during writes. Data is output on the falling edge of SCLK and held on the next falling edge.

5 of 35

5 Page

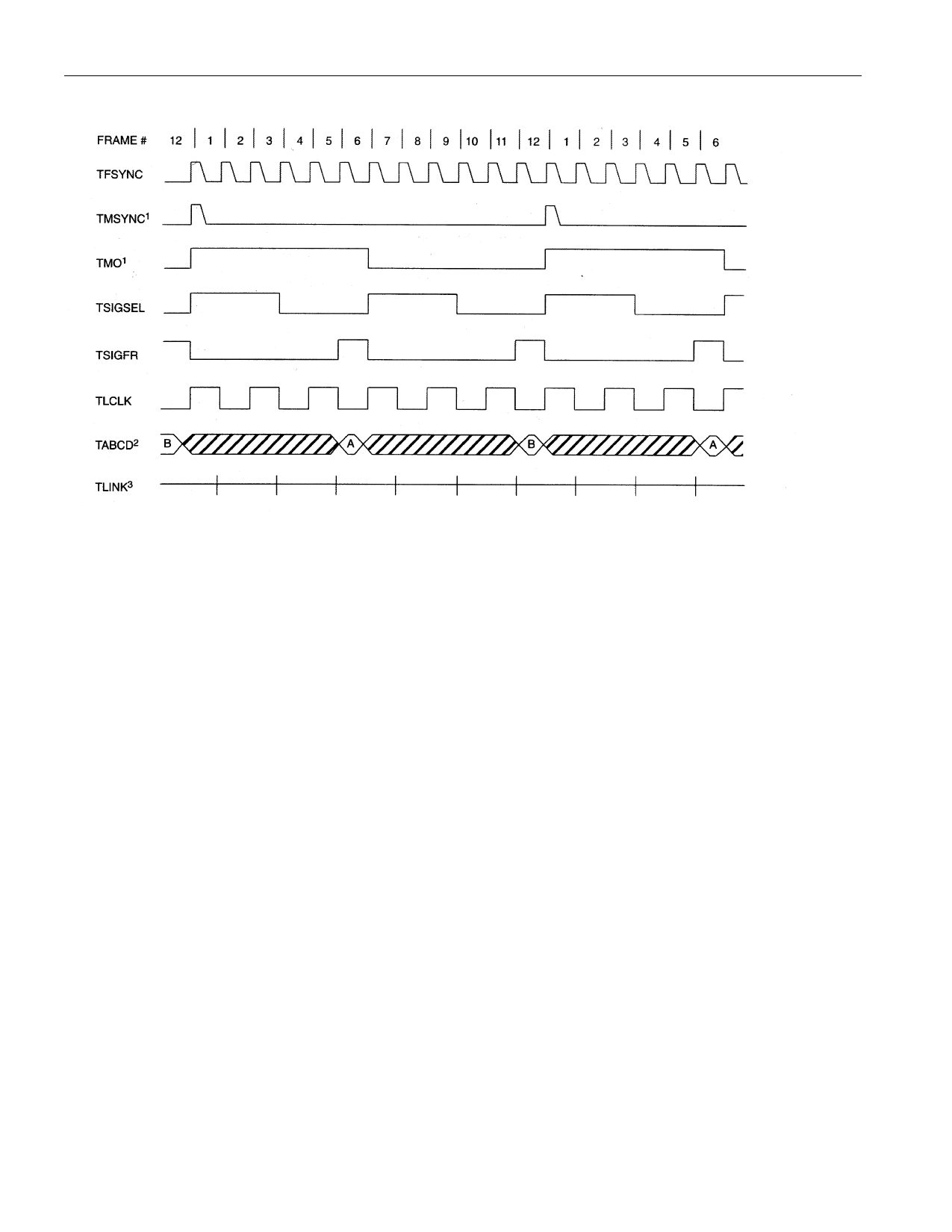

193S TRANSMIT MULTIFRAME TIMING Figure 9

DS2180A

NOTES:

1. Transmit frame and multiframe timing may be established in one of four ways:

a. With TFSYNC tied low, TMSYNC may be pulsed high once every multiframe period to establish

multiframe boundaries, allowing internal counters to determine frame timing.

b. TFSYNC may be pulsed every 125 microseconds; pulsing TMSYNC once establishes multiframe

boundaries.

c. TMSYNC and TFSYNC may be continuously pulsed to establish and reinforce frame and

superframe timing.

d. If TMSYNC is tied low and TFSYNC is pulsed at frame boundaries, the transmitter will establish

an arbitrary multiframe boundary as indicated by TMO.

2. Channels in which robbed bit signaling is enabled will sample TABCD during the LSB bit time in

frames indicated.

3. When external S-bit insertion is enabled, TLINK will be sampled during the F-bit time of even frames

and inserted into the outgoing data stream.

11 of 35

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet DS2180A.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| DS2180A | T1 Transceiver | Dallas Semiconducotr |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |