|

|

PDF AN8538 Data sheet ( Hoja de datos )

| Número de pieza | AN8538 | |

| Descripción | Single PLL IC for cellular phone | |

| Fabricantes | Panasonic Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de AN8538 (archivo pdf) en la parte inferior de esta página. Total 5 Páginas | ||

|

No Preview Available !

ICs for Mobile Communication

AN8538SH

Single PLL IC for cellular phone

s Overview

The AN8538SH is a single PLL IC with a fixed

frequency dividing ratio for IF local oscillation of

a cellular phone. You can generate a local signal of

260.76 MHz by using a reference signal of 19.68

MHz or 19.8 MHz.

s Features

• Two reference frequencies of 19.68 MHz and 19.8

MHz are available. (Select by SELECT pin.)

• Power saving operation (VCC = 2.7 V, 0.9 mA typ.)

• Power saving function (10 µA max.)

• Two systems of charge pump output (one of them

can be switched to on/off with SW pin.)

• Lock detection function

• SSONF-10D small package

s Applications

• IF local oscillation for cellular phone terminal

(CDMA for North America)

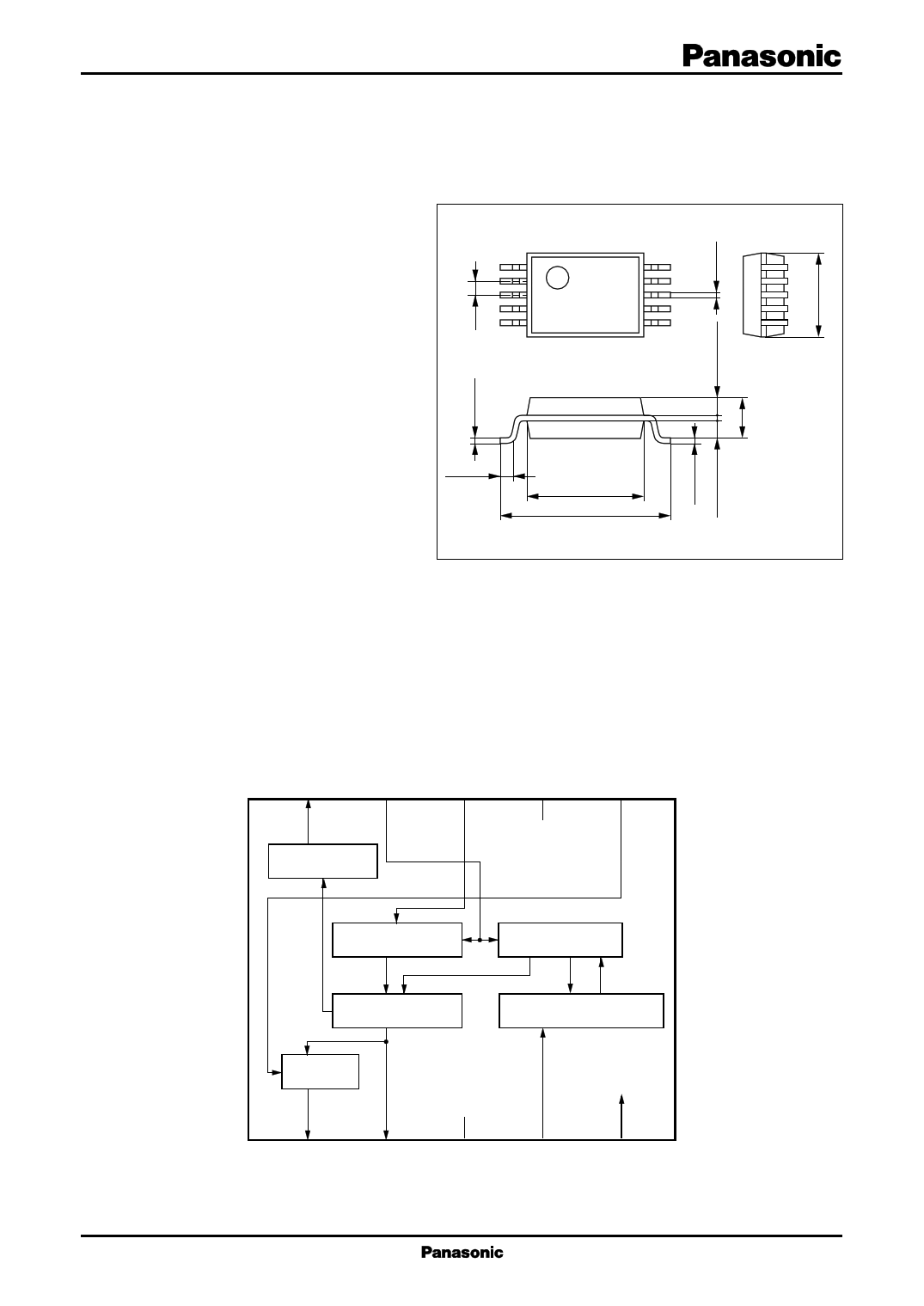

1

5

0.5±0.2

10

6

4.3±0.30

6.3±0.30

SSOP010-P-0225

Unit: mm

s Block Diagram

Lock detection

14-bit R counter

15-bit N counter

Phase comparator

Selector

1/16, 1/17 prescaler

1

1 page

ICs for Mobile Communication

s Application Notes (continued)

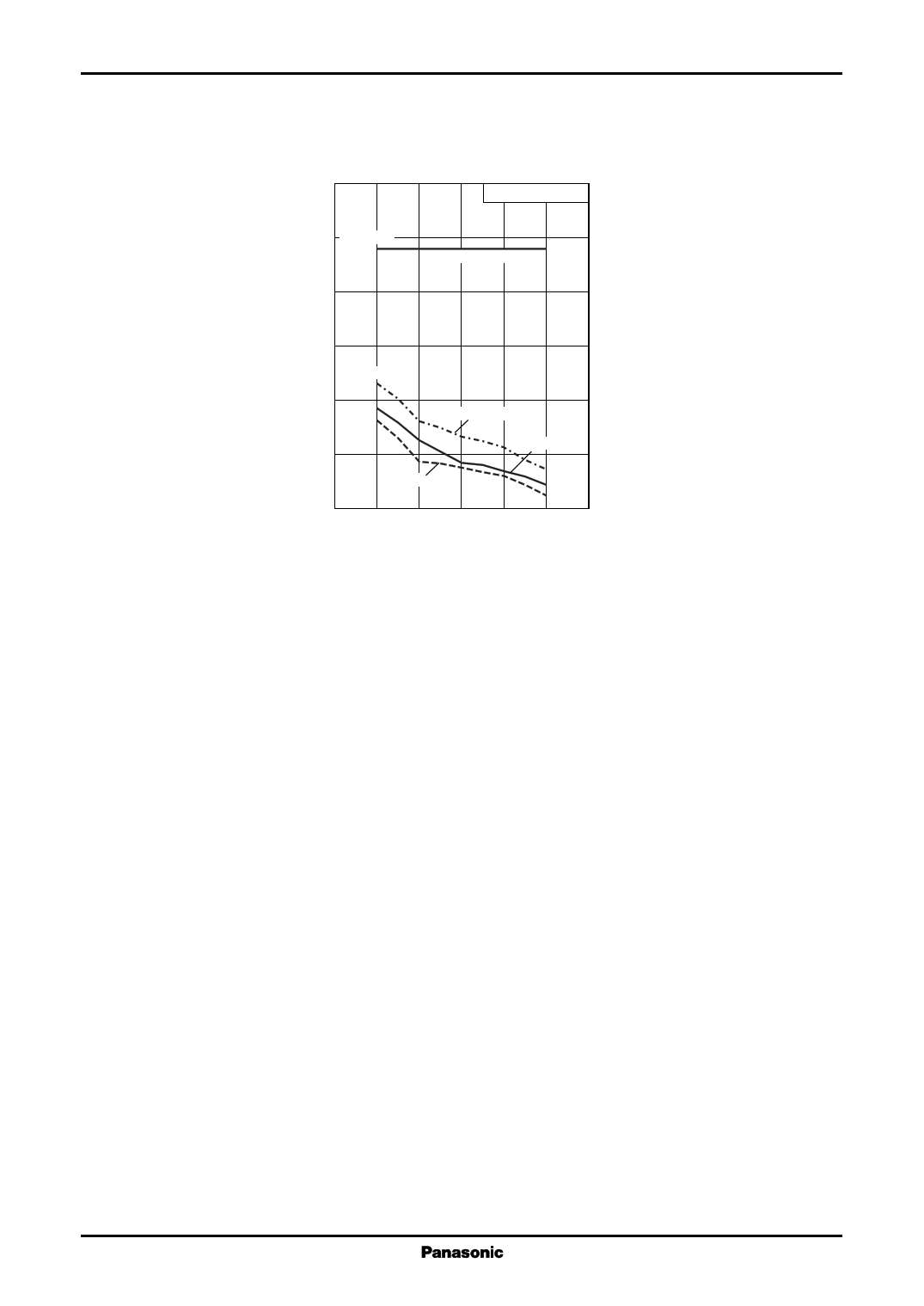

1. Input level characteristics (continued)

2) REF input level characteristics

20 Upper limit

10

VCC = 2.55 V to 3.3V

Ta = −30°C, 25°C, 85°C

AN8538SH

0

Lower limit

−10

Ta = −30°C

Ta = 25°C

−20

Ta = 85°C

−30

0

5 10 15 20 25

Input frequency (MHz)

30

2. Characteristics specification

1) IF select specification

SELECT pin control enables you to switch IF as below:

SELECT = low → fOUT = 260.76 MHz, fR = 60 kHz (P = 16, N = 271, A = 10, R = 328)

SELECT = high → fOUT = 260.76 MHz, fR = 60 kHz (P = 16, N = 271, A = 10, R = 330)

2) Unlock detection and LD output specification

LD output is high in a lock mode and low in an unlock mode. Lock signal is outputted in a power save mode.

SELECT = high : Detection time is 16 µs. About detection accuracy, when a dividing output shifts

by ±(51 × 3) ns for fREF = 60 kHz, it generates an unlock output.

SELECT = low : Detection time is 16 µs. About detection accuracy, when a dividing output shifts

by ±(51 × 3) ns for fREF = 60 kHz, it generates an unlock output.

3) Power save control specification

When power save control pin (PS) is high, it is set to an operating mode. When it is low, it is set to power save mode.

4) Analog SW control specification

CPSUB is controlled by SW pin.

SW = low : CPSUB open

SW = high: CPSUB operation

5) Other specification

Set CMOS input pins, such as PS pin, SW pin, SELECT pin, etc., normally to VCC or GND.

5

5 Page | ||

| Páginas | Total 5 Páginas | |

| PDF Descargar | [ Datasheet AN8538.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AN8538 | Single PLL IC for cellular phone | Panasonic Semiconductor |

| AN8538SH | Single PLL IC for cellular phone | Panasonic Semiconductor |

| AN8539SH | 300 MHz-band single PLL IC | Panasonic Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |