|

|

PDF ADC12441CMJ Data sheet ( Hoja de datos )

| Número de pieza | ADC12441CMJ | |

| Descripción | Dynamically-Tested Self-Calibrating 12-Bit Plus Sign A/D Converter with Sample-and-Hold | |

| Fabricantes | National Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de ADC12441CMJ (archivo pdf) en la parte inferior de esta página. Total 14 Páginas | ||

|

No Preview Available !

November 1994

ADC12441 Dynamically-Tested Self-Calibrating 12-Bit

Plus Sign A D Converter with Sample-and-Hold

General Description

The ADC12441 is a CMOS 12-bit plus sign successive ap-

proximation analog-to-digital converter whose dynamic

specifications (S N THD etc ) are tested and guaranteed

On request the ADC12441 goes through a self-calibration

cycle that adjusts positive linearity and full-scale errors to

less than g LSB each and zero error to less than

g1 LSB The ADC12441 also has the ability to go through

an Auto-Zero cycle that corrects the zero error during every

conversion

The analog input to the ADC12441 is tracked and held by

the internal circuitry and therefore does not require an ex-

ternal sample-and-hold A unipolar analog input voltage

range (0V to a5V) or a bipolar range (b5V to a5V) can be

accommodated with g5V supplies

The 13-bit word on the outputs of the ADC12441 gives a 2’s

complement representation of negative numbers The digi-

tal inputs and outputs are compatible with TTL or CMOS

logic levels

Features

Y Self-calibration provides excellent temperature stability

Y Internal sample-and-hold

Y Bipolar input range with single a5V reference

Applications

Y Digital signal processing

Y Telecommunications

Y Audio

Y High resolution process control

Y Instrumentation

Key Specifications

Y Resolution

Y Conversion Time

Y Bipolar Signal Noise

Y Total Harmonic Distortion

Y Aperture Time

Y Aperture Jitter

Y Zero Error

Y Positive Full Scale Error

Y Power Consumption g5V

Y Sampling rate

12 bits plus sign

13 8 ms (max)

76 5 dB (min)

b75 dB (max)

100 ns

100 psrms

g1 LSB (max)

g1 LSB (max)

70 mW (max)

55 kHz (max)

TRI-STATE is a registered trademark of National Semiconductor Corporation

Simplified Block Diagram

Connection Diagram

Dual-In-Line Package

C1995 National Semiconductor Corporation TL H 11017

Top View

TL H 11017 – 2

Order Number

ADC12441CMJ ADC12441CMJ 883

or ADC12441CIJ

See NS Package Number J28A

TL H 11017 – 1

RRD-B30M115 Printed in U S A

1 page

AC Electrical Characteristics (Continued)

Note 4 The power dissipation of this device under normal operation should never exceed 169 mW (Quiescent Power Dissipation a TTL Loads on the digital

outputs) Caution should be taken not to exceed absolute maximum power rating when the device is operating in a severe fault condition (ex when any inputs or

outputs exceed the power supply) The maximum power dissipation must be derated at elevated temperatures and is dictated by TJmax (maximum junction

temperature) iJA (package junction to ambient thermal resistance) and TA (ambient temperature) The maximum allowable power dissipation at any temperature

is PDmax e (TJmax b TA) iJA or the number given in the Absolute Maximum Ratings whichever is lower For this device TJmax e 125 C and the typical thermal

resistance (iJA) of the ADC12441 with CMJ and CIJ suffixes when board mounted is 47 C W

Note 5 Human body model 100 pF discharged through a 1 5 kX resistor

Note 6 Two on-chip diodes are tied to the analog input as shown below Errors in the A D conversion can occur if these diodes are forward biased more than

50 mV

TL H 11017 – 3

This means that if AVCC and DVCC are minimum (4 75 VDC) and Vb is maximum (b4 75 VDC) full-scale must be s 4 8 VDC

Note 7 A diode exists between AVCC and DVCC as shown below

TL H 11017 – 4

To guarantee accuracy it is required that the AVCC and DVCC be connected together to a power supply with separate bypass filters at each VCC pin

Note 8 Accuracy is guaranteed at fCLK e 2 0 MHz At higher and lower clock frequencies accuracy may degrade See curves in the Typical Performance

Characteristics section

Note 9 Typicals are at TJ e 25 C and represent most likely parametric norm

Note 10 Limits are guaranteed to National’s AOQL (Average Outgoing Quality Level)

Note 11 Positive linearity error is defined as the deviation of the analog value expressed in LSBs from the straight line that passes through positive full scale and

zero For negative linearity error the straight line passes through negative full scale and zero (See Figures 1b and 1c )

Note 12 The ADC12441’s self-calibration technique ensures linearity full scale and offset errors as specified but noise inherent in the self-calibration process will

result in a repeatability uncertainty of g0 20 LSB

Note 13 If TA changes then an Auto-Zero or Auto-Cal cycle will have to be re-started (see the Typical Performance Characteristic curves)

Note 14 After an Auto-Zero or Auto-Cal cycle at the specified power supply extremes

Note 15 If the clock is asynchronous to the falling edge of WR an uncertainty of one clock period will exist in the interval of tA therefore making the minimum

tA e 6 clock periods and the maximum tA e 7 clock periods If the falling edge of the clock is synchronous to the rising edge of WR then tA will be exactly 6 5 clock

periods

Note 16 The CAL line must be high before a conversion is started

Note 17 The specifications for these parameters are valid after an Auto-Cal cycle has been completed

Note 18 The ADC12441 reference ladder is composed solely of capacitors

Note 19 A Military RETS Electrical Test Specification is available on request At time of printing the ADC12441CMJ 883 RETS complies fully with the boldface

limits in this column

FIGURE 1a Transfer Characteristic

5

TL H 11017 – 5

5 Page

2 0 Functional Description (Continued)

Digital Control Inputs

CS WR RD CAL AZ

A D Function

1

1

1

1

1XX

0X1

1 1 Start Conversion without Auto-Zero

1 1 Read Conversion Result without Auto-Zero

1 0 Start Conversion with Auto-Zero

1 0 Read Conversion Result with Auto-Zero

X Start Calibration Cycle

0 X Test Mode (DB2 DB3 DB5 and DB6 become active)

FIGURE 1 Function of the A D Control Inputs

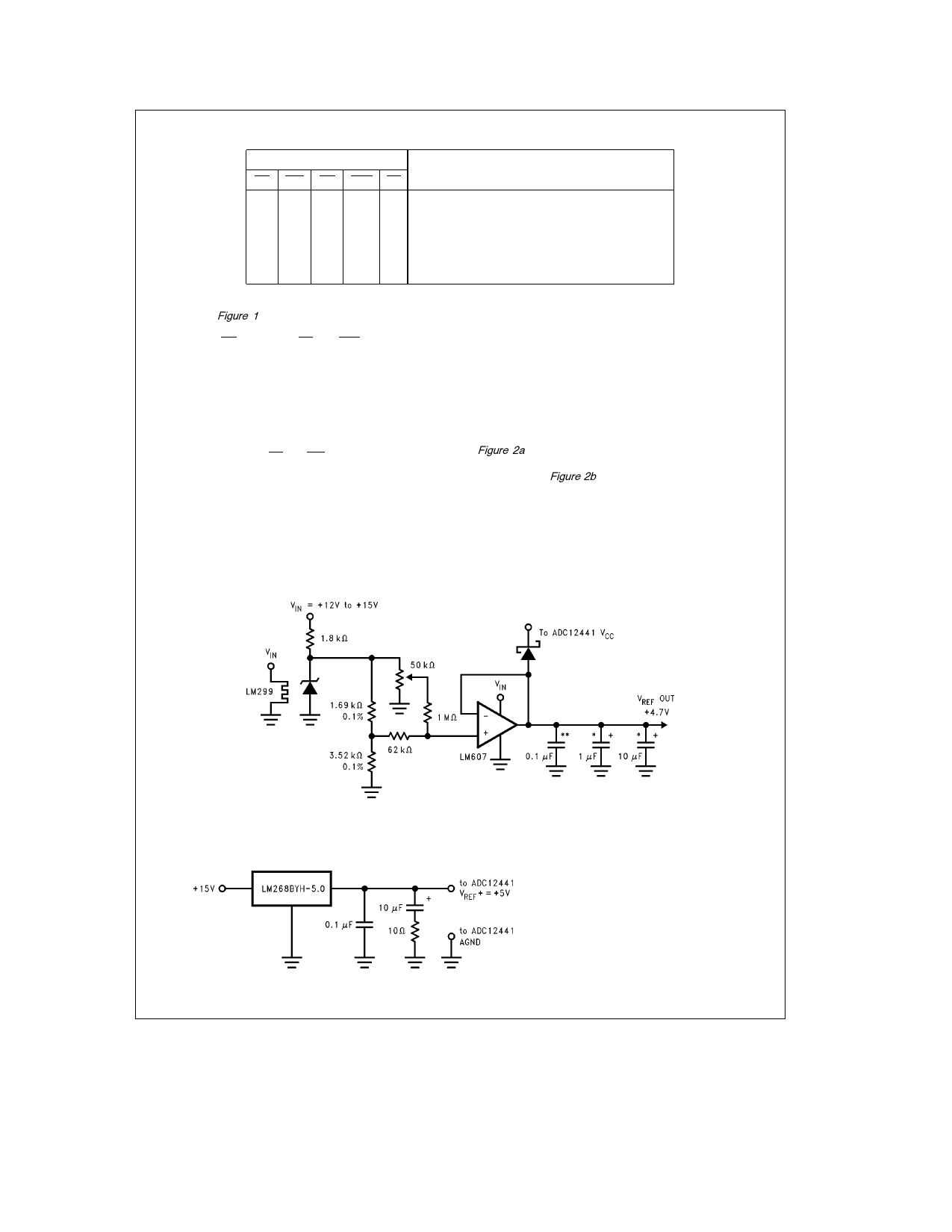

The table in Figure 1 summarizes the effect of the digital

control inputs on the function of the ADC12441 The Test

Mode where RD is high and CS and CAL are low is used

during manufacture to thoroughly check out the operation of

the ADC12441 Care should be taken not to inadvertently

be in this mode since DB2 DB3 DB5 and DB6 become

active outputs which may cause data bus contention

2 2 RESETTING THE A D

All internal logic can be reset which will abort any conver-

sion in process The A D is reset whenever a new conver-

sion is started by taking CS and WR low If this is done when

the analog input is being sampled or when EOC is low the

Auto-Cal correction factors may be corrupted therefore re-

quiring an Auto-Cal cycle before the next conversion This is

true with or without Auto-Zero The Calibration Cycle cannot

be reset once started On power-up the ADC12441 auto-

matically goes through a Calibration Cycle that takes typi-

cally 1396 clock cycles For reasons that will be discussed

in Section 3 7 a new calibration cycle needs to be started

after the completion of the automatic one

3 0 Analog Considerations

3 1 REFERENCE VOLTAGE

The voltage applied to the reference input of the converter

defines the voltage span of the analog input (the difference

between VIN and AGND) over which 4095 positive output

codes and 4096 negative output codes exist The A-to-D

can be used in either ratiometric or absolute reference ap-

plications The voltage source driving VREF must have a

very low output impedance and very low noise The circuit in

Figure 2a is an example of a very stable reference that is

appropriate for use with the ADC12441 The simple refer-

ence circuit of Figure 2b may be used when the application

does not require low full scale errors

In a ratiometric system the analog input voltage is propor-

tional to the voltage used for the A D reference When this

voltage is the system power supply the VREF pin can be

tied to VCC This technique relaxes the stability requirement

of the system reference as the analog input and A D refer-

ence move together maintaining the same output code for

given input condition

Tantalum

Ceramic

FIGURE 2a Low Drift Extremely Stable Reference Circuit

TL H 11017 – 19

Errors without any trims

25 C

Full Scale

g0 075%

Zero

g0 024%

Linearity

g LSB

TL H 11017 – 20

FIGURE 2b Simple Reference Circuit

b40 C to a85 C

g0 2%

g0 024%

g LSB

11

11 Page | ||

| Páginas | Total 14 Páginas | |

| PDF Descargar | [ Datasheet ADC12441CMJ.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ADC12441CMJ | Dynamically-Tested Self-Calibrating 12-Bit Plus Sign A/D Converter with Sample-and-Hold | National Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |