|

|

PDF AD1555 Data sheet ( Hoja de datos )

| Número de pieza | AD1555 | |

| Descripción | 24-Bit ADC WITH LOW NOISE PGA | |

| Fabricantes | Analog Devices | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AD1555 (archivo pdf) en la parte inferior de esta página. Total 24 Páginas | ||

|

No Preview Available !

a

24-Bit ⌺-⌬ ADC

with Low Noise PGA

AD1555/AD1556

FEATURES

AD1555

Fourth Order ⌺-⌬ Modulator

Large Dynamic Range

116 dB Min, 120 dB Typical @ 1 ms

117 dB Typical @ 0.5 ms

Low Input Noise: 80 nV rms @ 4 ms with

Gain of 34,128

Low Distortion: –111 dB Max, –120 dB Typical

Low Intermodulation: 122 dB

Sampling Rate at 256 kSPS

Very High Jitter Tolerance

No External Antialias Filter Required

Programmable Gain Front End

Input Range: ؎2.25 V

Robust Inputs

Gain Settings: 1, 2.5, 8.5, 34, 128

Common-Mode Rejection (DC to 1 kHz)

93 dB Min, 101 dB Typical @ Gain of 1

77 mW Typical Low Power Dissipation

Standby Modes

AD1556

FIR Digital Filter/Decimator

Serial or Parallel Selection of Configuration

Output Word Rates: 250 SPS to 16 kSPS

6.2 mW Typ Low Power Dissipation

70 W in Standby Mode

Reference Design and Evaluation Board with

Software Available

APPLICATIONS

Seismic Data Acquisition Systems

Chromatography

Automatic Test Equipment

GENERAL DESCRIPTION

The AD1555 is a complete sigma-delta modulator, combined

with a programmable gain amplifier intended for low frequency,

high dynamic range measurement applications. The AD1555

outputs a ones-density bitstream proportional to the analog

input. When used in conjunction with the AD1556 digital filter/

decimator, a high performance ADC is realized.

The continuous-time analog modulator input architecture avoids

the need for an external antialias filter. The programmable gain

front end simplifies system design, extends the dynamic range,

and reduces the system board area. Low operating power and

standby modes makes the AD1555 ideal for remote battery-pow-

ered data acquisition systems.

The AD1555 is fabricated on Analog Devices’ BiCMOS process

that has high performance bipolar devices along with CMOS

transistors. The AD1555 and AD1556 are packaged, respectively,

in 28-lead PLCC and 44-lead MQFP packages and are specified

from –55°C to +85°C (AD1556 and AD1555 B Grade) and from

0°C to 85°C (AD1555 A Grade).

0

–20

–40

–60

–80

–100

fIN = 24.4Hz

SNR = 116.7dB

THD = –120.6dB

–120

–140

–160

–180

–200

0

50 100 150 200 250 300 350 400 450 500

FREQUENCY – Hz

Figure 1. FFT Plot, Full-Scale AIN Input, Gain of 1

FUNCTIONAL BLOCK DIAGRAM

AIN (+)

AIN (–)

TIN (+)

TIN (–)

REFIN REFCAP2 REFCAP1 AGND3

REF DIVIDER

DAC

MODE CONTROL

LOGIC

OVERVOLTAGE

DETECTION

PGA

MUX

LOOP

FILTER

AD1555

CLOCK

GENERATION

CB0...CB4

MFLG

CSEL

TDATA

MDATA

MCLK

PGA0...PGA4 H/S

ERROR

PGA

CONTROL

CONFIGURATION

REGISTER

INPUT SHIFT

REGISTER

STATUS

REGISTER

INPUT

MUX

DIGITAL

FILTER

DATA

OUTPUT

MUX

CLOCK DIVIDER

DATA

REGISTER

AD1556

DIN

SCLK

CS

R/W

DOUT

DRDY

RSEL

AGND1

REV. B

PGAOUT MODIN AGND2 +VA –VA

VL DGND

CLKIN SYNC BW0...BW2 RESET PWRDN GND VL

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700

www.analog.com

Fax: 781/326-8703

© Analog Devices, Inc., 2002

1 page

AD1555/AD1556

TIMING SPECIFICATIONS (+VA = +5 V ؎ 5%; –VA = –5 V ؎ 5%; AD1555 VL = 5 V ؎ 5%, AD1556 VL = 2.85 V to 5.25 V;

CLKIN = 1.024 MHz; AGND = DGND = 0 V; CL = 50 pF; TA = TMIN to TMAX, unless otherwise noted)

Symbol

Min

Typ

Max

Unit

CLKIN Frequency1

CLKIN Duty Cycle Error

MCLK Output Frequency1

SYNC Setup Time

SYNC Hold Time

CLKIN Rising to MCLK Output Falling on SYNC

CLKIN Falling to MCLK Output Rising

CLKIN Falling to MCLK Output Falling

MCLK Input Falling to MDATA Falling

MCLK Input Rising to MDATA and MFLG Valid

TDATA Setup Time after SYNC

TDATA Hold Time

fCLKIN

t1

t2

t3

t4

t5

t6

t7

t8

t9

0.975

45

10

10

5

5

1.024

fCLKIN/4

1.075

55

20

20

20

30

100

MHz

%

ns

ns

ns

ns

ns

ns

ns

ns

ns

RESET Setup Time

RESET Hold Time

t10 15

t11 15

ns

ns

CLKIN Falling to DRDY Rising

CLKIN Rising to DRDY Falling2

CLKIN Rising to ERROR Falling

t12

t13

t14

RSEL to Data Valid

RSEL Setup to SCLK Falling

DRDY to Data Valid

DRDY High Setup to SCLK Falling

R/W to Data Valid

R/W High Setup to SCLK Falling

CS to Data Valid

CS Low Setup to SCLK Falling

SCLK Rising to DOUT Valid

SCLK High Pulsewidth

SCLK Low Pulsewidth

SCLK Period

SCLK Falling to DRDY Falling2

CS High or R/W Low to DOUT Hi-Z

t15

t16 10

t17

t18 10

t19

t20 10

t21

t22 10

t23

t24 25

t25 25

t26 70

t27

t28

R/W Low Setup to SCLK Falling

CS Low Setup to SCLK Falling

Data Setup Time to SCLK Falling

Data Hold Time after SCLK Falling

R/W Hold Time after SCLK Falling

t29 10

t30 10

t31 10

t32 10

t33 10

NOTES

1The gain of the modulator is proportional to fCLKIN and MCLK frequency.

2With DRDYBUF low only. When DRDYBUF is high, this timing also depends on the value of the external pull-down resistor.

Specifications subject to change without notice.

20

20

50

25

25

25

25

25

20

20

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

1.6mA IOL

TO OUTPUT

PIN CL

50pF

500A IOH

1.4V

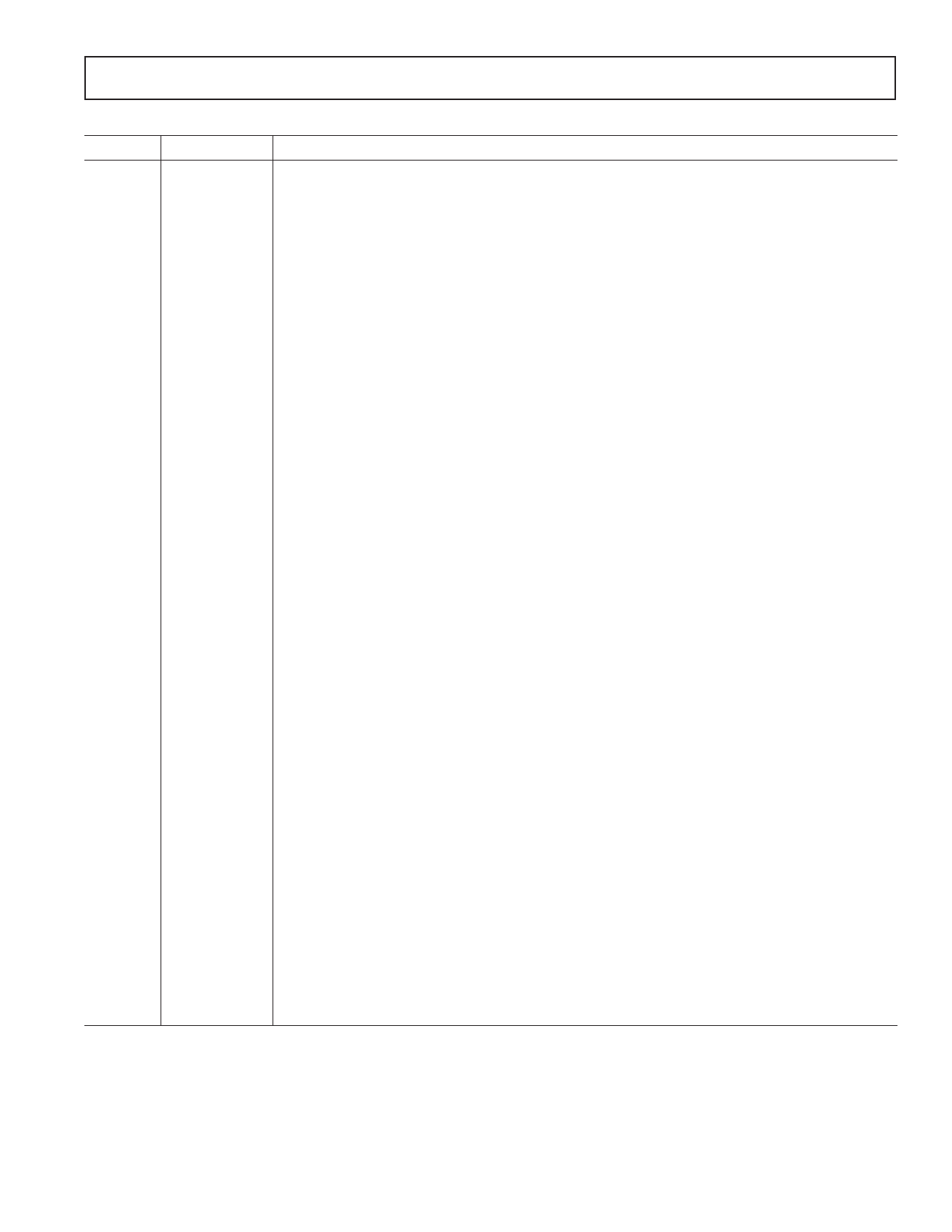

Figure 2. Load Circuit for Digital Interface Timing

REV. B

–5–

5 Page

Pin No.

14

15

16

17

18

19

20

25

26

29

30

31

32

35

36

37

38

43–39

AD1555/AD1556

Mnemonic

DOUT

DRDY

CS

R/W

RSEL

DIN

ERROR

RESET

PWRDN

CSEL

TDATA

SYNC

CLKIN

MCLK

MDATA

RESETD

MFLG

CB0–CB4

AD1556 PIN FUNCTION DESCRIPTIONS (continued)

Description

Serial Data Output. DOUT is used to access the conversion results or the contents of the Status

Register, depending on the logic state of the RSEL pin. At the beginning of a read operation, the

first data bit is output (MSB first). The data changes on the rising edge of SCLK and is valid on the

SCLK falling edge.

Data Ready. A logic high output indicates that data is ready to be accessed from the Output Data

Register. DRDY goes low once a read operation is complete. When selected, the DRDY output pin

has a type buffer that allows wired-OR connection of multiple AD1556s.

Chip Select. When set low the serial data interface pins DIN, DOUT, R/W, and SCLK are active; a

logic high disables these pins and sets the DOUT pin to Hi-Z.

Read/Write. A read operation is initiated if R/W is high and CS is low. A low sets the DOUT pin to

Hi-Z and allows a write operation to the device via the DIN pin.

Register Select. When set high, the Conversion Data Register contents are output on a read opera-

tion. A low selects the Status Register.

Serial Data Input. Used during a write operation. Loads the Configuration Register via the Input

Shift Register. Data is loaded MSB first and must be valid on the falling edge of SCLK.

Error Flag. A logic low output indicates an error condition occurred in the modulator or digital

filter. When ERROR goes low the ERROR bit in the status register is set high. The ERROR output

pin has an open drain type buffer with an internal 100 kΩ typical pull-up that allows wired-OR

connection of multiple AD1556s.

Chip Reset. A logic high input clears any error condition in the status register and sets the configuration

register to the state of the corresponding hardware pins. On power-up, this reset state is entered.

Power-Down Hardware Control. A logic high input powers down the filter. The convolution cycles

in the digital filter and the MCLK signal are stopped. All registers retain their data and the serial

data interface remains active. The power-down mode is entered on the first falling edge of CLKIN

after PWRDN is taken high. When exiting the power-down mode, a SYNC must be applied to

resume filter convolutions.

Filter Input Select. Selects the source for input to the digital filter. A logic high selects the TDATA

input, a low selects MDATA as the filter input.

Test Data. Input to digital filter for user test data.

Synchronization Input. The SYNC input clears the AD1556 filter in order to synchronize the start

of the filter convolutions. The SYNC event is initiated on the first CLKIN rising edge after the

SYNC pin goes high. The SYNC input can also be applied synchronously to the AD1556 decima-

tion rate without resetting the convolution cycles.

Clock Input. The clock input signal, nominally 1.024 MHz, provides the necessary clock for the

AD1556. This clock frequency is divided by four to generate the MCLK signal for the AD1555.

Modulator Clock. Provides the modulator sampling clock frequency. The modulator always samples

at one-fourth the CLKIN frequency.

Modulator Data. This input receives the ones-density bit stream from the AD1555 for input to the

digital filter.

Decimator Reset. A logic high resets the decimator of the digital filter.

Modulator Error. The MFLG input is used to detect if an overrange condition occurred in the

modulator. Its logic level is sensed on the rising edge of CLKIN. When overrange condition

detected, ERROR goes low and updates the status register.

Modulator Control. These output control pins represent a portion of the data loaded into the AD1556

Configuration Register. CB0–CB2 are generally used to set the PGA gain or cause it to enter in the

PGA standby mode (Refer to Table III). CB3 and CB4 select the mux input voltage applied to the

PGA as described in Table III.

REV. B

–11–

11 Page | ||

| Páginas | Total 24 Páginas | |

| PDF Descargar | [ Datasheet AD1555.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AD1555 | 24-Bit ADC WITH LOW NOISE PGA | Analog Devices |

| AD1556 | 24-Bit ADC WITH LOW NOISE PGA | Analog Devices |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |