|

|

PDF AD14160 Data sheet ( Hoja de datos )

| Número de pieza | AD14160 | |

| Descripción | Quad-SHARC DSP Multiprocessor Family | |

| Fabricantes | Analog Devices | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AD14160 (archivo pdf) en la parte inferior de esta página. Total 52 Páginas | ||

|

No Preview Available !

a

PERFORMANCE FEATURES

ADSP-21060 Core Processor (. . . ؋4)

480 MFLOPS Peak, 320 MFLOPS Sustained

25 ns Instruction Rate, Single-Cycle

Instruction Execution–Each of Four Processors

16 Mbit Shared SRAM (Internal to SHARCs)

4 Gigawords Addressable Off-Module Memory

Sixteen 40 Mbyte/s Link Ports (Four per SHARC)

Eight 40 Mbit/s Independent Serial Ports (Two

from Each SHARC)

5 V and 3.3 V Operation

32-Bit Single Precision and 40-Bit Extended

Precision IEEE Floating Point Data Formats, or

32-Bit Fixed Point Data Format

IEEE JTAG Standard 1149.1 Test Access Port and

On-Chip Emulation

PACKAGING FEATURES

452-Lead Ceramic Ball Grid Array (CBGA)

1.85" (47 mm) Body Size

0.200" Max Height

0.050" Ball Pitch

29 Grams (typical)

JC = 0.36؇C/W

Quad-SHARC®

DSP Multiprocessor Family

AD14160/AD14160L

FUNCTIONAL BLOCK DIAGRAM

ID2-0

CPA

SPORT 1

SPORT 0

TDI

SHARC_A

LINK 0

LINK 5

TDO

LINK 0

LINK 5

TDI

SHARC_B

ID2-0

CPA

SPORT 1

SPORT 0

AD14160/

AD14160L

SHARC BUS (ADDR31-0, DATA47-0, MS3-0, RD, WR, PAGE, ADRCLK, SW, ACK,

SBTS, HBR, HBG, REDY, BR6-1, RPBA, DMAR1.2, DMAG1.2)

ID2-0

CPA SHARC_D

SPORT 1

SPORT 0

TDO

LINK 0

LINK 5

TDI

LINK 0 SHARC_C

LINK 5

TDO

ID2-0

CPA

SPORT 1

SPORT 0

GENERAL DESCRIPTION

The AD14160/AD14160L Quad-SHARC Ceramic Ball Grid

Array (CBGA) puts the power of the first generation AD14060

(CQFP) DSP multiprocessor into a very high density ball grid

array package; now with additional link and serial I/O pinned

out, beyond that from the CQFP package. The core of the multi-

processor is the ADSP-21060 DSP microcomputer. The AD14x60

modules have the highest performance—density and lowest

cost— performance ratios of any in their class. They are ideal

for applications requiring higher levels of performance and/or

functionality per unit area.

The AD14160/AD14160L takes advantage of the built-in

multiprocessing features of the ADSP-21060 to achieve 480 peak

MFLOPS with a single chip type, in a single package. The on-

chip SRAM of the DSPs provides 16 Mbits of on-module

shared SRAM. The complete shared bus (48 data, 32 address)

is also brought off-module for interfacing with expansion

memory or other peripherals.

SHARC is a registered trademark of Analog Devices, Inc.

The ADSP-21060 link ports are interconnected to provide

direct communication among the four SHARCs as well as high

speed off-module access. Internally, links connect the SHARC

in a ring. Externally, each SHARC has a total of 160 Mbytes/s

link port bandwidth.

Multiprocessor performance is enhanced with embedded power

and ground planes, matched impedance interconnect, and opti-

mized signal routing lengths and separation. The fully tested

and ready-to-insert multiprocessor also significantly reduces

board space.

s

s

s

s

REV. A

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 World Wide Web Site: http://www.analog.com

Fax: 781/326-8703

© Analog Devices, Inc., 1998

1 page

1x

CLOCK

RESET

AD14160/AD14160L

AD14160/

AD14160L

CLKIN

RESET

RPBA

3

ID

ADDR31–0

DATA47–0

RD

WR

ACK

MS3–0

CONTROL

SERIALS

LINKS

DISCRETES

BMS

PAGE

SBTS

SW

ADRCLK

CS

HBR

HBG

REDY

CPA

BR2–6

BR1

5

ADSP-2106x #5

(OPTIONAL)

CLKIN

ADDR31–0

RESET

DATA47–0

RPBA

3

ID

CONTROL

ADDR

DATA

GLOBAL

MEMORY

OE AND

WE PERIPHERALS

ACK (OPTIONAL)

CS

CS

ADDR

DATA

BOOT

EPROM

(OPTIONAL)

ADDR

HOST

PROCESSOR

INTERFACE

(OPTIONAL)

DATA

CPA

BR1, 2, 3, 4, 6

BR5

5

ADSP-2106x #6

(OPTIONAL)

CLKIN

RESET

ADDR31–0

DATA47–0

RPBA

3

ID

CONTROL

CPA

BR1–5

BR6

5

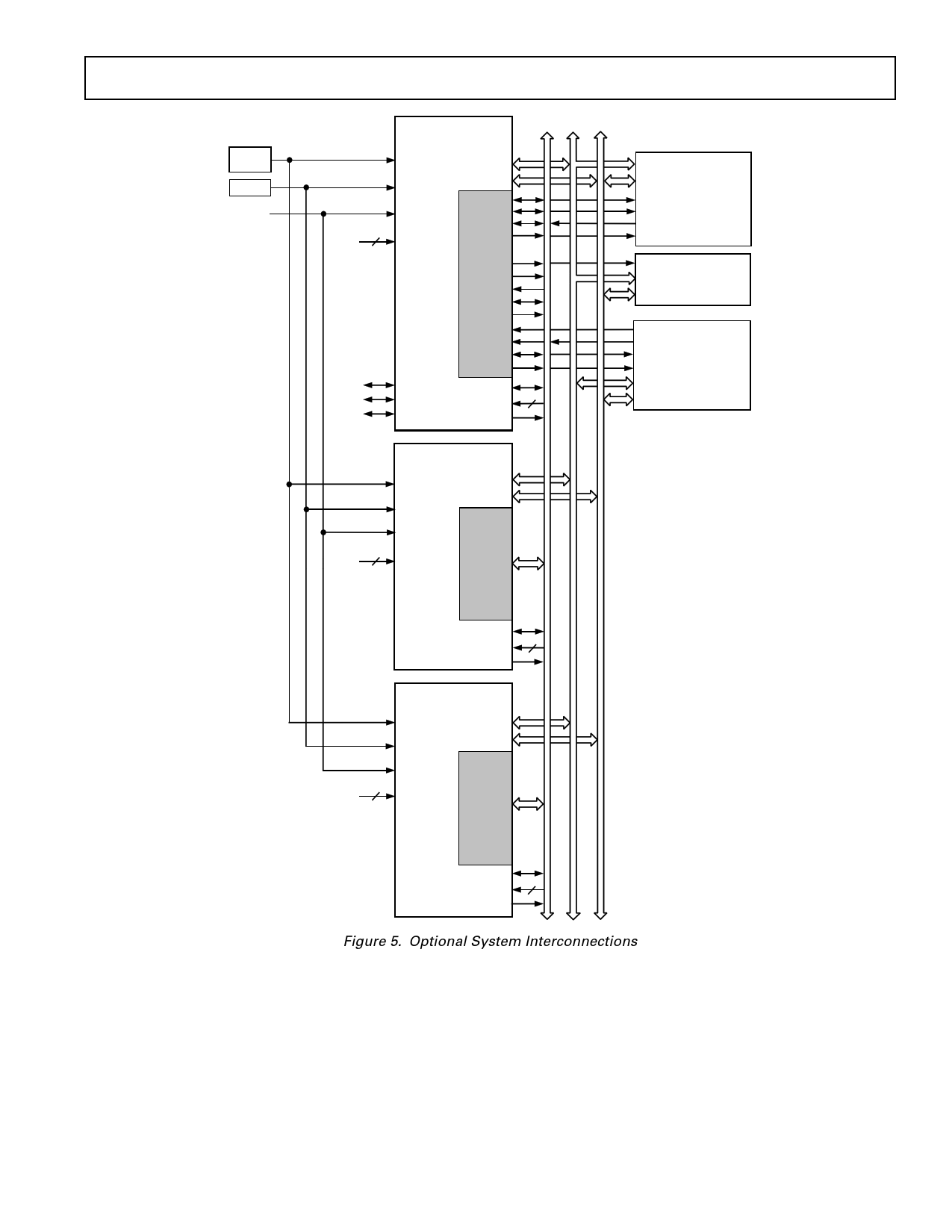

Figure 5. Optional System Interconnections

REV. A

–5–

5 Page

AD14160/AD14160L

Pin

BMSBCD

TIMEXPy

CLKIN

RESET

TCK

TMS

TDI

TDO

TRST

EMU (O/D)

VDD

GND

Type

I/O/T2

O

I

I/A

I

I/S

I/S

O

I/A

O

P

G

Function

Boot Memory Select. Output: Used as chip select for boot EPROM devices (when EBOOTBCD = 1,

LBOOTBCD = 0). In a multiprocessor system, BMS is output by the bus master. Input: When low,

indicates that no booting will occur and that SHARC_B, C, D will begin executing instructions from

external memory. See table below. This input is a system configuration selection which should be

hardwired.

EBOOT LBOOT BMS

Booting Mode

1 0 Output EPROM (Connect BMS to EPROM chip select)

0 0 1 (Input) Host Processor

0 1 1 (Input) Link Port

0 0 0 (Input) No Booting. Processor executes from external memory.

0 1 0 (Input) Reserved

1 1 x (Input) Reserved

Timer Expired. (Individual TIMEXP from y = SHARC_A, SHARC_B, SHARC_C, SHARC_D) Asserted

for four cycles when the timer is enabled and TCOUNT decrements to zero.

Clock In. (Common to all SHARCs) External clock input to the AD14160/AD14160L. The instruction

cycle rate is equal to CLKIN. CLKIN may not be halted, changed, or operated below the minimum specified

frequency.

Module Reset. (Common to all SHARCs) Resets the AD14160/AD14160L to a known state. This input

must be asserted (low) at power-up.

Test Clock (JTAG). (Common to all SHARCs) Provides an asynchronous clock for JTAG boundary

scan.

Test Mode Select (JTAG). (Common to all SHARCs) Used to control the test state machine. TMS has

a 20 kΩ internal pull-up resistor.

Test Data Input (JTAG). Provides serial data for the boundary scan logic chain starting at SHARC_A.

TDI has a 20 kΩ internal pull-up resistor.

Test Data Output (JTAG). Serial scan output of the boundary scan chain path, from SHARC_D.

Test Reset (JTAG). (Common to all SHARCs) Resets the test state machine. TRST must be asserted

(pulsed low) after power-up or held low for proper operation of the AD14160/AD14160L. TRST has a

20 kΩ internal pull-up resistor.

Emulation Status. (Common to all SHARCs) Must be connected to the ADSP-2106x EZ-ICE target

board connector only.

Power Supply. Nominally +5.0 V dc for 5 V devices or +3.3 V dc for 3.3 V devices (50 pins).

Power Supply Return. (64 pins).

NOTES

1LINK PORTS 0 and 5 are connected internally as described earlier in Link Port I/O.

2Three-statable only in EPROM boot mode (when BMS is an output).

REV. A

–11–

11 Page | ||

| Páginas | Total 52 Páginas | |

| PDF Descargar | [ Datasheet AD14160.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AD14160 | Quad-SHARC DSP Multiprocessor Family | Analog Devices |

| AD14160L | Quad-SHARC DSP Multiprocessor Family | Analog Devices |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |