|

|

PDF AD5532 Data sheet ( Hoja de datos )

| Número de pieza | AD5532 | |

| Descripción | 32-Channel/ 14-Bit Voltage-Output DAC | |

| Fabricantes | Analog Devices | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AD5532 (archivo pdf) en la parte inferior de esta página. Total 16 Páginas | ||

|

No Preview Available !

a

32-Channel, 14-Bit

Voltage-Output DAC

AD5532*

FEATURES

High Integration: 32-Channel DAC in 12 ؋ 12 mm2 LFBGA

Adjustable Voltage Output Range

Guaranteed Monotonic

Readback Capability

DSP-/Microcontroller-Compatible Serial Interface

Output Impedance

0.5 ⍀ (AD5532-1, AD5532-2)

500 ⍀ (AD5532-3)

1 k⍀ (AD5532-5)

Output Voltage Span

10 V (AD5532-1, AD5532-3, AD5532-5)

20 V (AD5532-2)

Infinite Sample-and-Hold Capability to ؎0.018% Accuracy

Temperature Range –40؇C to +85؇C

APPLICATIONS

Level Setting

Instrumentation

Automatic Test Equipment

Industrial Control Systems

Data Acquisition

Low Cost I/O

GENERAL DESCRIPTION

The AD5532 is a 32-channel voltage-output 14-bit DAC with

an additional infinite sample-and-hold mode. The selected DAC

register is written to via the 3-wire serial interface and VOUT

for this DAC is then updated to reflect the new contents of the

DAC register. DAC selection is accomplished via address bits

A0–A4. The output voltage range is determined by the offset

voltage at the OFFS_IN pin and the gain of the output amplifier.

It is restricted to a range from VSS + 2 V to VDD – 2 V because

of the headroom of the output amplifier.

The device is operated with AVCC = 5 V ± 5%, DVCC = 2.7 V

to 5.25 V, VSS = –4.75 V to –16.5 V and VDD = 8 V to 16.5 V

and requires a stable +3 V reference on REF_IN as well as an

offset voltage on OFFS_IN.

PRODUCT HIGHLIGHTS

1. 32-channel, 14-bit DAC in one package, guaranteed

monotonic.

2. The AD5532 is available in a 74-lead LFBGA package with

a body size of 12 mm × 12 mm.

3. Droopless/Infinite Sample-and-Hold Mode.

FUNCTIONAL BLOCK DIAGRAM

VIN

TRACK / RESET

BUSY

DAC GND

AGND

DGND

SER /PAR

DVCC AVCC REF IN REF OUT OFFS IN VDD VSS

AD5532

ADC

DAC

VOUT 0

MUX

INTERFACE

CONTROL

LOGIC

SCLK DIN DOUT

DAC

DAC

VOUT 31

OFFS OUT

ADDRESS INPUT REGISTER

WR

SYNC / CS A4 –A0 CAL OFFSET SEL

*Protected by U.S. Patent No. 5,969,657; other patents pending.

REV. 0

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 World Wide Web Site: http://www.analog.com

Fax: 781/326-8703

© Analog Devices, Inc., 2000

1 page

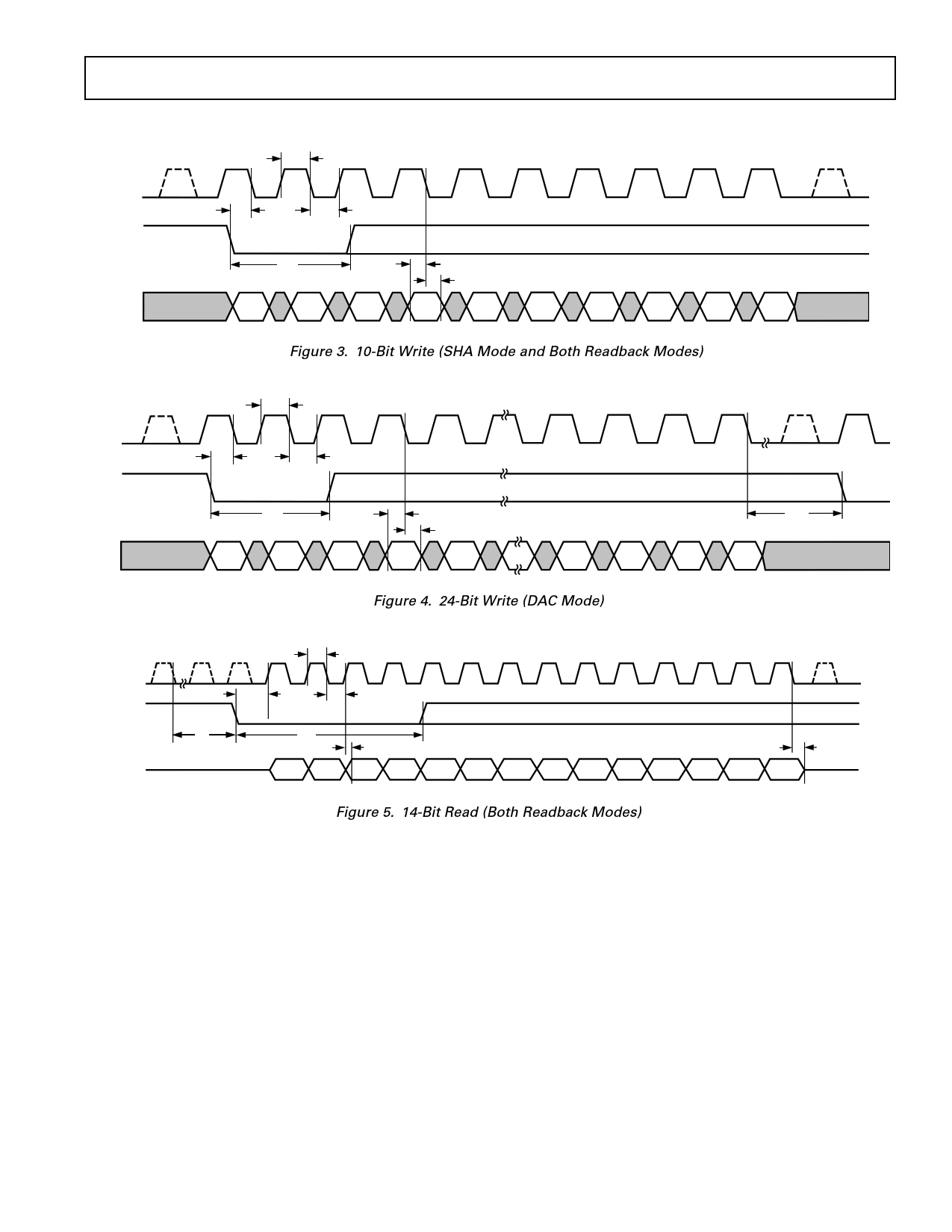

SERIAL INTERFACE TIMING DIAGRAMS

SCLK

SYNC

DIN

t1

1234 56789

t3 t2

t4 t5

t6

MSB

Figure 3. 10-Bit Write (SHA Mode and Both Readback Modes)

AD5532

10

LSB

SCLK

SYNC

DIN

t1

12 34 5

t3 t2

21 22 23 24

t4

MSB

t5

t6

Figure 4. 24-Bit Write (DAC Mode)

t 11

LSB

1

SCLK 10

SYNC

DOUT

t10

t1

1 2 3 4 5 6 7 8 9 10 11 12 13 14

t7 t2

t4

t8

t9

MSB

Figure 5. 14-Bit Read (Both Readback Modes)

LSB

REV. 0

–5–

5 Page

AD5532

FUNCTIONAL DESCRIPTION

The AD5532 can be thought of as consisting of 32 DACs and

an ADC (for SHA mode) in a single package. In DAC mode a

14-bit digital word is loaded into one of the 32 DAC registers

via the serial interface. This is then converted (with gain and

offset) into an analog output voltage (VOUT0–VOUT31).

To update a DAC’s output voltage the required DAC is addressed

via the serial port. When the DAC address and code have been

loaded the selected DAC converts the code.

On power-on, all the DACs, including the offset channel, are

loaded with zeros. The internal DAC outputs are at 50 mV

typical (negative full-scale). If the OFFS_IN pin is driven by

the on-board offset channel, the outputs VOUT0 to VOUT31 are

also at 50 mV on power-on since OFFS_IN = 50 mV, VOUT =

(Gain × VDAC) –(Gain –1) × VOFFS_IN = 50 mV.

Output Buffer Stage—Gain and Offset

The function of the output buffer stage is to translate the 0 V–3 V

output of the DAC to a wider range. This is done by gaining up

the DAC output by 3.52/7 and offsetting the voltage by the

voltage on OFFS_IN pin.

AD5532-1/AD5532-3/AD5532-5:

VOUT = 3.52 × VDAC – 2.52 × VOFFS_IN

AD5532-2:

VOUT = 7 × VDAC – 6 × VOFFS_IN

VDAC is the output of the DAC.

VOFFS_IN is the voltage at the OFFS_IN pin.

The following table shows how the output range on VOUT relates

to the offset voltage supplied by the user:

Table I. Sample Output Voltage Ranges

VOFFS_IN

(V)

0.5

1

VDAC

(V)

0 to 3

0 to 3

VOUT

(AD5532-1/-3/-5)

–1.26 to +9.3

–2.52 to +8.04

VOUT

(AD5532-2)

Headroom Limited

–6 to +15

VOUT is limited only by the headroom of the output amplifiers.

VOUT must be within maximum ratings.

Offset Voltage Channel

The offset voltage can be externally supplied by the user at

OFFS_IN or it can be supplied by an additional offset volt-

age channel on the device itself. The offset can be set up in

two ways. In SHA mode the required offset voltage is set up

on VIN and acquired by the offset channel. In DAC mode the

code corresponding to the offset value is loaded directly into

the offset DAC. This offset channel’s DAC output is directly

connected to OFFS_OUT. By connecting OFFS_OUT to OFFS_IN

this offset voltage can be used as the offset voltage for the 32

output amplifiers. It is important to choose the offset so that

VOUT is within maximum ratings.

Reset Function

The reset function on the AD5532 can be used to reset all nodes

on this device to their power-on-reset condition. This is imple-

mented by applying a low-going pulse of between 50 ns and 150 ns

to the TRACK/RESET pin on the device. If the applied pulse is

less than 50 ns it is assumed to be a glitch and no operation

takes place. If the applied pulse is wider than 150 ns this pin

adopts its track function on the selected channel, VIN is switched

to the output buffer and an acquisition on the channel will not

occur until a rising edge of TRACK.

SHA Mode

In SHA mode the input voltage VIN is sampled and converted

into a digital word. The noninverting input to the output buffer

(gain and offset stage) is tied to VIN during the acquisition period

to avoid spurious outputs while the DAC acquires the correct

code. This is completed in 16 µs max. At this time the updated

DAC output assumes control of the output voltage. The output

voltage of the DAC is connected to the noninverting input of

the output buffer. Since the channel output voltage is effectively

the output of a DAC there is no droop associated with it. As

long as power is maintained to the device the output voltage will

remain constant until this channel is addressed again.

Analog Input (SHA Mode)

The equivalent analog input circuit is shown in Figure 17. The

Capacitor C1 is typically 20 pF and can be attributed to pin

capacitance and 32 off-channels. When a channel is selected, an

extra 7.5 pF (typ) is switched in. This Capacitor C2 is charged

to the previously acquired voltage on that particular channel

so it must charge/discharge to the new level. It is essential that the

external source can charge/discharge this additional capaci-

tance within 1 µs–2 µs of channel selection so that VIN can be

acquired accurately. For this reason a low impedance source

is recommended.

VIN

C1

20pF

ADDRESSED CHANNEL

C2

7.5pF

Figure 17. Analog Input Circuit

Large source impedances will significantly affect the performance

of the ADC. This may necessitate the use of an input buffer

amplifier.

TRACK Function (SHA Mode)

Normally in SHA mode of operation, TRACK is held high and

the channel begins to acquire when it is addressed. However, if

TRACK is low when the channel is addressed, VIN is switched to

the output buffer and an acquisition on the channel will not

occur until a rising edge of TRACK. At this stage the BUSY pin

will go low until the acquisition is complete, at which point the

DAC assumes control of the voltage to the output buffer and

VIN is free to change again without affecting this output value.

REV. 0

–11–

11 Page | ||

| Páginas | Total 16 Páginas | |

| PDF Descargar | [ Datasheet AD5532.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AD5530 | Serial Input/ Voltage Output 12-/14-Bit DACs | Analog Devices |

| AD5531 | Serial Input/ Voltage Output 12-/14-Bit DACs | Analog Devices |

| AD5532 | 32-Channel/ 14-Bit Voltage-Output DAC | Analog Devices |

| AD5532B | 14-Bit DAC | Analog Devices |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |