|

|

PDF AD5300 Data sheet ( Hoja de datos )

| Número de pieza | AD5300 | |

| Descripción | 8-Bit DAC | |

| Fabricantes | Analog Devices | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AD5300 (archivo pdf) en la parte inferior de esta página. Total 13 Páginas | ||

|

No Preview Available !

2.7 V to 5.5 V, 140 μA, Rail-to-Rail Output

8-Bit DAC in a SOT-23

AD5300

FEATURES

Single 8-Bit DAC

6-Lead SOT-23 and 8-Lead MSOP Packages

Micropower Operation: 140 μA @ 5 V

Power-Down to 200 nA @ 5 V, 50 nA @ 3 V

2.7 V to 5.5 V Power Supply

Guaranteed Monotonic by Design

Reference Derived from Power Supply

Power-On Reset to 0 V

3 Power-Down Functions

Low Power Serial Interface with Schmitt-Triggered Inputs

On-Chip Output Buffer Amplifier, Rail-to-Rail Operation

SYNC Interrupt Facility

Qualified for automotive applications

APPLICATIONS

Portable Battery-Powered Instruments

Digital Gain and Offset Adjustment

Programmable Voltage and Current Sources

Programmable Attenuators

GENERAL DESCRIPTION

The AD5300 is a single, 8-bit buffered voltage output DAC that

operates from a single 2.7 V to 5.5 V supply, consuming 115 μA

at 3 V. Its on-chip precision output amplifier allows rail-to-rail

output swing to be achieved. The AD5300 uses a versatile 3-wire

serial interface that operates at clock rates up to 30 MHz and is

compatible with standard SPI®, QSPI™, MICROWIRE™, and

DSP interface standards.

The reference for the AD53001 is derived from the power supply

inputs and thus gives the widest dynamic output range. The part

incorporates a power-on reset circuit that ensures that the DAC

output powers up to 0 V and remains there until a valid write takes

place to the device. The part contains a power-down feature that

reduces the current consumption of the device to 200 nA at 5 V

and provides software selectable output loads while in power-

down mode. The part is put into power-down mode over the

serial interface.

The low power consumption of this part in normal operation

makes it ideally suited to portable battery-operated equipment.

The power consumption is 0.7 mW at 5 V, reducing to 1 μW in

power-down mode.

The AD5300 is one of a family of pin-compatible DACs. The

AD5310 is the 10-bit version, and the AD5320 is the 12-bit

version. The AD5300/AD5310/AD5320 are available in 6-lead

SOT-23 packages and 8-lead MSOP packages.

Rev. D

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarksandregisteredtrademarksarethepropertyoftheirrespectiveowners.

FUNCTIONAL BLOCK DIAGRAM

VDD GND

POWER-ON

RESET

DAC

REGISTER

REF (+) REF (–)

8-BIT

DAC

AD5300

OUTPUT

BUFFER

VOUT

INPUT

CONTROL

LOGIC

POWER-DOWN

CONTROL LOGIC

RESISTOR

NETWORK

SYNC SCLK DIN

PRODUCT HIGHLIGHTS

1. Available in 6-lead SOT-23 and 8-lead MSOP packages.

2. Low power, single-supply operation. This part operates from a

single 2.7 V to 5.5 V supply and typically consumes 0.35 mW

at 3 V and 0.7 mW at 5 V, making it ideal for battery-powered

applications.

3. The on-chip output buffer amplifier allows the output of

the DAC to swing rail-to-rail with a slew rate of 1 V/μs.

4. Reference derived from the power supply.

5. High speed serial interface with clock speeds up to 30 MHz.

Designed for very low power consumption. The interface

powers up only during a write cycle.

6. Power-down capability. When powered down, the DAC

typically consumes 50 nA at 3 V and 200 nA at 5 V.

1 Patent pending; protected by U.S. Patent No. 5684481.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

Fax: 781.461.3113 ©2003–2010 Analog Devices, Inc. All rights reserved.

1 page

AD5300

TERMINOLOGY

Relative Accuracy

For the DAC, relative accuracy or integral nonlinearity (INL) is

a measure of the maximum deviation, in LSBs, from a straight line

passing through the endpoints of the DAC transfer function. A

typical INL vs. code plot can be seen in Figure 2.

Differential Nonlinearity

Differential nonlinearity (DNL) is the difference between the

measured change and the ideal 1 LSB change between any two

adjacent codes. A specified differential nonlinearity of ± 1 LSB

maximum ensures monotonicity. This DAC is guaranteed

monotonic by design. A typical DNL vs. code plot can be seen

in Figure 3.

Zero-Code Error

Zero-code error is a measure of the output error when zero code

(00 Hex) is loaded to the DAC register. Ideally, the output

should be 0 V. The zero-code error is always positive in the

AD5300 because the output of the DAC cannot go below 0 V.

This is due to a combination of the offset errors in the DAC

and output amplifier. Zero-code error is expressed in LSBs. A

plot of zero-code error vs. temperature can be seen in Figure 6.

Full-Scale Error

Full-scale error is a measure of the output error when full-

scale code (FF Hex) is loaded to the DAC register. Ideally,

the output should be VDD – 1 LSB. Full-scale error is expressed

in LSBs. A plot of full-scale error vs. temperature can be

seen in Figure 6.

Gain Error

This is a measure of the span error of the DAC. It is the devia-

tion in slope of the DAC transfer characteristic from ideal

expressed as a percent of the full-scale range.

Total Unadjusted Error

Total unadjusted error (TUE) is a measure of the output error

taking into account all the various errors. A typical TUE vs.

code plot can be seen in Figure 4.

Zero-Code Error Drift

This is a measure of the change in zero-code error with a

change in temperature. It is expressed in µV/°C.

Gain Error Drift

This is a measure of the change in gain error with changes in

temperature. It is expressed in (ppm of full-scale range)/°C.

Digital-to-Analog Glitch Impulse

Digital-to-analog glitch impulse is the impulse injected into the

analog output when the input code in the DAC register changes

state. It is normally specified as the area of the glitch in nV-secs

and is measured when the digital input code is changed by

1 LSB at the major carry transition (7F Hex to 80 Hex). See

Figure 19.

Digital Feedthrough

Digital feedthrough is a measure of the impulse injected into the

analog output of the DAC from the digital inputs of the DAC

but is measured when the DAC output is not updated. It is

specified in nV-secs and is measured with a full-scale code

change on the data bus, i.e., from all 0s to all 1s, and vice versa.

REV. D

–5–

5 Page

AD5300

R2 = 10k⍀

+5V

+5V R1 = 10k⍀

10F

VDD

VOUT

0.1F

AD5300

AD820/

OP295

–5V

؎5V

3-WIRE

SERIAL

INTERFACE

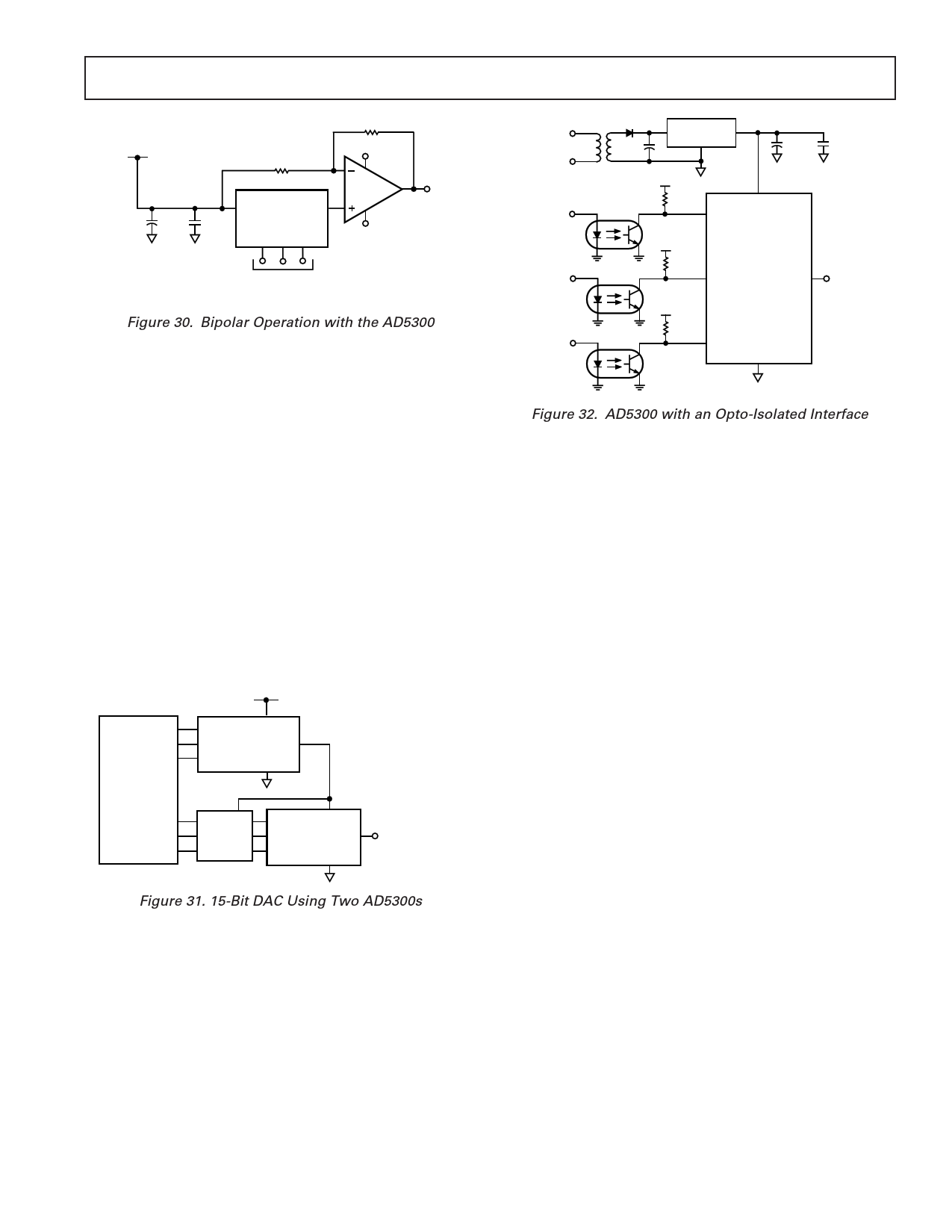

Figure 30. Bipolar Operation with the AD5300

Two 8-Bit AD5300s Together Make One 15-Bit DAC

By using the configuration in Figure 31, it can be seen that one

15-bit DAC can be made with two 8-bit AD5300s. Because of

the low supply current the AD5300 requires, the output of one

DAC may be directed into the supply pin of the second DAC.

The first DAC has no problem sourcing the required 140 µA

of current for the second DAC.

Since the AD5300 works on any supply voltage between 2.5 V

and 5.5 V, the output of the first DAC can be anywhere above

2.5 V. For a VDD of 5 V, this allows the first DAC to use half of

its output range (2.5 V to 5 V), which gives 7-bit resolution on

the output voltage. This output then becomes the supply and

reference for the second DAC. The second DAC has 8-bit reso-

lution on the output range, which gives an overall resolution for

the system of 15 bits.

A level-shifter is required to ensure that the logic input voltages

do not exceed the supply voltage of the part. The microcontroller

outputs 5 V signals, which need to be level shifted down to 2.5 V

in the case of the second DAC having a supply of only 2.5 V.

MICRO-

CONTROLLER

5V

SYNC

SCLK

DIN

VDD

AD5300

VOUT = 2.5V TO 5V

LEVEL

SHIFTER

SYNC

SCLK

DIN

VDD

AD5300

VOUT = 0V TO 5V

15-BIT

RESOLUTION

Figure 31. 15-Bit DAC Using Two AD5300s

Using AD5300 with an Opto-Isolated Interface

In process-control applications in industrial environments, it is

often necessary to use an opto-isolated interface to protect and

isolate the controlling circuitry from any hazardous common-

mode voltages that may occur in the area where the DAC is

functioning. Opto-isolators provide isolation in excess of 3 kV.

Because the AD5300 uses a 3-wire serial logic interface, it

requires only three opto-isolators to provide the required isola-

tion (see Figure 32). The power supply to the part also needs to

be isolated. This is done by using a transformer. On the DAC

side of the transformer, a 5 V regulator provides the 5 V supply

required for the AD5300.

POWER

SCLK

SYNC

DATA

5V

REGULATOR

10F

0.1F

VDD

10k⍀

VDD

SCLK

VDD

10k⍀

AD5300

SYNC

VOUT

VDD

10k⍀

DIN

GND

Figure 32. AD5300 with an Opto-Isolated Interface

Power Supply Bypassing and Grounding

When accuracy is important in a circuit, it is helpful to carefully

consider the power supply and ground return layout on the

board. The printed circuit board containing the AD5300 should

have separate analog and digital sections, each having its own

area of the board. If the AD5300 is in a system where other

devices require an AGND to DGND connection, the connec-

tion should be made at one point only. This ground point should

be as close as possible to the AD5300.

The power supply to the AD5300 should be bypassed with

10 µF and 0.1 µF capacitors. The capacitors should be physi-

cally as close as possible to the device with the 0.1 µF capacitor

ideally right up against the device. The 10 µF capacitors are the

tantalum bead type. It is important that the 0.1 µF capacitor

has low effective series resistance (ESR) and effective series

inductance (ESI), e.g., common ceramic types of capacitors. This

0.1 µF capacitor provides a low impedance path to ground for

high frequencies caused by transient currents due to internal

logic switching.

The power supply line itself should have as large a trace as pos-

sible to provide a low impedance path and reduce glitch effects

on the supply line. Clocks and other fast switching digital signals

should be shielded from other parts of the board by digital

ground. Avoid crossover of digital and analog signals if possible.

When traces cross on opposite sides of the board, ensure that

they run at right angles to each other to reduce feedthrough

effects through the board. The best board layout technique is

the microstrip technique where the component side of the board

is dedicated to the ground plane only and the signal traces are

placed on the solder side. However, this is not always possible

with a 2-layer board.

REV. D

–11–

11 Page | ||

| Páginas | Total 13 Páginas | |

| PDF Descargar | [ Datasheet AD5300.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AD530 | Integrated Circuit / Multiplier / Divider / Square Rooter | Analog Devices |

| AD5300 | 8-Bit DAC | Analog Devices |

| AD5301 | +2.5 V to +5.5 V/ 120 uA/ 2-Wire Interface/ Voltage Output 8-/10-/12-Bit DACs | Analog Devices |

| AD5302 | +2.5 V to +5.5 V/ 230 uA Dual Rail-to-Rail/ Voltage Output 8-/10-/12-Bit DACs | Analog Devices |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |