|

|

PDF AD7303 Data sheet ( Hoja de datos )

| Número de pieza | AD7303 | |

| Descripción | +2.7 V to +5.5 V/ Serial Input/ Dual Voltage Output 8-Bit DAC | |

| Fabricantes | Analog Devices | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AD7303 (archivo pdf) en la parte inferior de esta página. Total 16 Páginas | ||

|

No Preview Available !

a

FEATURES

Two 8-Bit DACs in One Package

8-Pin DIP/SOIC and microSOIC Packages

+2.7 V to +5.5 V Operation

Internal & External Reference Capability

Individual DAC Power-Down Function

Three-Wire Serial Interface

QSPI™, SPI™ and Microwire™ Compatible

On-Chip Output Buffer

Rail-to-Rail Operation

On-Chip Control Register

Low Power Operation: 2.3 mA @ 3.3 V

Full Power-Down to 1 A max, typically 80 nA

APPLICATIONS

Portable Battery Powered Instruments

Digital Gain and Offset Adjustment

Programmable Voltage and Current Sources

Programmable Attenuators

+2.7 V to +5.5 V, Serial Input, Dual

Voltage Output 8-Bit DAC

AD7303

FUNCTIONAL BLOCK DIAGRAM

AD7303

INPUT

REGISTER

DAC

REGISTER

I DAC A I/V

VOUT A

DIN

SCLK

SYNC

INPUT

REGISTER

DAC

REGISTER

I DAC B I/V

VOUT B

DATA (8)

CONTROL (8)

16-BIT SHIFT REGISTER

GND

MUX

POWER ON

RESET

÷2

REF

VDD

GENERAL DESCRIPTION

The AD7303 is a dual, 8-bit voltage out DAC that operates

from a single +2.7 V to +5.5 V supply. Its on-chip precision out-

put buffers allow the DAC outputs to swing rail to rail. This de-

vice uses a versatile 3-wire serial interface that operates at clock

rates up to 30 MHz, and is compatible with QSPI, SPI, microwire

and digital signal processor interface standards. The serial input

register is sixteen bits wide; 8 bits act as data bits for the DACs,

and the remaining eight bits make up a control register.

The on-chip control register is used to address the relevant

DAC, to power down the complete device or an individual

DAC, to select internal or external reference and to provide a

synchronous loading facility for simultaneous update of the

DAC outputs with a software LDAC function.

The low power consumption of this part makes it ideally suited

to portable battery operated equipment. The power consump-

tion is 7.5 mW max at 3 V, reducing to less than 3 µW in full

power-down mode.

The AD7303 is available in an 8-pin plastic dual in-line pack-

age, 8-lead SOIC and microSOIC packages.

QSPI and SPI are trademarks of Motorola.

Microwire is a trademark of National Semiconductor.

PRODUCT HIGHLIGHTS

1. Low power, single supply operation. This part operates from

a single +2.7 V to +5.5 V supply and consumes typically

15 mW at 5.5 V, making it ideal for battery powered

applications.

2. The on-chip output buffer amplifiers allow the outputs of the

DACs to swing rail to rail with a settling time of typically 1.2 µs.

3. Internal or external reference capability.

4. High speed serial interface with clock rates up to 30 MHz.

5. Individual power-down of each DAC provided. When com-

pletely powered down, the DAC consumes typically 80 nA.

REV. 0

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 617/329-4700

World Wide Web Site: http://www.analog.com

Fax: 617/326-8703

© Analog Devices, Inc., 1997

1 page

AD7303

TERMINOLOGY

INTEGRAL NONLINEARITY

For the DACs, relative accuracy or endpoint nonlinearity is a

measure of the maximum deviation, in LSBs, from a straight

line passing through the endpoints of the DAC transfer func-

tion. A graphical representation of the transfer curve is shown

in Figure 15.

DIGITAL-TO-ANALOG GLITCH IMPULSE

Digital-to-analog glitch impulse is the impulse injected into the

analog output when the digital inputs change state with the

DAC selected and the software LDAC used to update the DAC.

It is normally specified as the area of the glitch in nV-s and is

measured when the digital input code is changed by 1 LSB at

the major carry transition.

DIFFERENTIAL NONLINEARITY

Differential nonlinearity is the difference between the measured

change and the ideal 1 LSB change of any two adjacent codes. A

specified differential nonlinearity of ± 1 LSB maximum ensures

monotonicity.

ZERO CODE ERROR

Zero code error is the measured output voltage from VOUT of

either DAC when zero code (all zeros) is loaded to the DAC

latch. It is due to a combination of the offset errors in the DAC

and output amplifier. Zero-scale error is expressed in LSBs.

DIGITAL FEEDTHROUGH

Digital feedthrough is a measure of the impulse injected into the

analog output of a DAC from the digital inputs of the same

DAC, but is measured when the DAC is not updated. It is

specified in nV-s and measured with a full-scale code change on

the data bus, i.e., from all 0s to all 1s and vice versa.

DIGITAL CROSSTALK

Digital crosstalk is the glitch impulse transferred to the output

of one converter due to a digital code change to another DAC.

It is specified in nV-s.

GAIN ERROR

This is a measure of the span error of the DAC. It is the devia-

tion in slope of the DAC transfer characteristic from ideal

expressed as a percent of the full-scale value. Gain error is calcu-

lated between Codes 15 and 245.

FULL-SCALE ERROR

Full-Scale Error is a measure of the output error when the DAC

latch is loaded with FF Hex. Full-scale error includes the offset

error.

ANALOG CROSSTALK

Analog crosstalk is a change in output of any DAC in response

to a change in the output of the other DAC. It is measured in

LSBs.

POWER SUPPLY REJECTION RATIO (PSRR)

This specification indicates how the output of the DAC is

affected by changes in the power supply voltage. Power supply

rejection ratio is quoted in terms of % change in output per %

of change in VDD for full-scale output of the DAC. VDD is varied

± 10%. This specification applies to an external reference only

because the output voltage will track the VDD voltage when in-

ternal reference is selected.

REV. 0

–5–

5 Page

AD7303

POWER-ON RESET

The AD7303 has a power-on reset circuit designed to allow output

stability during power-up. This circuit holds the DACs in a reset

state until a write takes place to the DAC. In the reset state all zeros

are latched into the input registers of each DAC, and the DAC reg-

isters are in transparent mode. Thus the output of both DACs are

held at ground potential until a write takes place to the DAC.

POWER-DOWN FEATURES

Two bits in the control section of the 16-bit input word are used to

put the AD7303 into low power mode. DAC A and DAC B can be

powered down separately. When both DACs are powered down,

the current consumption of the device is reduced to less than 1 µA,

making the device suitable for use in portable battery powered

equipment. The reference bias servo loop, the output amplifiers

and associated linear circuitry are all shut down when the power-

down is activated. The output sees a load of approximately 23 kΩ

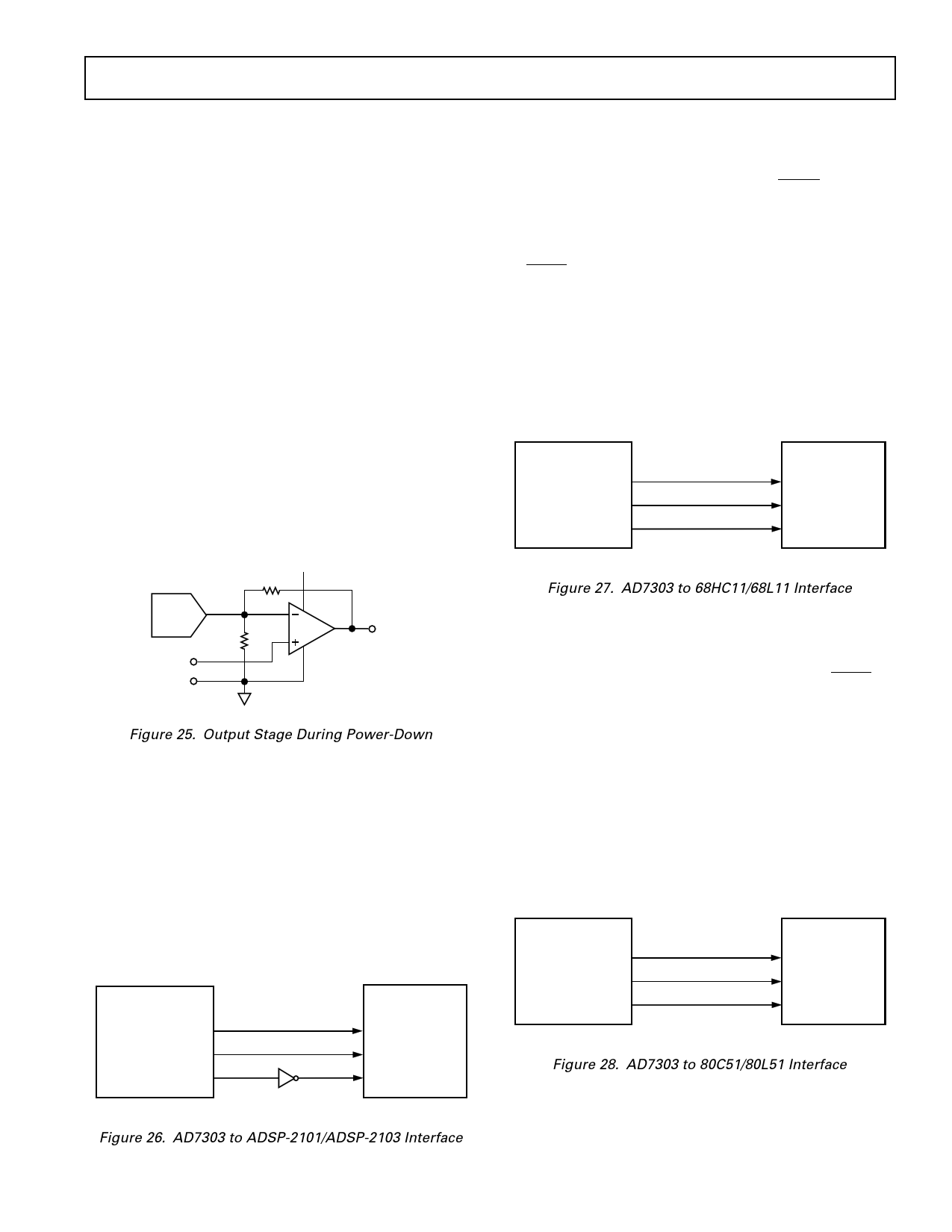

to GND when in power-down mode as shown in Figure 25. The

contents of the data registers are unaffected when in power-down

mode. The time to exit power-down is determined by the nature of

the power-down, if the device is fully powered down the bias gen-

erator is also powered down and the device takes typically 13 µs to

exit power-down mode. If the device is only partially powered

down, i.e., only one channel powered down, in this case the bias

generator is active and the time required for the power-down chan-

nel to exit this mode is typically 1.6 µs. See Figures 11 and 12.

VDD

11.7kΩ

IDAC

VREF

11.7kΩ

VO A/B

Figure 25. Output Stage During Power-Down

MICROPROCESSOR INTERFACING

AD7303 to ADSP-2101/ADSP-2103 Interface

Figure 26 shows a serial interface between the AD7303 and the

ADSP-2101/ADSP-2103. The ADSP-2101/ADSP-2103 should

be set up to operate in the SPORT Transmit Alternate Framing

Mode. The ADSP-2101/ADSP-2103 SPORT is programmed

through the SPORT control register and should be configured

as follows: Internal Clock Operation, Active Low Framing,

16-Bit Word Length. Transmission is initiated by writing a word

to the Tx register after the SPORT has been enabled. The data

is clocked out on each falling edge of the serial clock and clocked

into the AD7303 on the rising edge of the SCLK.

ADSP-2101/

ADSP-2103*

TFS

DT

SCLK

AD7303*

SYNC

DIN

SCLK

AD7303 to 68HC11/68L11 Interface

Figure 27 shows a serial interface between the AD7303 and the

68HC11/68L11 microcontroller. SCK of the 68HC11/68L11

drives the CLKIN of the AD7303, while the MOSI output

drives the serial data line of the DAC. The SYNC signal is

derived from a port line (PC7). The setup conditions for cor-

rect operation of this interface are as follows: the 68HC11/

68L11 should be configured so that its CPOL bit is a 0 and its

CPHA bit is a 0. When data is being transmitted to the DAC,

the SYNC line is taken low (PC7). When the 68HC11/68L11 is

configured as above, data appearing on the MOSI output is

valid on the rising edge of SCK. Serial data from the 68HC11/

68L11 is transmitted in 8-bit bytes with only eight falling clock

edges occurring in the transmit cycle. Data is transmitted MSB

first. In order to load data to the AD7303, PC7 is left low after

the first eight bits are transferred, and a second serial write op-

eration is performed to the DAC and PC7 is taken high at the

end of this procedure.

68HC11/68L11*

PC7

SCK

MOSI

AD7303*

SYNC

SCLK

DIN

*ADDITIONAL PINS OMITTED FOR CLARITY

Figure 27. AD7303 to 68HC11/68L11 Interface

AD7303 to 80C51/80L51 Interface

Figure 28 shows a serial interface between the AD7303 and the

80C51/80L51 microcontroller. The setup for the interface is as

follows: TXD of the 80C51/80L51 drives SCLK of the AD7303,

while RXD drives the serial data line of the part. The SYNC

signal is again derived from a bit programmable pin on the port.

In this case port line P3.3 is used. When data is to be transmit-

ted to the AD7303, P3.3 is taken low. The 80C51/80L51 trans-

mits data only in 8-bit bytes; thus only eight falling clock edges

occur in the transmit cycle. To load data to the DAC, P3.3 is

left low after the first eight bits are transmitted, and a second

write cycle is initiated to transmit the second byte of data. P3.3

is taken high following the completion of this cycle. The 80C51/

80L51 outputs the serial data in a format which has the LSB

first. The AD7303 requires its data with the MSB as the first bit

received. The 80C51/80L51 transmit routine should take this

into account.

80C51/80L51*

P3.3

TXD

RXD

AD7303*

SYNC

SCLK

SDIN

*ADDITIONAL PINS OMITTED FOR CLARITY

Figure 28. AD7303 to 80C51/80L51 Interface

*ADDITIONAL PINS OMITTED FOR CLARITY

Figure 26. AD7303 to ADSP-2101/ADSP-2103 Interface

REV. 0

–11–

11 Page | ||

| Páginas | Total 16 Páginas | |

| PDF Descargar | [ Datasheet AD7303.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AD7302 | 2.7 V to 5.5 V/ Parallel Input Dual Voltage Output 8-Bit DAC | Analog Devices |

| AD7303 | +2.7 V to +5.5 V/ Serial Input/ Dual Voltage Output 8-Bit DAC | Analog Devices |

| AD7304 | +3 V/+5 V/ Rail-to-Rail Quad/ 8-Bit DAC | Analog Devices |

| AD7305 | +3 V/+5 V/ Rail-to-Rail Quad/ 8-Bit DAC | Analog Devices |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |