|

|

PDF AD652 Data sheet ( Hoja de datos )

| Número de pieza | AD652 | |

| Descripción | Monolithic Synchronous Voltage-to-Frequency Converter | |

| Fabricantes | Analog Devices | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AD652 (archivo pdf) en la parte inferior de esta página. Total 16 Páginas | ||

|

No Preview Available !

a

FEATURES

Full-Scale Frequency (Up to 2 MHz) Set by External

System Clock

Extremely Low Linearity Error (0.005% max at 1 MHz

FS, 0.02% max at 2 MHz FS)

No Critical External Components Required

Accurate 5 V Reference Voltage

Low Drift (25 ppm/؇C max)

Dual or Single Supply Operation

Voltage or Current Input

MIL-STD-883 Compliant Versions Available

Monolithic Synchronous

Voltage-to-Frequency Converter

AD652

FUNCTIONAL BLOCK DIAGRAM

PRODUCT DESCRIPTION

The AD652 Synchronous Voltage-to-Frequency Converter

(SVFC) is a powerful building block for precision analog-to-

digital conversion, offering typical nonlinearity of 0.002%

(0.005% maximum) at a 100 kHz output frequency. The inher-

ent monotonicity of the transfer function and wide range of

clock frequencies allows the conversion time and resolution to

be optimized for specific applications.

The AD652 uses a variation of the popular charge-balancing

technique to perform the conversion function. The AD652 uses

an external clock to define the full-scale output frequency,

rather than relying on the stability of an external capacitor. The

result is a more stable, more linear transfer function, with sig-

nificant application benefits in both single- and multichannel

systems.

Gain drift is minimized using a precision low drift reference and

low TC on-chip thin-film scaling resistors. Furthermore, the ini-

tial gain error is reduced to less than 0.5% by the use of

laser-wafer-trimming.

The analog and digital sections of the AD652 have been de-

signed to allow operation from a single-ended power source,

simplifying its use with isolated power supplies.

The AD652 is available in five performance grades. The 20-lead

PLCC packaged JP and KP grades are specified for operation

over the 0°C to +70°C commercial temperature range. The

16-lead cerdip-packaged AQ and BQ grades are specified for

operation over the –40°C to +85°C industrial temperature

range, and the AD652SQ is available for operation over the full

–55°C to +125°C extended temperature range.

PRODUCT HIGHLIGHTS

1. The use of an external clock to set the full-scale frequency

allows the AD652 to achieve linearity and stability far supe-

rior to other monolithic VFCs. By using the same clock to

drive the AD652 and (through a suitable divider) also set the

counting period, conversion accuracy is maintained indepen-

dent of variations in clock frequency.

2. The AD652 Synchronous VFC requires only a single external

component (a noncritical integrator capacitor) for operation.

3. The AD652 includes a buffered, accurate 5 V reference

which is available to the user.

4. The clock input of the AD652 is TTL and CMOS compat-

ible and can also be driven by sources referred to the negative

power supply. The flexible open-collector output stage pro-

vides sufficient current sinking capability for TTL and CMOS

logic, as well as for optical couplers and pulse transformers.

A capacitor-programmable one-shot is provided for selection

of optimum output pulse width for power reduction.

5. The AD652 can also be configured for use as a synchronous

F/V converter for isolated analog signal transmission.

6. The AD652 is available in versions compliant with MIL-

STD-883. Refer to the Analog Devices Military Products

Databook or current AD652/883B data sheet for detailed

specifications.

REV. B

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 World Wide Web Site: http://www.analog.com

Fax: 781/326-8703

© Analog Devices, Inc., 2000

1 page

there are no problems with dielectric absorption causing the

duration of a reset pulse to be influenced by the length of time

since the last reset.

AD652

finally, a whole cycle is lost. When the cycle is lost, the Integrate

Phase lasts for two periods of the clock instead of the usual three

periods. Thus, among a long string of divide-by-fours an occasional

divide-by-three occurs; the average of the output frequency is

very close to one quarter of the clock, but the instantaneous fre-

quency can be very different.

Because of this, it is very difficult to observe the waveform on an

oscilloscope. During all of this time, the signal at the output of

the integrator is a sawtooth wave with an envelope which is also

a sawtooth. This is shown in Figure 4.

Figure 2. AD652 Block Diagram and System Waveforms

Referring to Figure 2, it can be seen that the period between

output pulses is constrained to be an exact multiple of the clock

period. Consider an input current of exactly one quarter of the

value of the reference current. In order to achieve a charge bal-

ance, the output frequency will equal the clock frequency divided

by four; one clock period for reset and three clock periods of inte-

grate. This is shown in Figure 3. If the input current is increased by

a very small amount, the output frequency should also increase

by a very small amount. Initially, however, no output change is

Figure 4. Integrator Output for IIN Slightly Greater

than 250 µA

Another way to view this is that the output is a frequency of

approximately one quarter of the clock that has been phase

modulated. A constant frequency can be thought of as accumu-

lating phase linearly with time at a rate equal to 2 πf radians per

second. Hence, the average output frequency which is slightly in

excess of a quarter of the clock will require phase accumulation

at a certain rate. However, since the SVFC is running at exactly

one quarter of the clock, it will not accumulate enough phase

(see Figure 5). When the difference between the required phase

(average frequency) and the actual phase equals 2 π, a step in

phase is taken where the deficit is made up instantaneously. The

output frequency is then a steady carrier which has been phase

modulated by a sawtooth signal (see Figure 5). The period of

the sawtooth phase modulation is the time required to accumulate

a 2 π difference in phase between the required average frequency

and one quarter of the clock frequency. The amplitude of the

sawtooth phase modulation is 2 π.

Figure 3. Integrator Output for lIN = 250 µA

observed for a very small increase in the input current. The out-

put frequency continues to run at one quarter of the clock,

delivering an average of 250 µA to the summing junction. Since

the input current is slightly larger than this, charge accumulates

in the integrator and the sawtooth signal starts to drift downward.

As the integrator sawtooth drifts down, the comparator thresh-

old is crossed earlier and earlier in each successive cycle, until

REV. B

–5–

Figure 5. Phase Modulation

5 Page

AD652

This can be shown in equation form, where fC is the AD654

output frequency and fOUT is the AD652 output frequency:

fC

=

V1

1 MHz

10 V

fOUT

= V2

fC/2

10 V

fOUT

=

V1V2

1 MHz

2(10 V ) (10 V

)

f OUT = V1 •V 2 • 5 kHz/V 2

The scope photo in Figure 19 shows V1 and V2 (top two traces)

and the output of the F-V (bottom trace).

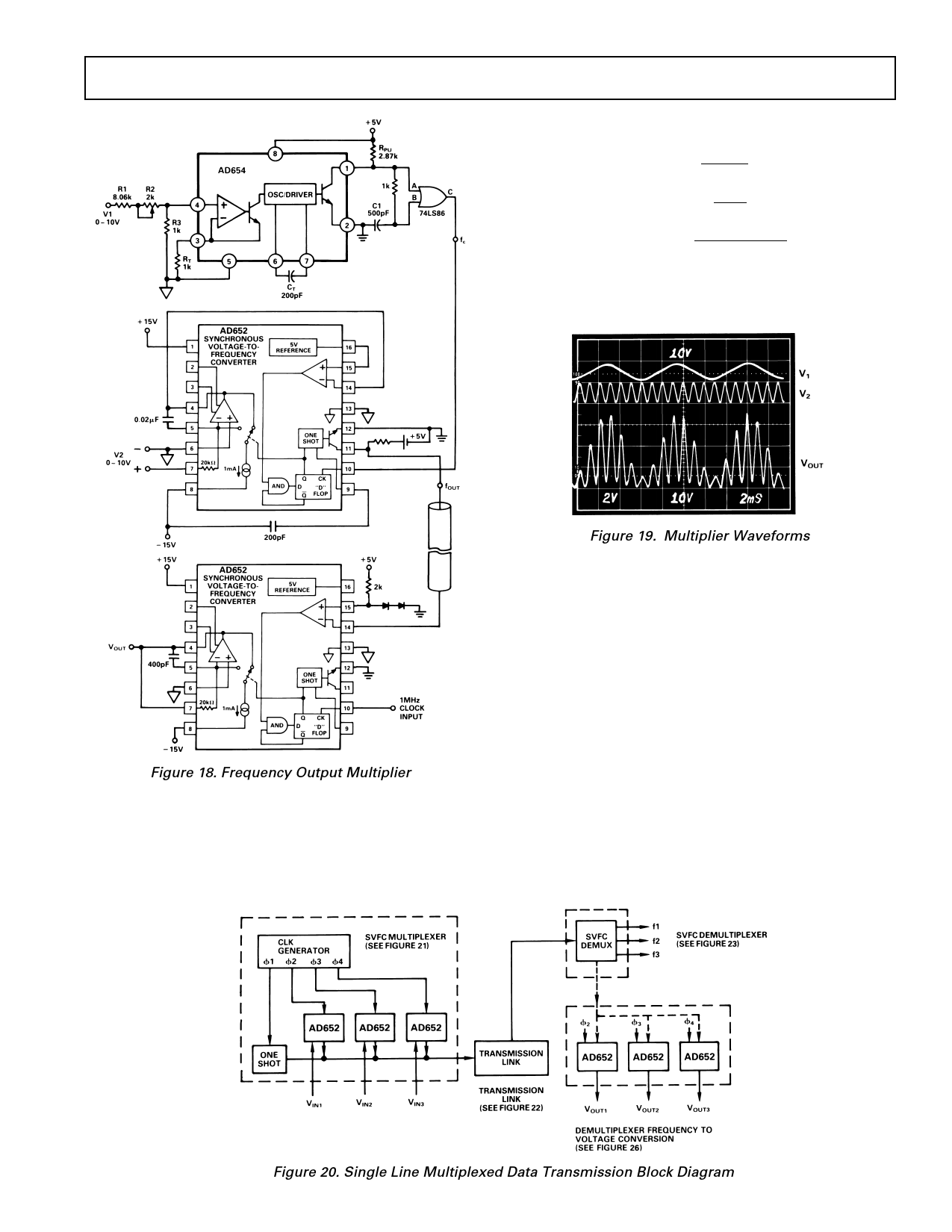

Figure 18. Frequency Output Multiplier

This 1 MHz full-scale frequency is then used as the clock input

to the AD652 SVFC. Since the AD652 full-scale output fre-

quency is one-half the clock frequency, the 1 MHz FS clock

frequency establishes a 500 kHz maximum output frequency for

the AD652 when its input voltage (V2) is +10 V. The user thus

has an output frequency range from 0 kHz–500 kHz which is

proportional to the product of V1 and V2.

Figure 19. Multiplier Waveforms

SINGLE-LINE MULTIPLEXED DATA TRANSMISSION

It is often necessary to measure several different signals and relay

the information to some remote location using a minimum

amount of cable. Multiple AD652 SVFC devices may be used

with a multiphase clock to combine these measurements for

serial transmission and demultiplexing. Figure 20 shows a block

diagram of a single-line multiplexed data transmission system

with high noise immunity. Figures 21, 22 and 23 show the SVFC

multiplexer, a representative means of data transmission, and an

SVFC demultiplexer respectively.

Multiplexer

Figure 21 shows the SVFC multiplexer. The clock inputs for the

several SVFC channels are generated by a TIM9904A four phase

clock driver, and the frequency outputs are combined by strapping

all the frequency output pins together (a “wire or” connection).

The one-shot in the AD652 sets the pulse width of the frequency

output pulses to be slightly shorter than one quarter of the clock

period. Synchronization is achieved by applying one of the four

available phases to a fixed TTL one-shot (’121) and combining

REV. B

Figure 20. Single Line Multiplexed Data Transmission Block Diagram

–11–

11 Page | ||

| Páginas | Total 16 Páginas | |

| PDF Descargar | [ Datasheet AD652.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AD650 | Voltage-to-Frequency and Frequency-to-Voltage Converter | Analog Devices |

| AD651 | Monolithic Synchronous Voltage to Frequency Converter | Analog Devices |

| AD652 | Monolithic Synchronous Voltage-to-Frequency Converter | Analog Devices |

| AD6528 | GSM/GPRS Digital Baseband Processor | Analog Devices |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |