|

|

PDF AD7946 Data sheet ( Hoja de datos )

| Número de pieza | AD7946 | |

| Descripción | 14-Bit/ 500 kSPS PulSAR ADC in MSOP/QFN | |

| Fabricantes | Analog Devices | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AD7946 (archivo pdf) en la parte inferior de esta página. Total 27 Páginas | ||

|

No Preview Available !

Preliminary Technical Data

FEATURES

14-bit resolution with no missing codes

Throughput: 500 kSPS

INL: ±0.4 LSB typ, ±1 LSB max (±0.0061 % of FSR)

S/(N + D): 85 dB @ 20 kHz

THD: −100 dB @ 20 kHz

Pseudo-differential analog input range

0 V to VREF with VREF up to VDD

No pipeline delay

Single-supply 5V operation with

1.8 V/2.5 V/3 V/5 V logic interface

Serial interface SPI®/QSPI™/µWire/DSP compatible

Daisy chain multiple ADCs and BUSY indicator

Power dissipation

3.3 mW @ 5 V/100 kSPS,

3.3 µW @ 5 V/100 SPS

Stand-by current: 1 nA

10-lead package: MSOP (MSOP-8 size) and

QFN (LFCSP), 3 mm × 3 mm same space as SOT-23

Pin-for-pin compatible with the 16-Bit AD7686

APPLICATIONS

Battery-powered equipment

Data acquisition

Instrumentation

Medical instruments

Process control

Table 1. MSOP, QFN (LFCSP)/SOT-23 14 and16-Bit ADC

Type

100 kSPS 250 kSPS 500 kSPS

16-Bit True

Differential

AD7684

AD7687

AD7688

16-Bit Pseudo

AD7683

Differential/Unipolar

AD7685

AD7694

AD7686

16-Bit Unipolar

AD7680

14-Bit Pseudo

Differential/Unipolar

AD7942 AD7946

14-Bit Unipolar

AD7940

14-Bit, 500 kSPS PulSAR™

ADC in MSOP/QFN

AD7946

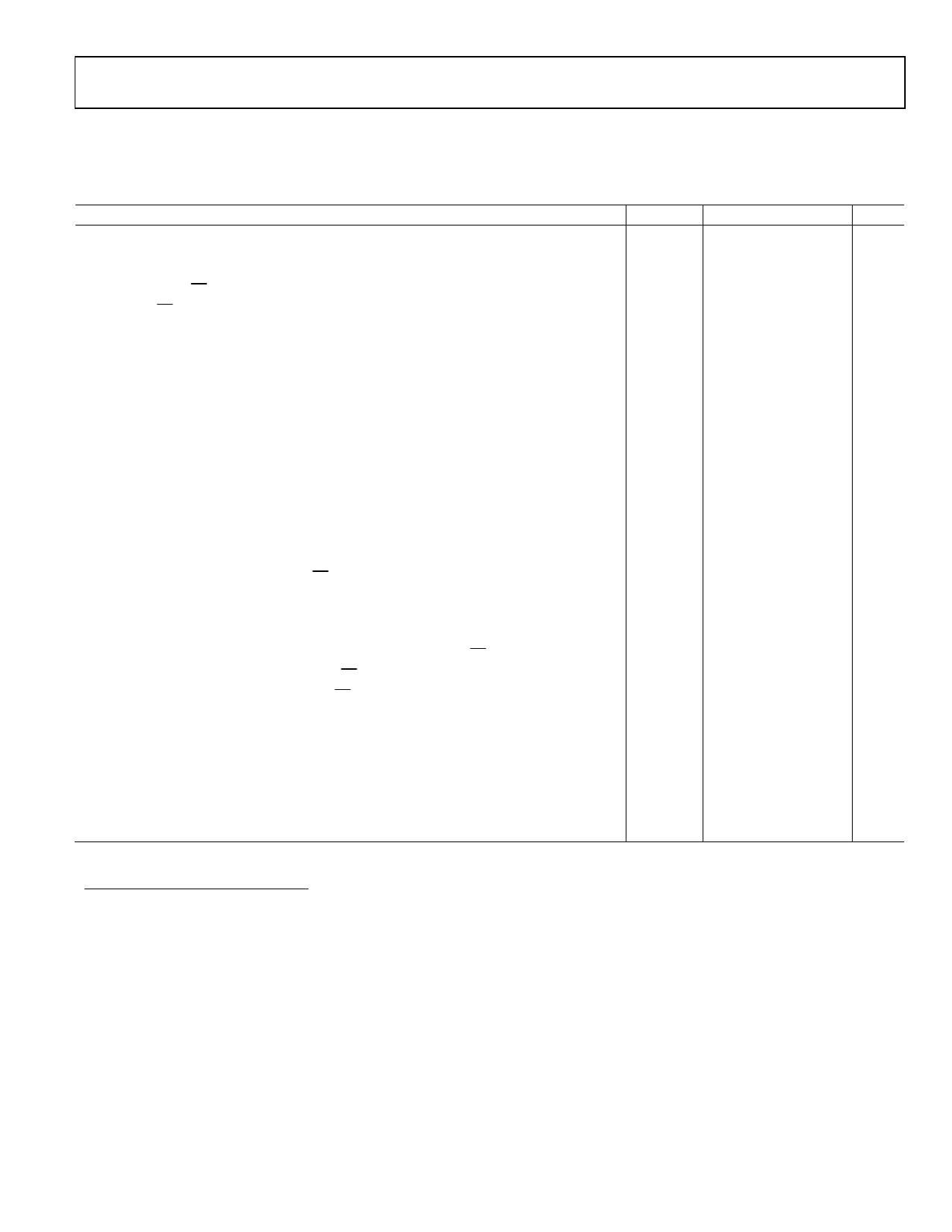

APPLICATION DIAGRAM

0.5 TO 5V 5V

0 TO VREF

REF VDD VIO

SDI

IN+

AD7946 SCK

IN– SDO

GND

CNV

1.8 TO VDD

3- OR 4-WIRE INTERFACE

(SPI, DAISY CHAIN, CS)

Figure 1.

GENERAL DESCRIPTION

The AD7946 is a 14-bit, charge redistribution successive

approximation, analog-to-digital converter (ADC) that operates

from a single 5V power supply, VDD. It contains a low power,

high speed, 14-bit sampling ADC with no missing codes, an

internal conversion clock, and a versatile serial interface port.

The part also contains a low noise, wide bandwidth, short

aperture delay track-and-hold circuit. On the CNV rising edge,

it samples an analog input IN+ between 0 V to REF with respect

to a ground sense IN−. The reference voltage, REF, is applied

externally and can be set up to the supply voltage.

Its power scales linearly with throughput.

The SPI compatible serial interface also features the ability,

using the SDI input, to daisy chain several ADCs on a single 3-

wire bus and provides an optional BUSY indicator. It is

compatible with 1.8 V, 2.5 V, 3 V, or 5 V logic using the separate

supply VIO.

The AD7946 is housed in a 10-lead MSOP or a 10-lead QFN

(LFCSP) with operation specified from −40°C to +85°C.

Rev Pr D

Information furnished by Analog Devices is believed to be accurate and reliable.

However, no responsibility is assumed by Analog Devices for its use, nor for any

infringements of patents or other rights of third parties that may result from its use.

Specifications subject to change without notice. No license is granted by implication

or otherwise under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

Fax: 781.326.8703 © 2004 Analog Devices, Inc. All rights reserved.

1 page

Preliminary Technical Data

AD7946

TIMING SPECIFICATIONS

−40°C to +85°C, VDD = 4.5 V to 5.5 V, VIO = 2.3 V to 5.5 V or VDD + 0.3 V, whichever is the lowest, unless otherwise stated.

Table 4. 1

Conversion Time: CNV Rising Edge to Data Available

Acquisition Time

Time between Conversions

CNV Pulse Width ( CS Mode )

SCK Period ( CS Mode )

SCK Period ( Chain Mode )

VIO above 4.5 V

VIO above 3 V

VIO above 2.7 V

VIO above 2.3 V

SCK Low Time

SCK High Time

SCK Falling Edge to Data Remains Valid

SCK Falling Edge to Data Valid Delay

VIO above 4.5 V

VIO above 3 V

VIO above 2.7 V

VIO above 2.3 V

CNV or SDI Low to SDO D15 MSB Valid (CS Mode)

VIO above 4.5 V

VIO above 2.7 V

VIO above 2.3 V

CNV or SDI High or Last SCK Falling Edge to SDO High Impedance (CS Mode)

SDI Valid Setup Time from CNV Rising Edge (CS Mode)

SDI Valid Hold Time from CNV Rising Edge (CS Mode)

SCK Valid Setup Time from CNV Rising Edge (Chain Mode)

SCK Valid Hold Time from CNV Rising Edge (Chain Mode)

SDI Valid Setup Time from SCK Falling Edge (Chain Mode)

SDI Valid Hold Time from SCK Falling Edge (Chain Mode)

SDI High to SDO High (Chain Mode with BUSY indicator)

VIO above 4.5 V

VIO above 2.3 V

Symbol

tCONV

tACQ

tCYC

tCNVH

tSCK

tSCK

tSCKL

tSCKH

tHSDO

tDSDO

tEN

tDIS

tSSDICNV

tHSDICNV

tSSCKCNV

tHSCKCNV

tSSDISCK

tHSDISCK

tDSDOSDI

Min Typ Max

0.5 1.6

400

2

10

15

19

20

21

22

7

7

5

14

15

16

17

15

18

22

25

15

0

5

5

5

4

15

26

Unit

µs

ns

µs

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

1 See Figure 2 and Figure 3 for load conditions.

Rev Pr D | Page 5 of 27

5 Page

Preliminary Technical Data

AD7946

Figure 17. Operating Currents vs. Temperature

Figure 19. tDSDO vs. Capacitance Load and Supply

Figure 18. Offset and Gain Error vs. Temperature

Rev Pr D | Page 11 of 27

11 Page | ||

| Páginas | Total 27 Páginas | |

| PDF Descargar | [ Datasheet AD7946.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AD7940 | 14-Bit ADC | Analog Devices |

| AD7942 | PulSAR ADC | Analog Devices |

| AD7943 | +3.3 V/+5 V Multiplying 12-Bit DACs | Analog Devices |

| AD7944 | PulSAR 15.5 mW ADC | Analog Devices |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |