|

|

PDF AD7888 Data sheet ( Hoja de datos )

| Número de pieza | AD7888 | |

| Descripción | +2.7 V to +5.25 V/ Micropower/ 8-Channel/ 125 kSPS/ 12-Bit ADC in 16-Lead TSSOP | |

| Fabricantes | Analog Devices | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AD7888 (archivo pdf) en la parte inferior de esta página. Total 16 Páginas | ||

|

No Preview Available !

a +2.7 V to +5.25 V, Micropower, 8-Channel,

125 kSPS, 12-Bit ADC in 16-Lead TSSOP

AD7888

FEATURES

Specified for VDD of +2.7 V to +5.25 V

Flexible Power/Throughput Rate Management

Shutdown Mode: 1 A Max

Eight Single-Ended Inputs

Serial Interface: SPI™/QSPI™/MICROWIRE™/DSP

Compatible

16-Lead Narrow SOIC and TSSOP Packages

APPLICATIONS

Battery-Powered Systems (Personal Digital Assistants,

Medical Instruments, Mobile Communications)

Instrumentation and Control Systems

High Speed Modems

FUNCTIONAL BLOCK DIAGRAM

AIN1

AIN8

REF IN/REF OUT

I/P

MUX

T/H

AD7888

BUF

2.5V

REF

COMP

CHARGE

REDISTRIBUTION

DAC

VDD

GENERAL DESCRIPTION

The AD7888 is a high speed, low power, 12-bit ADC that oper-

ates from a single +2.7 V to +5.25 V power supply. The AD7888

is capable of a 125 kSPS throughput rate. The input track-and-

hold acquires a signal in 500 ns and features a single-ended

sampling scheme. The AD7888 contains eight single-ended

analog inputs, AIN1 through AIN8. The analog input on each

of these channels is from 0 to VREF. The part is capable of con-

verting full power signals up to 2.5 MHz.

The AD7888 features an on-chip 2.5 V reference that can be

used as the reference source for the A/D converter. The REF

IN/REF OUT pin allows the user access to this reference. Alter-

natively, this pin can be overdriven to provide an external refer-

ence voltage for the AD7888. The voltage range for this external

reference is from 1.2 V to VDD.

CMOS construction ensures low power dissipation of typically

2 mW for normal operation and 3 µW in power-down mode.

The part is available in a 16-lead narrow body small outline

(SOIC) and a 16-lead thin shrink small outline (TSSOP) package.

AGND

SAR + ADC

CONTROL LOGIC

SPORT

AGND

CS DIN DOUT SCLK

PRODUCT HIGHLIGHTS

1. Smallest 12-bit 8-channel ADC; 16-lead TSSOP is the same

area as an 8-lead SOIC and less than half the height.

2. Lowest Power 12-bit 8-channel ADC.

3. Flexible power management options including automatic

power-down after conversion.

4. Analog input range from 0 V to VREF (VDD).

5. Versatile serial I/O port (SPI/QSPI/MICROWIRE/DSP

Compatible).

SPI and QSPI are trademarks of Motorola, Inc.

MICROWIRE is a trademark of National Semiconductor Corporation.

REV. 0

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 World Wide Web Site: http://www.analog.com

Fax: 781/326-8703

© Analog Devices, Inc., 1999

1 page

PIN CONFIGURATIONS

SOIC AND TSSOP

CS 1

16 SCLK

REF IN/REF OUT 2

15 DOUT

VDD 3

14 DIN

AGND 4 AD7888 13 AGND

AIN1

5

TOP VIEW

(Not to Scale)

12

AIN8

AIN2 6

11 AIN7

AIN3 7

10 AIN6

AIN4 8

9 AIN5

AD7888

PIN FUNCTION DESCRIPTIONS

Pin Pin

No. Mnemonic

1 CS

2 REF IN/REF OUT

3 VDD

4, 13 AGND

5–12 AIN1–AIN8

14 DIN

15 DOUT

16 SCLK

Function

Chip Select. Active low logic input. This input provides the dual function of initiating conversions on

the AD7888 and also frames the serial data transfer.

Reference Input/Output. The on-chip reference is available on this pin for use external to the AD7888.

Alternatively, the internal reference can be disabled and an external reference applied to this input.

The voltage range for the external reference is from +1.2 V to VDD.

Power Supply Input. The VDD range for the AD7888 is from +2.7 V to +5.25 V.

Analog Ground. Ground reference point for all circuitry on the AD7888. All analog input signals and

any external reference signals should be referred to this AGND voltage. Both of these pins should

connect to the AGND plane of a system.

Analog Input 1 through Analog Input 8. Eight single-ended analog input channels that are multiplexed

into the on-chip track/hold. The analog input channel to be converted is selected by using the ADD0

through ADD2 bits of the Control Register. The input range for all input channels is 0 to VREF. Any

unused input channels should be connected to AGND to avoid noise pickup.

Data In. Logic Input. Data to be written to the AD7888’s Control Register is provided on this input

and is clocked into the register on the rising edge of SCLK (see Control Register section).

Data Out. Logic Output. The conversion result from the AD7888 is provided on this output as a serial

data stream. The bits are clocked out on the falling edge of the SCLK input. The data stream consists

of four leading zeros followed by the 12 bits of conversion data, which is provided MSB first.

Serial Clock. Logic Input. SCLK provides the serial clock for accessing data from the part and writing

serial data to the Control Register. This clock input is also used as the clock source for the AD7888’s

conversion process.

REV. 0

–5–

5 Page

AD7888

CS

SCLK

THE PART REMAINS POWERED UP

AT ALL TIMES AS PM1 AND PM0 = 0

1 16

DOUT

DIN

4 LEADING ZEROES + CONVERSION RESULT

DATA IN

CONTROL REGISTER DATA IS LOADED ON THE

FIRST 8 CLOCKS. PM1 AND PM0 = 0 TO KEEP

THE PART IN THIS MODE

Figure 13. Normal-Mode Operation

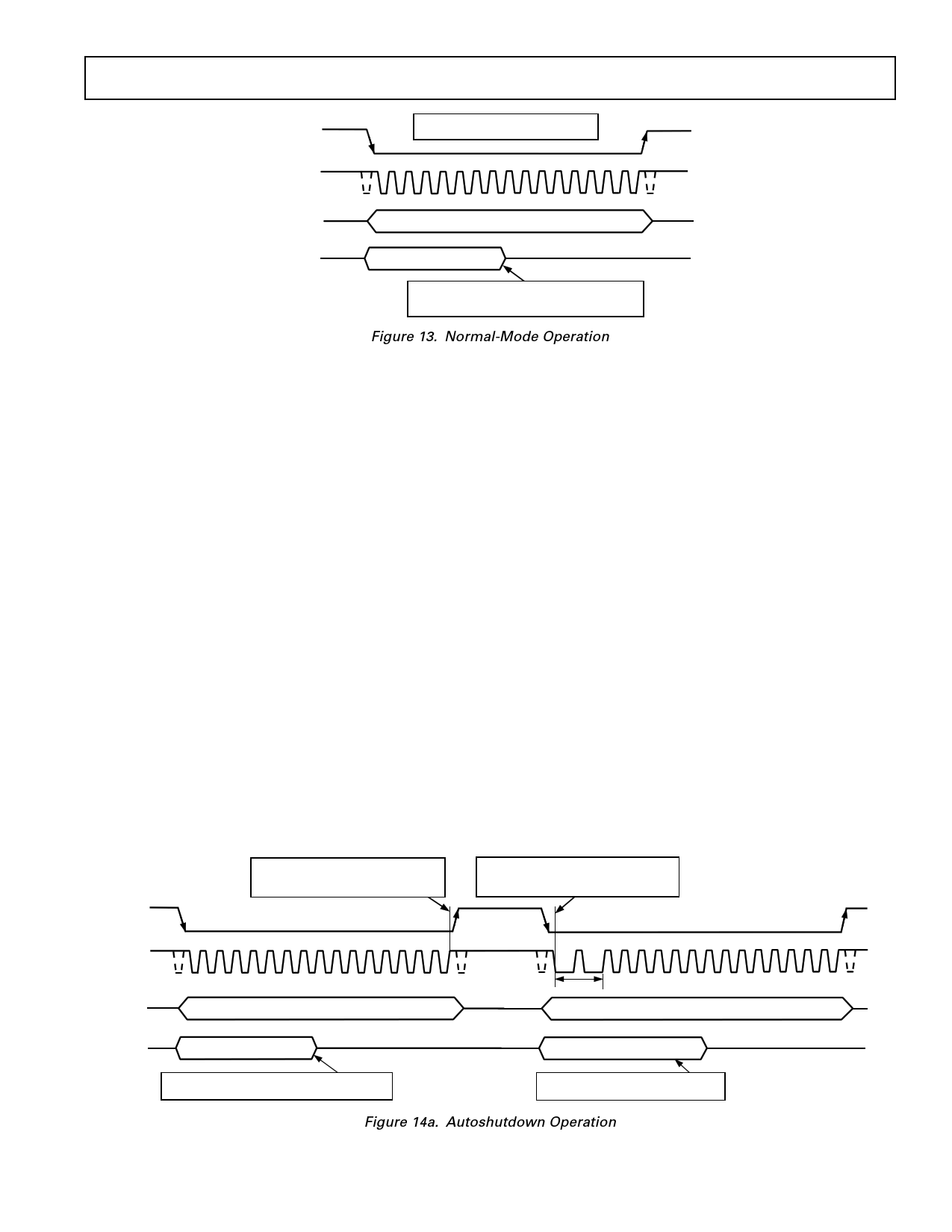

MODES OF OPERATION

The AD7888 has a number of different modes of operation.

These are designed to provide flexible power management

options. These options can be chosen to optimize the power

dissipation/throughput rate ratio for differing application re-

quirements. The modes of operation are controlled by the PM1

and PM0 bits of the Control Register as outlined previously.

Normal Mode (PM1 = 0, PM0 = 0)

This mode is intended for fastest throughput rate performance

as the user does not have to worry about any power-up times

with the AD7888 remaining fully powered all the time. Figure

13 shows the general diagram of the operation of the AD7888 in

this mode.

The data presented to the AD7888 on the DIN line during the

first eight clock cycles of the data transfer are loaded to the

Control Register. The part will remain powered up at the end of

the conversion as long as PM1 and PM0 were set to zero in the

write during that conversion. To continue to operate in this

mode, the user must ensure that PM1 and PM0 are both loaded

with 0 on every data transfer.

The falling edge of CS initiates the sequence and the input

signal is sampled on the second rising edge of the SCLK input.

Sixteen serial clock cycles are required to complete the conver-

sion and access the conversion result. Once a data transfer is

complete (CS has returned high), another conversion can be

initiated immediately by bringing CS low again.

Full Shutdown (PM1 = 0, PM0 = 1)

In this mode, all internal circuitry on the AD7888, including the

on-chip reference, is powered-down. The part retains the infor-

mation in the Control Register during full shutdown. The part

remains in full shutdown until the power management bits are

changed. If the power management bits are changed to PM1 = 1

and PM0 = 0, i.e., the autoshutdown mode, the part will remain

in shutdown (now in autoshutdown) but will power up once a

conversion is initiated after that (see Power-Up Times section).

The part changes mode as soon as the control register has been

updated, so if the part is in full shutdown mode and the power

management bits are changed to PM1 = PM0 = 0, i.e., normal

mode, then the part will power up on the 16th SCLK rising edge.

Autoshutdown (PM1 = 1, PM0 = 0)

In this mode, the AD7888 automatically enters its power-down

mode at the end of every conversion. Figure 14a shows the

general diagram of the operation of the AD7888 in this mode.

When CS goes from high to low, all on-chip circuitry will start

to power up on the next falling edge of SCLK. On the sixteenth

SCLK rising edge the part will power down again. It takes ap-

proximately 5 µs for the AD7888 internal circuitry to be fully

powered up. As a result, a conversion (or sample-and-hold

acquisition) should not be initiated during this 5 µs. The input

signal is sampled on the second rising edge of SCLK following

the CS falling edge. The user should ensure that 5 µs elapse

between the first falling edge of SCLK after the falling edge of

CS

SCLK

DOUT

THE PART ENTERS

SHUTDOWN AT THE END OF

CONVERSION AS PM1 = 1 AND PM0 = 0

THE PART POWERS UP FROM

SHUTDOWN ON SCLK FALLING EDGE AS

PM1 = 1 AND PM0 = 0

1 16

4 LEADING ZEROES + CONVERSION RESULT

12

16

t10 = 5s

4 LEADING ZEROES + CONVERSION RESULT

DIN DATA IN

DATA IN

CONTROL REGISTER DATA IS LOADED ON THE

FIRST 8 CLOCKS. PM1 = 1 AND PM0 = 0

PM1 = 1 AND PM0 = 0 TO KEEP THE

PART IN THIS MODE

Figure 14a. Autoshutdown Operation

REV. 0

–11–

11 Page | ||

| Páginas | Total 16 Páginas | |

| PDF Descargar | [ Datasheet AD7888.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AD7880 | LC2MOS Single +5 V Supply/ Low Power/ 12-Bit Sampling ADC | Analog Devices |

| AD7883 | LC2MOS 12-Bit/ 3.3 V Sampling ADC | Analog Devices |

| AD7884 | LC2MOS 16-Bit/ High Speed Sampling ADCs | Analog Devices |

| AD7885 | LC2MOS 16-Bit/ High Speed Sampling ADCs | Analog Devices |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |