|

|

PDF ADS7870 Data sheet ( Hoja de datos )

| Número de pieza | ADS7870 | |

| Descripción | 12-Bit ADC/ MUX/ PGA and Internal Reference DATA ACQUISITION SYSTEM | |

| Fabricantes | Burr-Brown Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ADS7870 (archivo pdf) en la parte inferior de esta página. Total 27 Páginas | ||

|

No Preview Available !

®

ADS7870

ADS7870

For most current data sheet and other product

information, visit www.burr-brown.com

12-Bit ADC, MUX, PGA and Internal Reference

DATA ACQUISITION SYSTEM

FEATURES

q 16-BIT DYNAMIC RANGE

q PGA GAINS: 1, 2, 4, 5, 8, 10, 16, 20V/V

q 4-CHANNEL DIFFERENTIAL/8-CHANNEL

SINGLE ENDED MULTIPLEXER

q 2.048V OR 2.5V INTERNAL REFERENCE

q FAST SERIAL INTERFACE

q HIGH THROUGHPUT RATE: 52ksamples/s

q ERROR/OVERLOAD INDICATOR

q 2.7V TO 5.5V SINGLE-SUPPLY OPERATION

q 4-BIT DIGITAL I/O VIA SERIAL INTERFACE

q SSOP-28 PACKAGE

DESCRIPTION

The ADS7870(1) is a complete low-power data acquisi-

tion system on a single chip. It consists of a 4-channel

differential/8-channel single-ended multiplexer, preci-

sion programmable gain amplifier, 12-bit successive

approximation analog-to-digital converter and a preci-

sion voltage reference.

The programmable-gain amplifier provides high input

impedance, excellent gain accuracy, good common-

mode rejection, and low noise.

For many low-level signals, no external amplification or

impedance buffering is needed between the signal

source and the A/D input.

APPLICATIONS

q PORTABLE/BATTERY POWERED

SYSTEMS

q LOW POWER INSTRUMENTATION

q LOW POWER CONTROL SYSTEMS

q SMART SENSOR APPLICATIONS

The offset voltage of the PGA is auto zeroed. Gains of

1, 2, 4, 5, 8, 10, 16 and 20V/V provide 16-bit dynamic

range and allow signals as low as 125mV to produce full

scale digital outputs.

The ADS7870 contains an internal reference, which is

trimmed for high initial accuracy and stability vs tem-

perature. Drift is typically 10ppm/°C. An external refer-

ence can be used in situations where multiple ADS7870s

share a common reference.

The serial interface allows the use of SPI™, QSPI™,

Microwire™, and 8051-family protocols, without glue

logic.

NOTE: (1) Patent Pending.

VREF BUFIN BUFOUT/REFIN

ADS7870

Analog

Inputs

8 Ch

(4 Ch Diff.)

MUX

I/O 0

I/O 1

I/O 2

I/O 3

Digital

I/O

REF

PGA

BUF Clock

Divider

Oscillator

12-Bit

A/D

Registers

and

Control

Serial

Interface

CCLK

OSC ENABLE

BUSY

CONVERT

RESET

RISE/FALL

CS

SCLK

DIN

DOUT

International Airport Industrial Park • Mailing Address: PO Box 11400, Tucson, AZ 85734 • Street Address: 6730 S. Tucson Blvd., Tucson, AZ 85706 • Tel: (520) 746-1111

Twx: 910-952-1111 • Internet: http://www.burr-brown.com/ • Cable: BBRCORP • Telex: 066-6491 • FAX: (520) 889-1510 • Immediate Product Info: (800) 548-6132

©1999 Burr-Brown Corporation

PDS-11539A

PArintDedSin 7U.8S.A7.0December, 1999

®

1 page

PIN ASSIGNMENTS

PIN #

NAME

1 LN 0

2 LN 1

3 LN 2

4 LN 3

5 LN 4

6 LN 5

7 LN 6

8 LN 7

9 RESET

10 RISE/FALL

11 I/O 0

12 I/O 1

13 I/O 2

14 I/O 3

15 NC

16 CONVERT

17 BUSY

18 OSC ENABLE

19 CCLK

I/O

Analog Input

Analog Input

Analog Input

Analog Input

Analog Input

Analog Input

Analog Input

Analog Input

Digital Input

Digital Input

Digital Input/Output

Digital Input/Output

Digital Input/Output

Digital Input/Output

No Connection

Digital Input

Digital Output

Digital Input

Digital Input/Output

20 SCLK

Digital Input

21 DIN

Digital Input

22 DOUT

Digital Output

23 CS

Digital Input

24 VDD

25 GND

Power

Power

26 VREF

Analog Output

27 BUFIN

Analog Input

28 BUFOUT/REFIN Analog Output/Input

DESCRIPTION

MUX Input Line 0

MUX Input Line 1

MUX Input Line 2

MUX Input Line 3

MUX Input Line 4

MUX Input Line 5

MUX Input Line 6

MUX Input Line 7

Master Reset zero’s all registers.

Sets the active edge for SCLK. “0” sets SCLK active on falling edge. “1” sets SCLK active on rising edge.

Digital Input or Output signal

Digital Input or Output signal

Digital Input or Output signal

Digital Input or Output signal

Do not connect to this pin.

“0” to “1” transition starts a conversion cycle.

“1” indicates converter is busy

“0” sets CCLK as input, “1” sets CCLK as output and turns oscillator on.

If OSC ENABLE = “1” then Internal Oscillator is output to this pin. If OSC ENABLE = “0” then this is

the input pin for an external conversion clock.

Serial Data Input/Output Transfer Clock. Active edge set by the RISE/FALL pin. If RISE/FALL is low,

SCLK is active on the falling edge.

Serial Data Input. In the 3-wire mode, this pin is used for serial data input. In the 2-wire mode serial

data, output appears on this pin as well as the DOUT pin.

Serial Data Output. This pin is driven when CS is low and is high impedance when CS is high. This

pin behaves the same in both 3-wire and 2-wire modes.

Chip Select. When CS is low the serial interface is enabled. When CS is high the serial interface is

disabled, the DOUT pin is high impedance, and the DIN pin is an input. The CS pin only effects the

operation of the serial interface. It does not directly enable/disable the operation of the signal

conversion process.

Power Supply Voltage, +2.7V to +5.5V.

Power Supply Ground.

2.048V/2.5V On-Chip Voltage Reference

Input to Reference Buffer Amplifier

Output from Reference Buffer Amplifier and Reference Input to ADC.

®

5 ADS7870

5 Page

The ADS7870 is controlled by commands written to the

serial interface as shown in Table I. This eight-bit word

defines either the direct mode or register mode (see operat-

ing mode text).

Communication through the serial interface is dependent on

the micro-controller providing an instruction byte followed

by either additional data (for a write operation) or additional

clocks to allow the ADS7870 to provide data (for a read

operation). Special operating modes for reducing the in-

struction byte overhead for retrieving conversion results are

provided.

Reset of device (RESET), start of conversion (CONVERT),

and oscillator enable (OSC ENABLE) can be done by

signals to external pins or entries to internal registers. The

actual execution of each of these commands is a logical OR

function; either pin or register signal TRUE cause the

function to execute. The CONVERT pin signal is an edge-

triggered event, with a hold time of two DCLK periods for

de-bounce.

OPERATING MODES

The ADS7870 serial interface operates based on an instruc-

tion byte followed by an action commanded by the contents

of that instruction. The 8-bit instruction word is clocked into

the DIN input. There are two types of instruction bytes that

may be written to the ADS7870 as determined by Bit D7 of

the instruction word (see Table I). These two instructions

represent two different operating modes. In direct mode (Bit

D7 = 1), a conversion is started. A register mode (Bit D7 =

0) instruction is followed by a Read or Write Operation to

the specified register.

Direct Mode

In the direct mode a conversion is initiated by writing a

single 8-bit instruction byte to the ADS7870 (Bit D7 is set

to “1”). Writing the direct mode command sets the configu-

ration of the multiplexer, selects the gain of the PGA, and

starts a conversion cycle. After the last bit of the instruction

byte is received, the ADS7870 performs a conversion on the

selected input channel with the PGA gain set as indicated in

the instruction byte.

The conversion cycle will begin on the second falling edge

of CCLK after the eighth active edge of SCLK of the

instruction byte. When the conversion is complete the con-

version result will be stored in the A/D Output registers and

is available to be clocked out of the serial interface by the

controlling device using the READ operation in the Register

Mode.

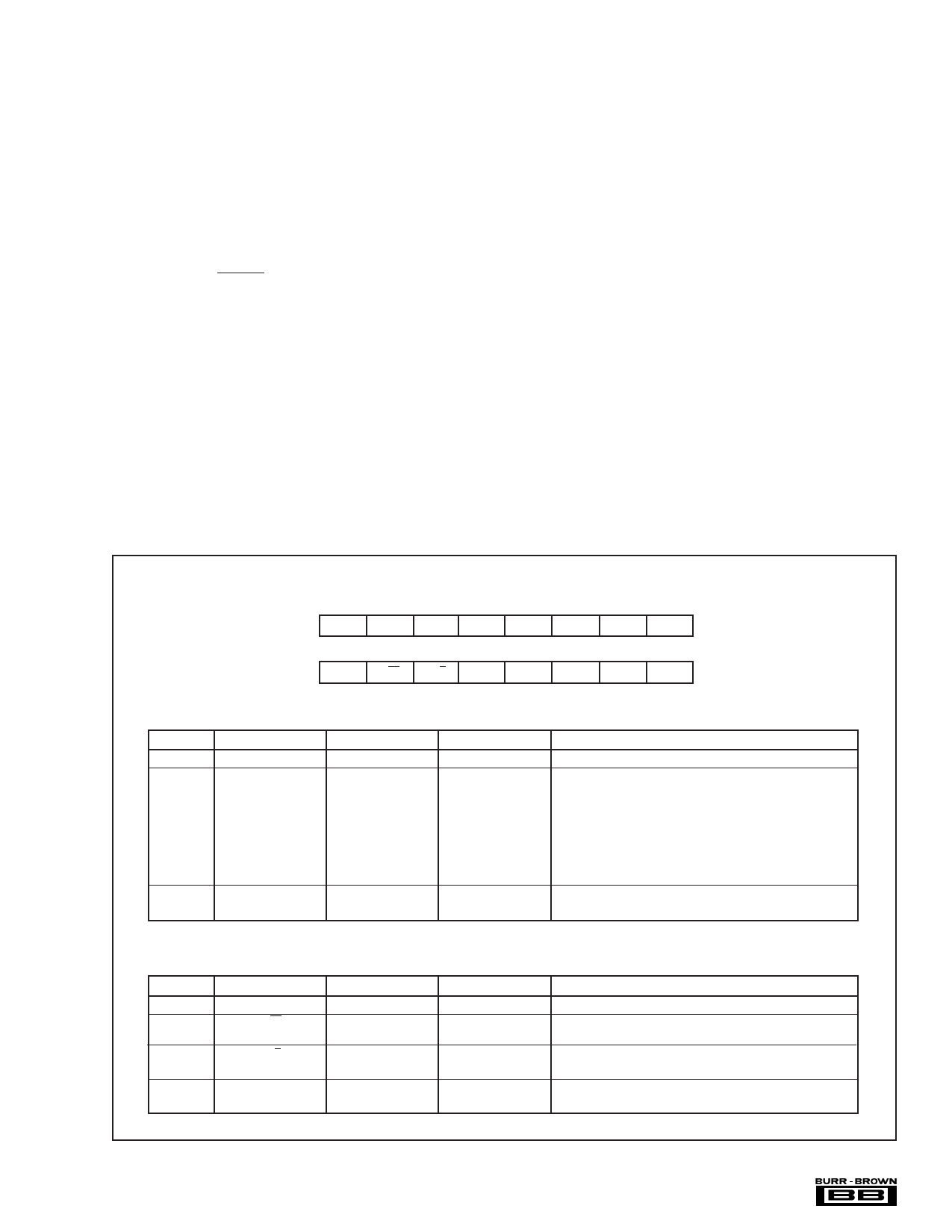

INSTRUCTION BYTE

D7 (MSB) D6 D5 D4 D3 D2 D1 D0

Start Conversion 1 G2 G1 G0 M3 M2 M1 M0

(Direct Mode)

OR

Read/Write

(Register Mode)

0 R/W 16/8 AS4 AS3 AS2 AS1 AS0

START CONVERSION INSTRUCTION BYTE (Direct Mode)(1)

BIT SYMBOL

NAME

VALUE

FUNCTION

D7

Mode Select

1 Starts a Conversion Cycle (Direct Mode)

D6-D4

G2-G0

PGA Gain Select

000 PGA Gain = 1 (power up default condition)

001 PGA Gain = 2

010 PGA Gain = 4

011 PGA Gain = 5

100 PGA Gain = 8

101 PGA Gain = 10

110 PGA Gain = 16

111 PGA Gain = 20

D3-D0

M3-M0

Input Channel Select

See

Table III

Determines input channel selection for the requested

conversion, differential or single-ended configuration.

NOTE: (1) The seven lower bits of this byte are also written to register 4, the Gain/Mux register.

READ / WRITE INSTRUCTION BYTE (Register Mode)

BIT SYMBOL

NAME

D7 Mode Select

D6

R/W

Read/Write Select

D5

16/8

Word Length

D4-D0

AS4-AS0

Register Address

VALUE

0

0

1

0

1

See

Table II

FUNCTION

Initiates a read or write operation (Register Mode)

Write Operation

Read Operation

8-Bit Word

16-Bit Word (2 eight-bit bytes)

Determines the address of the register that is

to be read from or written to.

TABLE I. Instruction Byte Addressing.

11

ADS7870

®

11 Page | ||

| Páginas | Total 27 Páginas | |

| PDF Descargar | [ Datasheet ADS7870.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ADS7870 | 12-Bit ADC/ MUX/ PGA and Internal Reference DATA ACQUISITION SYSTEM | Burr-Brown Corporation |

| ADS7870 | 12-Bit ADC MUX PGA and Internal Reference Data Acquisition System (Rev. C) | Texas Instruments |

| ADS7870EA | 12-Bit ADC/ MUX/ PGA and Internal Reference DATA ACQUISITION SYSTEM | Burr-Brown Corporation |

| ADS7871 | ADS7871: 14-Bit A/D Converter MUX PGA Internal Reference DAQ System (Rev. C) | Texas Instruments |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |