|

|

PDF ATtiny25 Data sheet ( Hoja de datos )

| Número de pieza | ATtiny25 | |

| Descripción | (Automotive) Atmel 8-bit AVR Microcontroller | |

| Fabricantes | ATMEL Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ATtiny25 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

ATtiny25/45/85 Automotive

8-bit AVR Microcontroller with 2/4/8K Bytes In-System

Programmable Flash

DATASHEET

Features

● High performance, low power AVR® 8-bit microcontroller

● Advanced RISC architecture

● 120 powerful instructions – most single clock cycle execution

● 32 × 8 general purpose working registers

● Fully static operation

● Non-volatile program and data memories

● 2/4/8Kbyte of in-system programmable program memory flash (ATtiny25/45/85)

● Endurance: 10,000 write/erase cycles

● 128/256/512 bytes in-system programmable EEPROM (Atmel® ATtiny25/45/85)

● Endurance: 100,000 write/erase cycles

● 128/256/512 bytes internal SRAM (ATtiny25/45/85)

● Programming lock for self-programming flash program and EEPROM data

security

● Peripheral features

● 8-bit Timer/Counter with prescaler and Two PWM channels

● 8-bit high speed Timer/Counter with separate prescaler

● 2 High frequency PWM outputs with separate output compare registers

● Programmable dead time generator

● Universal serial interface with start condition detector

● 10-bit ADC

● 4 Single ended channels

● 2 Differential ADC channel pairs with programmable gain (1x, 20x)

● Programmable watchdog timer with separate on-chip oscillator

● On-chip analog comparator

● Special microcontroller features

● debugWIRE on-chip debug system

● In-system programmable via SPI port

● External and internal interrupt sources

● Low power idle, ADC noise reduction, and power-down modes

● Enhanced power-on reset circuit

● Programmable brown-out detection circuit

● Internal calibrated oscillator

7598J-AVR-12/14

1 page

2. About Code Examples

This documentation contains simple code examples that briefly show how to use various parts of the device. These code

examples assume that the part specific header file is included before compilation. Be aware that not all C compiler vendors

include bit definitions in the header files and interrupt handling in C is compiler dependent. Please confirm with the C

compiler documentation for more details.

3. AVR CPU Core

3.1 Introduction

This section discusses the AVR® core architecture in general. The main function of the CPU core is to ensure correct

program execution. The CPU must therefore be able to access memories, perform calculations, control peripherals, and

handle interrupts.

3.2 Architectural Overview

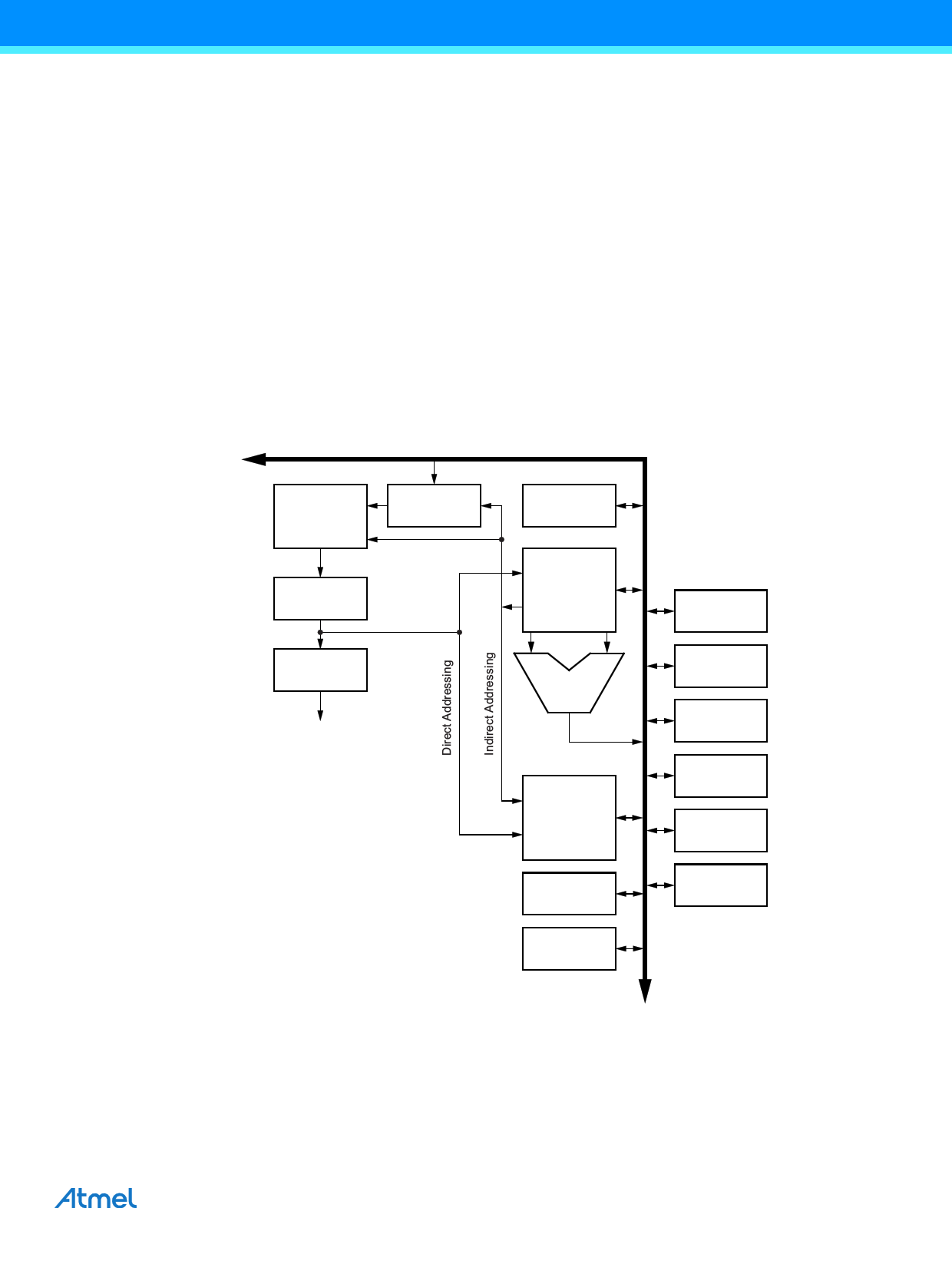

Figure 3-1. Block Diagram of the AVR Architecture

Data Bus 8-bit

Flash

Program

Memory

Instruction

Register

Instruction

Decoder

Control Lines

Program

Counter

Status and

Control

32 x 8

General

Purpose

Registers

ALU

Data

SRAM

Interrupt

Unit

Watchdog

Timer

Analog

Comparator

I/O Module 1

I/O Module 2

EEPROM

I/O Module n

I/O Lines

ATtiny25/45/85 Automotive [DATASHEET]

7598J–AVR–12/14

5

5 Page

Assembly Code Example

in r16, SREG ; store SREG value

cli ; disable interrupts during timed sequence

sbi EECR, EEMWE ; start EEPROM write

sbi EECR, EEWE

out SREG, r16 ; restore SREG value (I-bit)

C Code Example

char cSREG;

cSREG = SREG;

/* store SREG value */

/* disable interrupts during timed sequence */

_CLI();

EECR |= (1<<EEMWE); /* start EEPROM write */

EECR |= (1<<EEWE);

SREG = cSREG; /* restore SREG value (I-bit) */

When using the SEI instruction to enable interrupts, the instruction following SEI will be executed before any pending

interrupts, as shown in this example.

Assembly Code Example

sei ; set Global Interrupt Enable

sleep ; enter sleep, waiting for interrupt

; note: will enter sleep before any pending

; interrupt(s)

C Code Example

_SEI(); /* set Global Interrupt Enable */

_SLEEP(); /* enter sleep, waiting for interrupt */

/* note: will enter sleep before any pending interrupt(s) */

3.8.1

Interrupt Response Time

The interrupt execution response for all the enabled AVR® interrupts is four clock cycles minimum. After four clock cycles the

program vector address for the actual interrupt handling routine is executed. During this four clock cycle period, the program

counter is pushed onto the stack. The vector is normally a jump to the interrupt routine, and this jump takes three clock

cycles. If an interrupt occurs during execution of a multi-cycle instruction, this instruction is completed before the interrupt is

served. If an interrupt occurs when the MCU is in sleep mode, the interrupt execution response time is increased by four

clock cycles. This increase comes in addition to the start-up time from the selected sleep mode.

A return from an interrupt handling routine takes four clock cycles. During these four clock cycles, the program counter (two

bytes) is popped back from the stack, the stack pointer is incremented by two, and the I-bit in SREG is set.

ATtiny25/45/85 Automotive [DATASHEET]

7598J–AVR–12/14

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet ATtiny25.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ATTINY20 | 8-bit AVR Microcontroller | ATMEL Corporation |

| ATTINY22L | 8-bit Microcontroller with 2K Bytes of In-System Programmable Flash | ATMEL Corporation |

| ATTINY2313 | 8-bit AVR Microcontroller with 2K Bytes In-System Programmable Flash | ATMEL Corporation |

| ATTINY2313 | 8-bit AVR Microcontroller with 2K Bytes In-System Programmable Flash | ATMEL Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |