|

|

PDF ADuM210N Data sheet ( Hoja de datos )

| Número de pieza | ADuM210N | |

| Descripción | Single-Channel Digital Isolator | |

| Fabricantes | Analog Devices | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ADuM210N (archivo pdf) en la parte inferior de esta página. Total 16 Páginas | ||

|

No Preview Available !

Data Sheet

5.0 kV rms, Single-Channel Digital Isolator

ADuM210N

FEATURES

High common-mode transient immunity: 100 kV/μs

High robustness to radiated and conducted noise

Low propagation delay

13 ns maximum for 5 V operation

15 ns maximum for 1.8 V operation

150 Mbps maximum data rate

Safety and regulatory approvals (pending)

UL recognition

5000 V rms for 1 minute per UL 1577

CSA Component Acceptance Notice 5A

VDE certificate of conformity

DIN V VDE V 0884-10 (VDE V 0884-10):2006-12

VIORM = 849 V peak

CQC Certification per GB4943.1-2011

Low dynamic power consumption

1.8 V to 5 V level translation

High temperature operation: 125°C maximum

Fail-safe high or low options

8-lead, RoHS-compliant, SOIC_IC package

APPLICATIONS

General-purpose single-channel isolation

Industrial field bus isolation

GENERAL DESCRIPTION

The ADuM210N1 is a single-channel digital isolator based on

Analog Devices, Inc., iCoupler® technology. Combining high

speed, complementary metal-oxide semiconductor (CMOS)

and monolithic air core transformer technology, this isolation

component provides outstanding performance characteristics,

superior to alternatives such as optocoupler devices and other

integrated couplers. The maximum propagation delay is 13 ns

with a pulse width distortion of less than 3 ns at 5 V operation.

The ADuM210N supports data rates as high as 150 Mbps with a

withstand voltage rating of 5.0 kV rms (see the Ordering Guide).

The device operates with the supply voltage on either side ranging

from 1.8 V to 5 V, providing compatibility with lower voltage

systems as well as enabling voltage translation functionality

across the isolation barrier.

Unlike other optocoupler alternatives, dc correctness is ensured

in the absence of input logic transitions. Two different fail-safe

options are available, in which the outputs transition to a pre-

determined state when the input power supply is not applied or

the inputs are disabled.

VDD1 1

VI 2

(DATA IN)

VDD1 3

GND1 4

FUNCTIONAL BLOCK DIAGRAM

ED

NE

CC

OO

DD

EE

8 VDD2

7 GND2

6 VO

(DATA OUT)

ADuM210N

Figure 1.

5 GND2

1 Protected by U.S. Patents 5,952,849; 6,873,065; 6,903,578; and 7,075,329. Other patents are pending.

Rev. 0

Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarksandregisteredtrademarksarethepropertyoftheirrespectiveowners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

©2016 Analog Devices, Inc. All rights reserved.

Technical Support

www.analog.com

1 page

ADuM210N

Data Sheet

Table 2. Total Supply Current vs. Data Throughput—5 V Operation

1 Mbps

Parameter

Symbol

Min Typ Max

SUPPLY CURRENT

Supply Current Side 1

IDD1

2.2 3.7

Supply Current Side 2

IDD2

1.1 1.6

Min

25 Mbps

Typ Max

2.5 3.9

1.6 2.3

100 Mbps

Min Typ Max

3.6 4.9

3.1 4.6

Unit

mA

mA

ELECTRICAL CHARACTERISTICS—3.3 V OPERATION

All typical specifications are at TA = 25°C, VDD1 = VDD2 = 3.3 V. Minimum/maximum specifications apply over the entire recommended

operation range: 3.0 V ≤ VDD1 ≤ 3.6 V, 3.0 V ≤ VDD2 ≤ 3.6 V, and −40°C ≤ TA ≤ +125°C, unless otherwise noted. Switching specifications

are tested with CL = 15 pF and CMOS signal levels, unless otherwise noted. Supply currents are specified with 50% duty cycle signals.

Table 3.

Parameter

SWITCHING SPECIFICATIONS

Pulse Width

Data Rate

Propagation Delay

Pulse Width Distortion

Change vs. Temperature

Propagation Delay Skew

Jitter

DC SPECIFICATIONS

Input Threshold

Logic High

Logic Low

Output Voltage

Logic High

Logic Low

Input Current per Channel

Quiescent Supply Current

Dynamic Supply Current

Dynamic Input

Dynamic Output

Undervoltage Lockout

Positive VDDx Threshold

Negative VDDx Threshold

VDDx Hysteresis

AC SPECIFICATIONS

Output Rise/Fall Time

Common-Mode Transient Immunity2

Symbol

PW

tPHL, tPLH

PWD

tPSK

VIH

VIL

VOH

VOL

II

IDD1 (Q)

IDD2 (Q)

IDD1 (Q)

IDD2 (Q)

IDDI (D)

IDDO (D)

UVLO

VDDxUV+

VDDxUV−

VDDxUVH

tR/tF

|CMH|

|CML|

Min

6.6

150

4.8

0.7 × VDD1

VDD2 − 0.1

VDD2 − 0.4

−10

75

75

Typ Max

6.8 14

0.7 3

1.5

7.0

290

45

0.3 × VDD1

VDD2

VDD2 − 0.2

0.0

0.2

+0.01

0.8

0.9

3.6

0.9

0.1

0.4

+10

1.3

1.4

5.8

1.4

0.01

0.01

1.6

1.5

0.1

2.5

100

100

Unit

ns

Mbps

ns

ns

ps/°C

ns

ps p-p

ps rms

V

V

V

V

V

V

µA

mA

mA

mA

mA

mA/Mbps

mA/Mbps

V

V

V

ns

kV/µs

kV/µs

Test Conditions/Comments

Within PWD limit

Within PWD limit

50% input to 50% output

|tPLH − tPHL|

Between any two units at the same

temperature, voltage, and load

See the Jitter Measurement section

See the Jitter Measurement section

IO = −20 µA, VI = VIH

IO = −2 mA, VI = VIH

IO = 20 µA, VI = VIL

IO = 2 mA, VI = VIL

0 V ≤ VI ≤ VDD1

VI = 0 (N0), 1 (N1)1

VI = 0 (N0), 1 (N1)1

VI = 1 (N0), 0 (N1)1

VI = 1 (N0), 0 (N1)1

Inputs switching, 50% duty cycle

Inputs switching, 50% duty cycle

10% to 90%

VI = VDD1, VCM = 1000 V, transient

magnitude = 800 V

VI = 0 V, VCM = 1000 V, transient

magnitude = 800 V

1 N0 indicates the ADuM210N0 models and N1 indicates the ADuM210N1 models. See the Ordering Guide.

2 |CMH| is the maximum common-mode voltage slew rate that can be sustained while maintaining the voltage output (VO) > 0.8 × VDD2. |CML| is the maximum common-mode

voltage slew rate that can be sustained while maintaining VO > 0.8 V. The common-mode voltage slew rates apply to both rising and falling common-mode voltage edges.

Rev. 0 | Page 4 of 15

5 Page

ADuM210N

Data Sheet

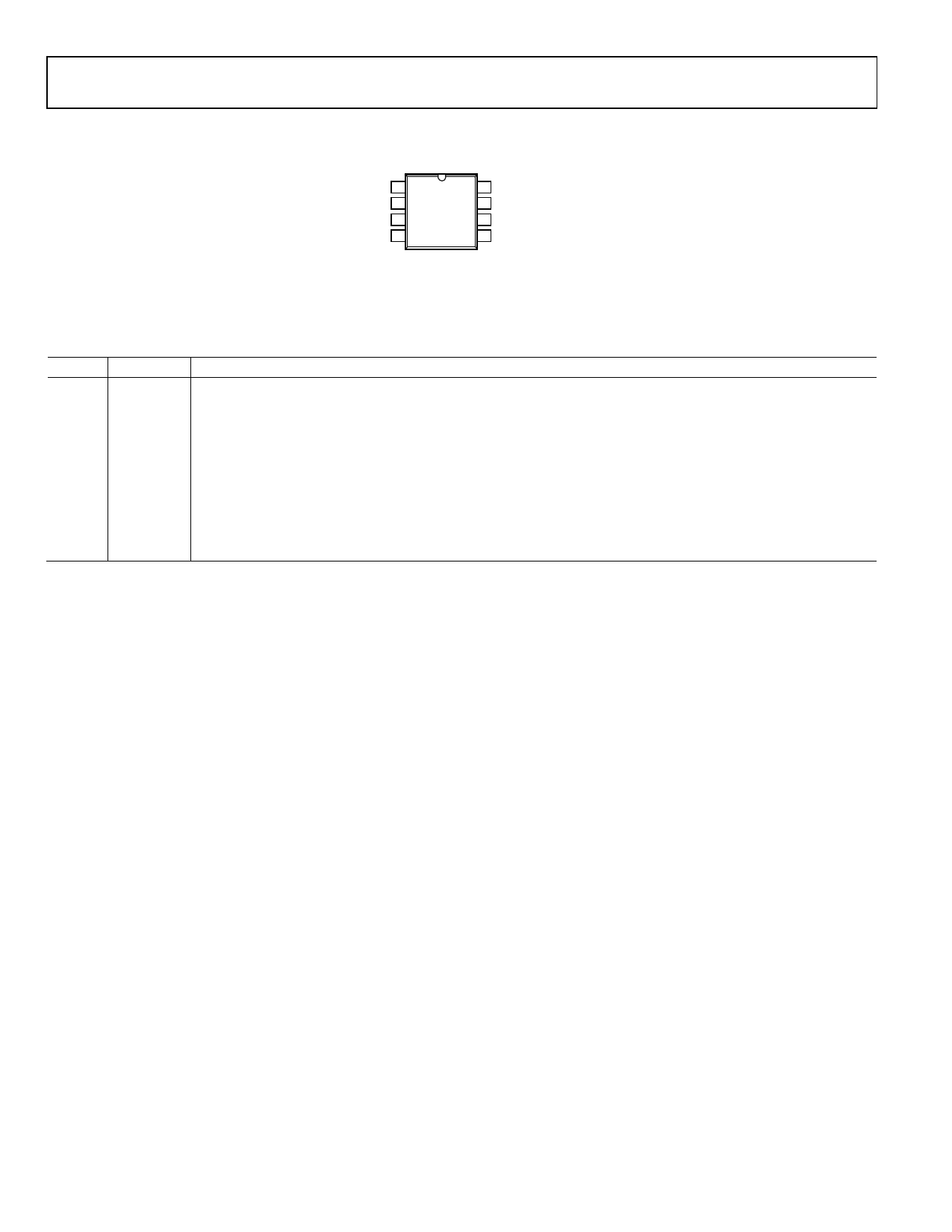

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

VDD11 1

8 VDD2

VI 2 ADuM210N 7 GND22

VDD11 3

TOP VIEW

(Not to Scale)

6 VO

GND1 4

5 GND22

1 PIN 1 AND PIN 3 ARE INTERNALLY CONNECTED. EITHER OR BOTH

MAY BE USED FOR VDD1.

2 PIN 5 AND PIN 7 ARE INTERNALLY CONNECTED. EITHER OR BOTH

MAY BE USED FOR GND2.

Figure 3. Pin Configuration

Table 17. Pin Function Descriptions1

Pin No. Mnemonic Description

1 VDD1

Supply Voltage for Isolator Side 1. Pin 1 and Pin 3 are internally connected. Either or both may be used for VDD1.

2 VI

Logic Input.

3 VDD1

Supply Voltage for Isolator Side 1. Pin 1 and Pin 3 are internally connected. Either or both may be used for VDD1.

4 GND1 Ground 1. Ground reference for Isolator Side 1.

5 GND2 Ground 2. Ground reference for Isolator Side 2. Pin 5 and Pin 7 are internally connected. Either or both may be used

for GND2.

6 VO

Logic Output.

7 GND2 Ground 2. Ground reference for Isolator Side 2. Pin 5 and Pin 7 are internally connected. Either or both may be used

for GND2

8 VDD2

Supply Voltage for Isolator Side 2.

1 Reference the AN-1109 Application Note for specific layout guidelines.

Rev. 0 | Page 10 of 15

11 Page | ||

| Páginas | Total 16 Páginas | |

| PDF Descargar | [ Datasheet ADuM210N.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ADuM210N | Single-Channel Digital Isolator | Analog Devices |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |